2. マイクロプロセッサの構造

2.1 マイクロプロセッサ開発の概要

2.1.1 開発の歴史

初代: 1971 年以降、4 ビット マイクロプロセッサとローエンドの 8 ビット マイクロプロセッサ

第2世代: 1973 年以来、8 ビット マイクロプロセッサ

第三世代: 1978 年以来、16 ビット マイクロプロセッサ

第四世代: 1981 年以来、32 ビット マイクロプロセッサ

2.2 マイクロプロセッサの機能構成

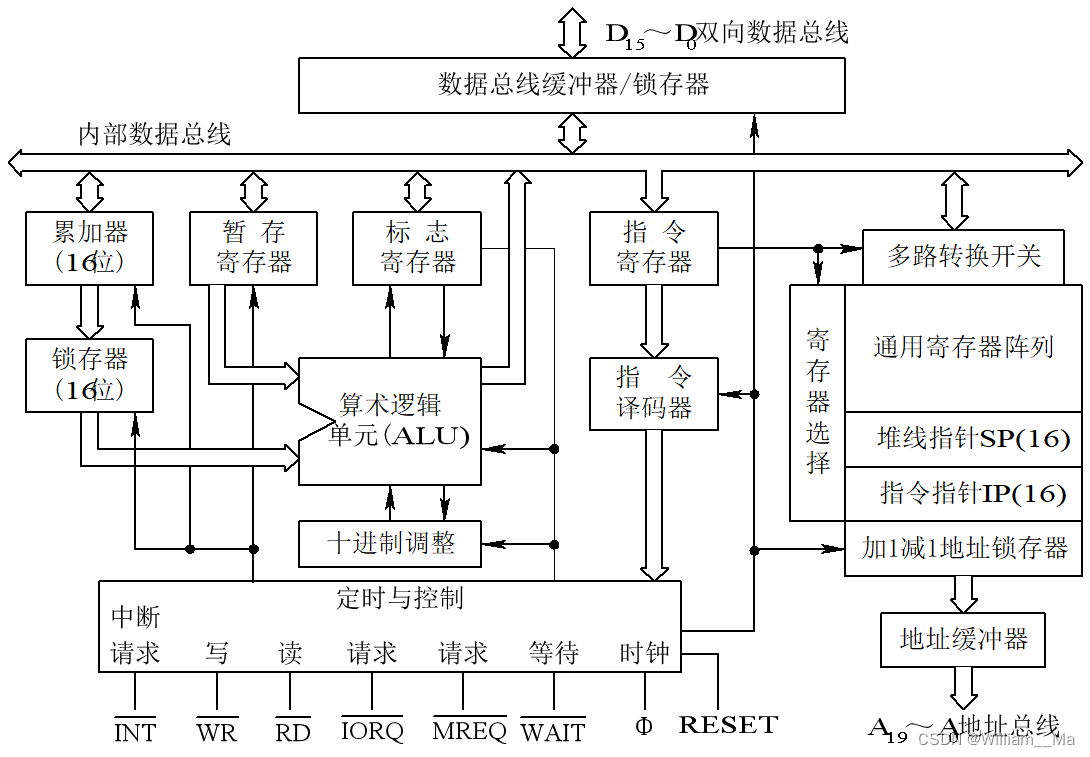

2.2.1 マイクロプロセッサの構造構成

① 算術演算装置:算術論理演算装置(ALU)を含みます。データに対して算術論理演算が実行され、演算結果の特性がフラグ レジスタに格納されます。

② コントローラ: 命令レジスタ、命令デコーダ、タイミングおよび制御回路を含みます。命令のデコード結果に応じて、あるタイミングでデコード信号を発行し、命令の実行を制御します。

③レジスタアレイ:汎用レジスタと特殊レジスタのセットを含みます。汎用レジスタ - 演算に関係するデータの一時記憶域、特殊レジスタ - 通常は命令ポインタ IP (またはプログラム カウンタ PC) およびスタック ポインタ SP。

3人のつながりは、

これら 3 つの部分間の情報交換は、バス アーキテクチャを通じて実現されます。

バス: コンポーネント間の情報伝達のためのアナウンス経路。ここでのバスを「内部バス」(または「オンチップバス」)と呼びます。ユーザーは内部バスの動作を直接制御できません。

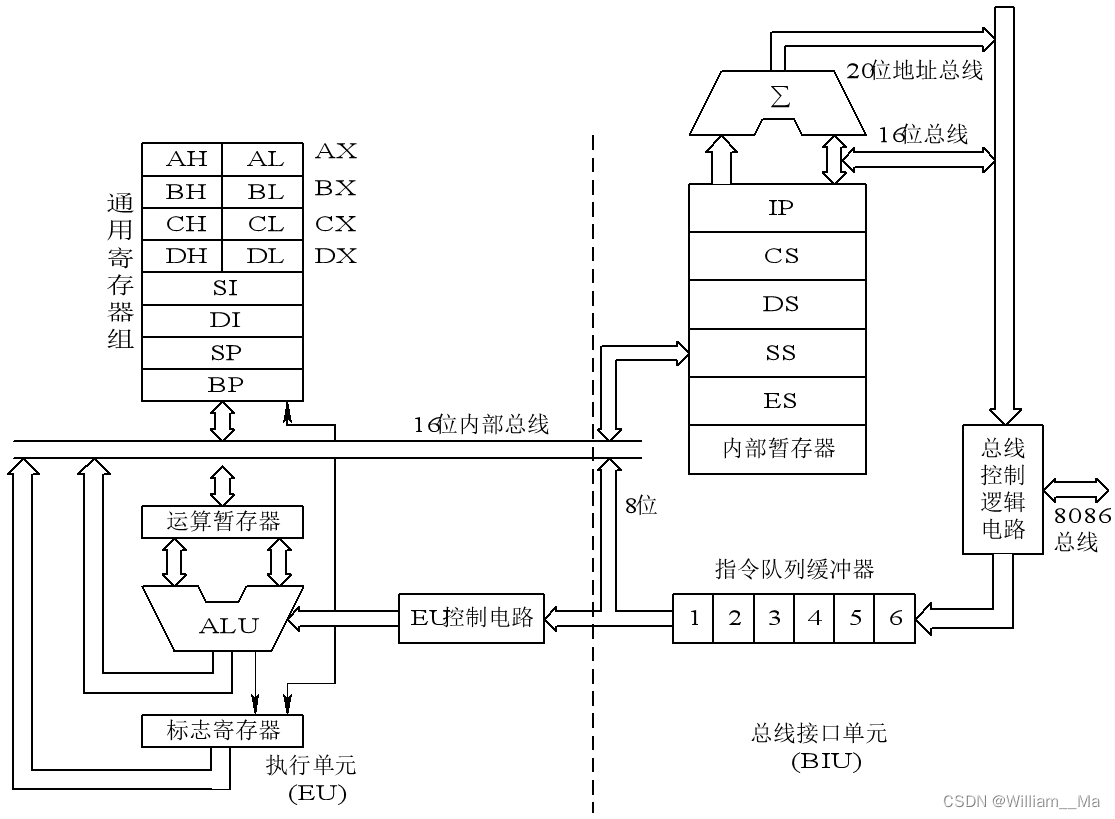

2.2.2 Inter 8086 マイクロプロセッサの機能構造

2.2.2.1 8086CPUの内部構造

バス インターフェイス ユニット (BIU):

メモリと I/O デバイス間のインターフェイス コンポーネントは、すべてのピンの動作を担当します。

16 ビット双方向データ バス、20 ビット アドレス バス、複数の制御バス

特定のタスク: メモリ ユニットから命令をフェッチし、一時記憶用の命令キュー バッファに送信する役割を果たします。

CPU が命令を実行するとき、バス ユニットは実行ユニットと連携して、指定されたメモリ ユニットまたは I/O ポートからデータをフェッチして実行ユニットに送信したり、実行ユニットの処理構造を指定のメモリ ユニットに転送したりする必要があります。またはI/Oインターフェース。

構成:20ビットアドレス加算器、4セグメントレジスタ、16ビット命令ポインタIP、命令キューバッファ、バス制御論理回路。

アドレス加算器: 16 ビット レジスタは 20 ビット アドレス アドレス指定を実装します。アドレス加算器は、関連するセグメント レジスタの内容 (セグメントの開始アドレス) を左に 4 ビットシフトし、それをオフセット アドレスに加算して次の値を形成します。 20ビットの物理アドレス。

16 ビット命令ポインタ IP: (命令ポインタ) これは、コード内で実行される次の命令のオフセット アドレスを格納するために使用され、CS と組み合わせて命令格納ユニットを指す物理アドレスを形成します。

命令バッファキュー: EU が命令を実行し、バスを占有する必要がない場合、BIU は自動的に命令をプリフェッチし、取得した命令を 6 バイトの命令キューレジスタに順番に格納します。先出し方式で、EU にフェッチされます。実行するために。

バス制御論理回路: 8086 CPU の内部バスを外部バスに接続することは、8086 CPU がメモリ ユニットまたは I/O ポートとデータを交換する唯一の方法です。

16 ビットのデータ バス、20 ビットのアドレス バス、およびいくつかの制御バスが含まれます。

実行単位 EU:

1つの16ビット演算ユニットALU、8つの16ビットレジスタ、1つの16ビットフラグレジスタFLAGS、1つのデータ一時記憶レジスタおよび実行ユニットの制御回路を含む

算術論理演算装置 (ALU): 16 ビットの算術演算装置で、8 ビットおよび 16 ビットのバイナリ算術演算および論理演算に使用でき、メモリのアドレス指定に必要な 16 ビット オフセットも計算できます。命令量のアドレッシングモード。

フラグ レジスタ (FLAGS): CPU 動作のステータス特性を反映し、特定の制御フラグを保存するために使用される 16 ビット レジスタです。

演算一時レジスタ: ALU が演算を完了するのを支援し、演算に参加するデータを一時的に保存します。

汎用レジスタセット: 4つの16ビットデータレジスタを含むAX、BX、CX、DXおよび 4 つの 16 ビット ポインタおよびインデックス レジスタSP、BPおよびSI、DI。

EU 制御回路: BIU の命令キュー バッファから命令をフェッチし、命令をデコードし、命令要件に従って EU の内部コンポーネントに制御コマンドを送信して、各命令で指定された機能を実行します。

EU の命令の実行は命令フェッチ オペコードから始まります。

演算演算の場合、演算データは演算一時レジスタを介して ALU に送信され、演算結果は ALU データバスを介して対応するレジスタに送信され、演算結果に応じてフラグ レジスタ FLAGS の状態が変化します。

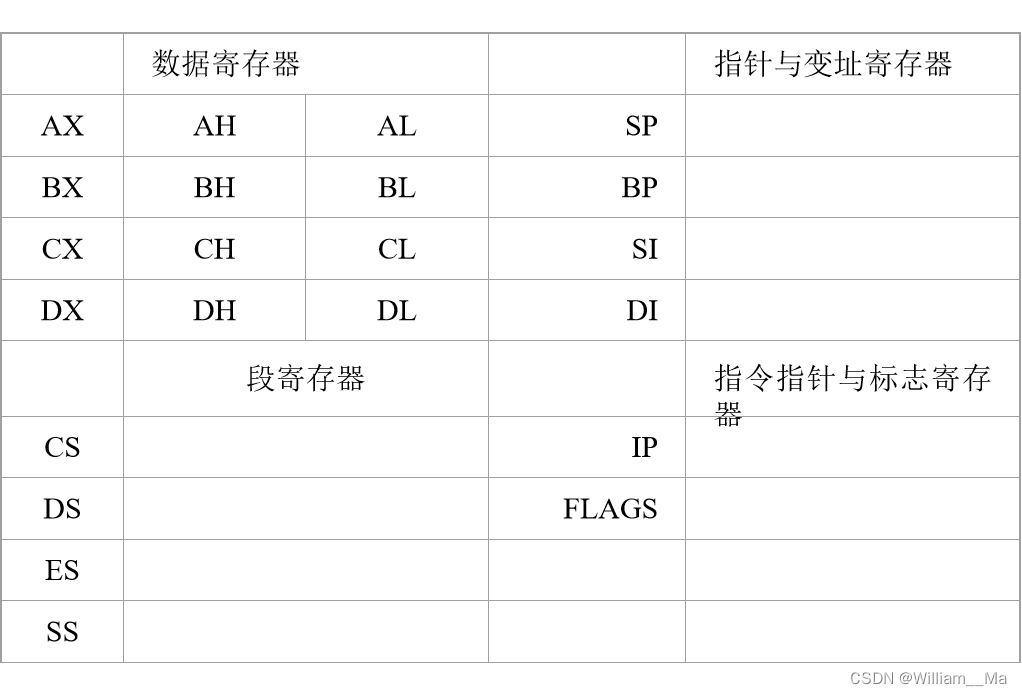

2.2.2.2 8086CPU 内部レジスタ

14個の16ビットレジスタを含む

汎用レジスタ

これはデータレジスタと呼ばれ、16 ビットデータレジスタまたは 2 つの 8 ビットデータレジスタとして使用できます。16ビットとして使用する場合はAX、BX、CX、DXと呼ばれます。8 ビットとして使用する場合、AH、BH、CH、DH は上位バイトを格納し、AL、BL、CL、DL は下位バイトを格納し、独立してアドレス指定できます。

セグメントレジスタ

物理アドレスの計算は BIU で実行され、まずセグメント アドレスを 4 ビット左にシフトし、次にそれを 16 ビットのオフセット値に加算します。

セグメントレジスタは4つ(CS、DS、SS、ES)あります。

CS (コード セグメント レジスタ):現在使用されている命令コードは、セグメント レジスタによって指定されたメモリ セグメントから取得でき、対応するオフセット値は IP によって提供されます。

SS (スタック セグメント レジスタ):現在のスタックの開始アドレスを指定します。

DS (Data Segment Register):現在のプログラムで使用されるデータが格納されているセグメントの開始アドレスを示します。

ES (追加セグメント レジスタ):現在のプログラムで使用される追加セグメント アドレスの開始位置を示します。通常、元のデータや演算結果を格納するために使用されます。

アドレスポインタとインデックスレジスタ

アドレス ポインタとインデックス レジスタはどちらも 16 ビット レジスタで、通常はアドレスのオフセット (つまり、セグメントの開始アドレスからの相対的な距離) を格納するために使用されます。

スタック ポインタ SP は、スタック セグメント内のスタックの現在の先頭のアドレスを指すために使用されます。プッシュ (PUSH) 命令とポップ (POP) 命令には、SPによってスタックの先頭のオフセット アドレスが与えられます。

ベースアドレスポインタBPは、スタックセグメント内の処理対象データのベースアドレスを指すため、ベースアドレスポインタレジスタと呼ばれます。

インデックス レジスタ SI および DI は、現在のデータ セグメント内の特定のユニットのオフセットを格納するために使用されます。

命令ポインタとフラグレジスタ

通常の動作中、命令ポインタ IPには、BIU によってフェッチされる次の命令のオフセット アドレスが格納されます。

命令フェッチ操作が実行されるたびに、次にフェッチされるメモリユニットを指すように自動的に 1 を加算し、バイトがフェッチされるたびに IP の内容が 1 ずつインクリメントされ、IP の内容が 1 ずつ増加します。単語を取得した後、IP はコンテンツに 2 を追加します。

フラグレジスタ FLAGS は16 ビットのレジスタで、8086 では有効ビットを合計 9 ビット使用します。6 ビットはステータス フラグ ビット、3 ビットは制御フラグ ビットです。

6つのステータスフラグ

CF(キャリーフラグ)- キャリーフラグビット。CF は、最上位ビットからキャリー (またはボロー) を生成するために加算 (または減算) 演算が実行される場合は 1、それ以外の場合は 0 です。

PF (パリティ フラグ) - パリティ フラグ。このフラグは、演算結果の 1 の数が偶数か奇数かを反映します。命令実行結果の下位 8 ビットに 1 が偶数個含まれる場合は PF=1、それ以外の場合は PF=0。

AF(補助キャリーフラグ) ——補助キャリーフラグ。結果の下位 4 ビットが上位 4 ビットへのキャリー (またはボロー) を持つように加算 (または減算) 演算を実行する場合、AF=1、それ以外の場合、AF=0。

ZF(ゼロフラッグ)- ゼロフラグ。現在の演算結果がゼロの場合は ZF=1、それ以外の場合は ZF=0。

SF(Sign Flag) —— 符号フラグビット。演算結果の最上位ビットと同じです。

OF(オーバーフローフラグ)- オーバーフローフラグ。補数演算でオーバーフローが発生した場合は OF=1、オーバーフローが発生した場合は OF=0 となります。

3つの制御フラグビット

DF(方向フラグ) ——方向フラグビット。文字列処理の方向を指定するために使用され、このビットが "1" の場合、文字列は降順、つまりアドレスの上位から下位に向かって処理されます。それ以外の場合は、昇順で処理されます。

IF(割り込みイネーブルフラグ) ——割り込みイネーブルフラグビット。これは、8086 が外部割り込み要求を受信できるかどうかを制御するために使用されます。IF=1 の場合、8086 は外部割り込みに応答できますが、それ以外の場合は外部割り込みに応答しません。

IF の状態は、ノンマスカブル割り込み要求 (NMI) および CPU 内部割り込み要求には影響しません。

TF(トラップ フラグ) - トレース フラグ。プログラムのデバッグ用に設定されるトラップ制御ビットです。このビットが "1" の場合、8086 CPU はシングルステップ状態となり、CPU は命令を実行するたびに自動的に内部割り込みを発生します。このビットがリセットされると、CPU は通常の動作を再開します。

2.2.2.3 8086CPUのメモリとメモリポート

8086 CPU がアドレス指定できる1MBこの記憶空間の記憶単位はバイトオーダーとして8ビットでソートされて記憶されます。

各バイトは、アドレス範囲が 0 ~ 220-1 の符号なし整数である一意のアドレス コードによって識別されますが、表現するには 16 進数を使用するのが一般的です。00000H~FFFFFH。

メモリ空間をバイトアドレス番号の順に並べる方法を == 「バイトアドレッシング」 == と呼びます。

ワードの上位 8 ビット バイトは上位アドレス ユニットに格納され、ワードの下位 8 ビット バイトは下位アドレス ユニットに格納されると規定されています。

下位バイトのアドレスがこのワードのアドレスとして使用されます。

ワードデータは必ず偶数アドレス、つまり偶数アドレスが下位バイト、奇数アドレスが上位バイトに位置し、この規則に従って格納されたワードデータを「レギュラーワード」と呼びます。

メモリの分割構造と物理アドレスの形成

1 MB の記憶空間はいくつかの論理セグメントに分割され、現在の 4 つの論理セグメントのベース アドレスは CPU 内の 4 つのセグメント レジスタ、つまりコード セグメント レジスタ CS、データ セグメント レジスタ DS、スタック セグメント レジスタに設定されます。 SS および追加セグメント Register ES。

論理アドレスとは、プログラムが使用するアドレスです。

物理アドレスとは、CPUやメモリがデータのやり取りに実際に使用するアドレスのことです。2 つの部分で構成されます。セグメントベースアドレス(セグメント開始アドレス上位16ビット)とオフセットアドレス。

前者はセグメント レジスタによって与えられ、後者は記憶ユニットの位置とセグメントの開始アドレスの間のオフセット距離を指します。CPU がストレージ ユニットをアドレス指定する場合、まずセグメント レジスタの内容を 4 ビット左にシフトし、次に命令で指定された 16 ビットのオフセット アドレスを追加して 20 ビットの物理アドレスを形成します。

命令をフェッチするとき、CPU はコードセグメントレジスタ CS を自動的に選択します。、左に 4 ビットシフトした後、命令によって提供される 16 ビットのオフセット アドレスを加算して、フェッチされる命令の物理アドレスを計算します。

スタック動作中、CPU はスタックセグメントレジスタ SS を自動的に選択します。、その内容を 4 ビット左にシフトし、命令によって提供される 16 ビットのオフセット アドレスを加算し、スタック トップ ユニットの物理アドレスを計算します。

オペランドがアクセスされるたびに、CPU はデータ セグメント レジスタ (または追加のセグメント レジスタ ES) を自動的に選択します。、セグメントのベース値を 4 ビット左にシフトし、16 ビットのオフセット アドレスを追加して、メモリ内のオペランドの物理アドレスを取得します。

8086のI/Oポート

各 I/O インターフェイスには 1 つまたは複数のポートがあります。マイコンシステムでは、各ポートにアドレスが割り当てられており、これをポートアドレスといいます。

8086 CPU はアドレスバスを使用します下位16ビット8 ビット I/O ポートのアドレス指定ラインとして、8086 システムによってアクセスされる最大 == 65 536 (64 KB)== 8 ビット I/O ポートがあります。

データバスの負荷分散を容易にするために、上位8ビットと下位8ビットに接続されるデバイスの数は等しいことが好ましい。