wx Gong Zhonghao: Chuangxiang Diary

Dialogue Send: Music Circuit

完全な非透かし紙レポート (回路図を含む) を無料で入手

1. 設計タスクの要件

1. コース設計の課題

書かれた音楽を自動再生できる音楽演奏回路を設計する。実験ボックスのスピーカーから音楽を再生し、発光ダイオードを使用して音楽のビートを表示する必要があります。

(追加機能:この設計は、トピックに必要なすべての機能の実現に基づいて、多くの追加機能を追加します。すべての機能は、ここに宣言されている「工学設計の概要」で明確にされます。)

2. 設計解析

(1) 音楽ハードウェア再生回路の基本原理

ハードウェア回路の発音原理は、プログラムで FPGA の特定のピンを制御できる場合、音の周波数範囲は数十から数千 Hz 程度です。スピーカーに接続された特定の周波数の矩形波を出力するチップは、対応する周波数の音を発することができます。音楽の各音は特定の周波数に対応します. FPGA に異なる音を出力させたい場合は、対応する音の周波数を制御するだけで済みます。音楽はすべて一連の音符で構成されているため、音楽のスコアに従ってこれらの音符に対応する周波数を連続して出力するだけで、各音符のトーンをスピーカーで連続的に送信できます。音楽を正確に再生するには、ラウドスピーカーで再生できるようにするだけでは十分ではなく、音楽のリズムを正確に制御する必要があります。つまり、音楽の各音の周波数と持続時間が 2 つの鍵となります。音楽の連続演奏への要因。

(2) 音符周波数の取得 ある

基準周波数を分周することにより、周波数の異なる複数の信号を得ることができます。各音の周波数はほとんどの場合非整数であり、分周係数は小数にならないため、コンピュータで得られた分周係数は整数に丸める必要があります。基準周波数が低すぎると、分周係数が小さすぎて丸め誤差が大きくなります。基準周波数が高すぎると、周波数の相対誤差は小さくなりますが、分周構造が大きくなります。実際には、これら 2 つの要因を総合的に考慮し、誤差を最小限に抑えることを前提として、適切な基準周波数を選択する必要があります。この設計では 1MHz の基準周波数を選択します。デジタル分周器は12ビットのバイナリーカウンターを採用し、音楽の休符は分周係数が0、つまり初期値=4095に設定されている限り、この時スピーカーは鳴りません。

分周係数から数値制御分周器の初期値を求めることができる。(もはや言葉では原理を説明することはできず、プログラムはこの問題を説明することができます。初期値の説明については、以下のプログラムを参照してください。) 初期値の計算式は次のとおりです

。クロックソースとして12MHZを使用し、1MHZの周波数のパルスオーバーフロー信号を12分周して与え、1MHZのオーバーフロー信号を12ビットのバイナリコードでプリセット番号と周波数でカウントします。与えられたプリセット番号で変化するパルス信号。パルス信号にはブザーを駆動する能力がないため、このパルス信号の周波数を 2 分周してブザーを駆動し、最終的な出力信号の周波数とプリセット番号の関係は次のようになります。

(3) 音楽のリズムの制御

一般的な音楽の最小拍子は 1/4拍子であり、1拍の時間を 1 秒とすると、4Hz の 1/4拍子の長さを出力すればよい ( 0.25 秒) その他の占有時間の場合 より長い拍 (1/4 拍の整数倍である必要があります) の場合、対応する回数の音符を出力するだけで済みます。

カウントクロック信号は音符の速度を出力するための制御信号として使用され、クロックが速い場合は出力ビート速度が速く、再生速度も速く、クロックが遅い場合は出力ビート速度が遅くなります。となり、自然と再生速度が落ちていきますが、2周波プログラムを追加する必要があるので、カウンターのクロック信号を4Hzの2倍、つまり8Hzにする必要があります。

(4) 譜面の生成

LPM-ROM の譜面に音符データを格納する設計で、4 クロック拍分、つまり 1 秒間ロジック内に音が留まると、その音符が LPM-ROM に格納されます。 ROM 内の連続する 4 つのアドレスすべてが格納されます。4Hz のクロックが来ると、それに合わせて LPM-ROM からノートデータが出力されます。

(5) 選択モジュール 選択

モジュールは、4 桁の制御信号を使用して、楽譜モジュール データの選択性を制御しますが、vhdl 言語で記述するのは比較的簡単なので、ここでは詳しく説明しません。

(6) Decoder とその他のモジュール

Decoder とその他のモジュールは以前の実験で行われており、原理は比較的単純で理解しやすいので、ここでは詳しく説明しません。

3. エンジニアリング設計の概要

4Hzのクロックパルスが到来すると、楽譜生成モジュールは音符データを分周係数モジュールに出力し、分周係数モジュールは音符に対応する分周係数に必要な初期値を出力し、初期値はデジタル分周器モジュールに送信され、12MHzのクロックパルスが来ると、数値制御分周器は対応する周波数(つまり、音符に対応する周波数)を分周に従ってスピーカーに出力します係数, スピーカーは対応する音を発することができます. 音が来る. 連続する8Hzクロックパルスは、スコアジェネレータに保存されている音符データを1つずつ周波数分割係数モジュールに送信し、数値制御周波数分割モジュールを通過します.最後に、スピーカーが音符データを 1 つずつ送信すると、対応する音声が再生されます。曲もスムーズに再生されました。同時に、LED デジタル チューブは音楽とともに対応するスコアを表示し、3 桁の LED ライトが高、中、低の周波数に対応して点滅します。メロディーが一度再生されると、メロディージェネレーターが自動的に最初からループ再生を開始することができます. このとき、ディップスイッチを使用して再生する音楽を選択すると、ディップスイッチはセレクターに選択信号を与えます.対応する曲を選択します. データ変換モジュールは対応する曲を再生します. このプロジェクトでは4つの音楽が選択され、グレイコードの形式でコード化されています. DIPスイッチの1ビットのみが毎回変更されるため、選択に便利です. . (残りの完全な詳細については、ダウンロードを参照してください)

2. 全体フレーム図

プロジェクトはモジュールで構成されており、そのうちの 4 つは図に示すように楽譜保存モジュール用の ROM です。

1. 分周器の機能は、チップ上で提供される 50MHz のクロックを 12MHz と 8Hz のクロックに分周することであり、それぞれカウンタと分周ドライバ (NC 分周器) で使用されます。

2. カウンターはカウント機能を完了し、183 ベース (最長の歌菊テーブルには 183 文字あります) が各クロック エッジに 1 を追加します。

3. 4 つの音楽モジュールは、それぞれ 4 曲のスコアを記録します。前のモジュールのカウンタがカウントした数に従って、対応するアドレスのデータを読み出し、次のモジュールに渡します。

4. セレクターは、曲を選択する機能を完了します。

5. データ変換モジュールは、セレクターで選択されたソング ROM 内のアドレスのデータを、周波数ドライバー (数値制御分周器) の分周に必要な制御データ、3 つの LED ライト (高、中) のデータに変換します。および低音)、およびデコーダーに必要なデータ。

6. 分周ドライバは数値制御分周器でもあり、分周機能を完了してブザーを駆動します。

7. デコーダーは、LED デジタル管に楽譜データを表示します。

3. デバイスを選択する

詳細はダウンロードをご覧ください

4.機能モジュール

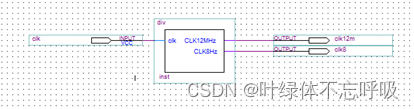

1. 分周器 (div) は、

チップ上で提供される 50MHz のクロックを 12MHz と 8Hz のクロックに分周し、それぞれカウンターと分周ドライバー (NC 分周器) で使用されます。

(1) モジュールのグラフィック:

(2) プログラムは次のとおりです。

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY div IS

PORT(

clk :IN STD_LOGIC;

CLK12MHz,CLK8Hz: OUT std_logic);

END div;

ARCHITECTURE one of div is

begin

nana:process(clk)

variable cnt:integer range 0 to 2;

variable tmp:std_logic;

begin

if(clk'event and clk='1')then

if cnt>=1 then

cnt:=0;

tmp:=not tmp;

else

cnt:=cnt+1;

end if;

end if;

CLK12MHz<=tmp;

end process nana;

nbnb:process(clk)

variable cnt:integer range 0 to 3125000;

variable tmp:std_logic;

begin

if(clk'event and clk='1')then

if cnt>=3124999 then

cnt:=0;

tmp:=not tmp;

else

cnt:=cnt+1;

end if;

end if;

CLK8Hz<=tmp;

end process nbnb;

end one;

(3) シミュレーション波形:

(4) シミュレーション波形解析

波形から、ckl は 50MHz の入力クロック信号、ckl12 は 12MHz の出力クロック信号、clk8 は 8Hz のクロック信号であることがわかります。紙では、すべての波形が印刷されません。

分析後、このモジュールの機能は完全に正しいです。

2. カウンター (notetabs)

(詳細はダウンロードを参照)

3. モジュールを選択 (選択)

(詳細はダウンロードを参照)

4. データ変換モジュール (tontaba)

セレクターで選択されたソング ROM のアドレスのデータを、周波数ドライバー (数値制御分周器) の分周に必要な制御データに変換し、3 つの LED ライト (ハイ、ミドル、バス) のデータと、デコーダが必要とするデータ。

(1) モジュールイメージ:

(2) プログラムは次のとおりです。

library ieee;

use ieee.std_logic_1164.all;

entity tonetaba is

port(index:in std_logic_vector (4 downto 0);

code:out std_logic_vector(3 downto 0);

high0:out std_logic_vector(2 downto 0);

tone:out std_logic_vector(11 downto 0))

;

end;

architecture one of tonetaba is

begin

search:process(index)

begin

case index is

when"00000"=>tone<="111111111111";code<="0000";high0<="000";--0/4095

when"00001"=>tone<="011100011111";code<="0001";high0<="001";--L1/1823

when"00010"=>tone<="100000001111";code<="0010";high0<="001";--L2/2063

when"00011"=>tone<="100011110010";code<="0011";high0<="001";--L3/2291

when"00100"=>tone<="100101010101";code<="0100";high0<="001";--L4/2390

when"00101"=>tone<="101000010000";code<="0101";high0<="001";--L5/2576

when"00110"=>tone<="101010111000";code<="0110";high0<="001";--L6/2745

when"00111"=>tone<="101101001011";code<="0111";high0<="001";--L7/2891

when"01000"=>tone<="101110001111";code<="0001";high0<="010";--M1/2960

when"01001"=>tone<="110000001001";code<="0010";high0<="010";--M2/3082

when"01010"=>tone<="110001111001";code<="0011";high0<="010";--M3/3193

when"01011"=>tone<="110010101100";code<="0100";high0<="010";--M4/3244

when"01100"=>tone<="110100001001";code<="0101";high0<="010";--M5/3337

when"01101"=>tone<="110101011100";code<="0110";high0<="010";--M6/3420

when"01110"=>tone<="110110100101";code<="0111";high0<="010";--M7/3494

when"01111"=>tone<="110111000111";code<="0001";high0<="100";--H1/3528

when"10000"=>tone<="111000000101";code<="0010";high0<="100";--H2/3589

when"10001"=>tone<="111000111100";code<="0011";high0<="100";--H3/3645

when"10010"=>tone<="111001010110";code<="0100";high0<="100";--H4/3670

when"10011"=>tone<="111010000100";code<="0101";high0<="100";--H5/3717

when"10100"=>tone<="111010101101";code<="0110";high0<="100";--H6/3758

when"10101"=>tone<="111011010010";code<="0111";high0<="100";--H7/3795

when others=>null;

end case;

end process;

end;

(3) シミュレーション波形:

(4) シミュレーション波形解析

由波形可看出,当输入信号index为00110时high0显示1,code显示6(即 中音6),预置初值为101010111000,查询上文所列的表,可发现功能完全正确。

第二个波形图,输入信号00010,输出为中音2,再查预置初值,同样可发现完全正确。因此该模块功能完全正确。

5. デコーダー モジュール (削除済み)

(詳細はダウンロードを参照)

6. デジタル分周器モジュール (speakera)

(詳細はダウンロードを参照)

7. 楽譜データROM(4モジュール)

(詳細はダウンロード参照)

8. アドレスラインの選択:

上記のモジュールに加えて, アドレスラインの選択も追加する必要があります. 実験用ボトムボックスのさまざまな機能が選択されています. この実験はLEDデジタルチューブを使用しているため, アドレスラインの割り当てvga は vga0 =0、vga1=1、vga2=0、vga3=0 です。以下に示すように:

9. led デジタル管の位置選択機能のソリューション:

このプロジェクトは 1 つの数字を表示するだけでよいので、デジタル管を選択できます. 実験ボックスのデジタル管は共通陽極デジタル管であるため、それはデジタルチューブを選択する必要があります 図に示すように、チューブは低レベルに割り当てることができます: (2、4、6、および 8 つのデジタルチューブを一緒に表示するために選択しました)

5. 全体設計回路図

1. 最上位設計の回路図

2. 最上位設計のシミュレーション結果

プロジェクトの全体的な入力クロック信号は 50MHz であり、複数の分周器を通過する必要があり、分周係数が非常に大きいため、全体的なシミュレーションで成功することは不可能です (シミュレーション時間が長くなりすぎて失敗します)。この問題に関して、私は李冰氏に具体的に尋ねました.先生は、シミュレーション中にいくつかのモジュールを削除し、機能の一部のみをシミュレートするように私に言いました.削除されたモジュールは、プロジェクト全体の正しさを証明するために個別にシミュレートできます.私はこの案は以前から考えていたのですが、このシミュレーションはまずdiv分周モジュールを外してから、スピーカープログラムを変更して(スピーカーモジュールのシミュレーションと同様に)シミュレーションするか、divとスピーカーモジュールを外すことができることがわかりました。同時にシミュレーション。ただし、この 2 つの方法もいくつかに分けてシミュレーションを行っていますが、プロジェクト全体のシミュレーションは行っていないため、このシミュレーションは、各モジュールを個別にシミュレーションしてその機能の正確性を検証することと本質的に同じです。

各モジュールの機能が完全に正しいことが証明されている限り、プロジェクト全体の機能を実現できると結論付けることができます.各モジュールの機能は上記で完全に正しいことが証明されているので、全体の機能はプロジェクトも完全に正しいです。解析後、トップレベルのデザイン シミュレーション機能は完全に正しくなります。

3. 回路の最上位ファイルのピン割り当て図は次のとおりです。

4. 接続とダウンロード

このプログラムはハードウェア回路上に実装されています. CLK は 50MHz の水晶発振器入力に接続されています. 選曲インジケータはそれぞれ IO9, I010, IO11, IO12 に接続され、次に LED ライトに接続されています. SPKOUT を IO13 に接続し、スピーカーに接続します。

6. 結論

音楽演奏は、自動応答装置、携帯電話の着信音、グループ電話、およびインテリジェント計装機器で広く使用されています。多くの実装方法があり、その中には純粋なハードウェアを使用して音楽パフォーマンスを完成させます.FPGA統合の改善により、価格が下がり、EDA設計ツールが更新され、機能がますます普及しており、アプリケーションを作ります.このスキームの人気はますます高まっています。今日のデジタル ロジック設計者は、市場投入までの時間をさらに短縮して何万ものゲートを設計するというプレッシャーにさらされていますが、設計者は構造の独自性を維持するためにシリコン効率を犠牲にすることは許されていません。今日の EDA ソフトウェア ツールを使用してこれらの問題に対処するのは簡単なことではありません。FPGA には、構築されたパラメータ化されたライブラリ ユニット LPM デバイスが多数プリロードされています。LPM をサポートする EDA[1] ソフトウェア ツールを導入することで、設計者は構造的に独立した製品を設計し、シリコン チップを非常に効率的に使用できるようになります。

このFPGAベースの音楽ハードウェアパフォーマンス回路の設計と実装は、VHDL階層およびモジュール設計方法を採用するだけでなく、数値制御周波数分割とカスタムLPM-ROMの設計思想を採用し、設計をより最適化します。音楽パフォーマンスデジタル回路 これに基づいて、トップレベルのファイル構造を変更せずに音楽を自由に変更できます。これにより、製品開発サイクルが効果的に短縮され、設計されたチップの数が削減され、消費電力が削減され、設計の柔軟性、信頼性、およびスケーラビリティ。