入出力インターフェース

高速マイクロプロセッサと低速周辺機器が連携して機能します。データのバッファリングとラッチの機能、データ形式の変換機能、タイミング制御機能を備え、周辺機器のステータスを提供できる接続回路が必要です。これを入出力と呼びます。インターフェイス。

I / Oインターフェースには次の機能が必要です。

(1)アドレスデコード

CPUは、インターフェースにアドレスを割り当てることによりインターフェースを認識し、アドレスバスを介してインターフェースにアドレス情報を送信する。インターフェイスには、アドレスのデコード機能が必要です。

(2)データ送信

(3)ハンドシェイク接点信号を提供する

外部デバイスの動作速度は、CPUの処理速度よりもはるかに遅いことがよくあります。CPUから送信されたデータは、周辺機器によって時間内に読み取ることができず、データが失われるため、ハンドシェイクコンタクト信号が必要です(デバイスの準備が完了すると、CPUが情報を交換し、それ以外の場合は待機します) )CPUをI / Oデバイスと同期します。

(4)データ形式変換

I / Oインターフェースは、外部デバイスのステータス情報を提供できると同時に、周辺機器を制御するためにCPUのコマンドに従って制御信号を出力できる必要があります。

(5)信号レベル変換

外部デバイスのほとんどは複雑な電気機械デバイスであり、それらの信号レベルのほとんどはTTLまたはMOS回路と互換性がなく、信号レベル変換を完了するにはインターフェイスが必要です。

(6)エラー検出機能

インターフェースとデバイス間のデータ伝送はしばしば干渉され、結果として情報エラーが発生します。インターフェースには、伝送された情報を検証するための特定のエラー検出機能が必要です。

I / Oインターフェースの分類

データ伝送方式により、I / Oインターフェースはパラレルインターフェースとシリアルインターフェースに分かれています。

(1)パラレルインターフェイス。一度に1バイトまたは複数バイトのすべてのビットを送信します。

(2)シリアルインターフェース、一度に1ビット、データのすべてのビットがビットごとに転送されます。

アドレス情報、制御情報、データ情報などの情報は、システムバスを介してCPUとI / Oインターフェイス間で送信されます。データ情報、制御情報、ステータス情報などの情報は、I / Oインターフェースとデバイス間でシリアルまたはパラレルに交換されます。

I / Oポート

I / Oインターフェース回路は、いくつかの特殊レジスターのセットアップ、入出力データのバッファー、制御モードの設定、および入出力ステータス情報の保存などを行う必要があります。これらのレジスターは、CPUから直接アクセスでき、しばしばポートと呼ばれます。

ポートから送信される情報に応じて、ポートをデータポート、ステータスポート、および制御ポートに分割して、データ情報、ステータス情報、および制御情報を送信できます。

ステータス情報はペリフェラルによって提供され、CPUは時間内に読み取るため、ステータスポートは情報入力ポートです。

I / Oインターフェースが機能し始める前に、CPUはその動作モードを設定する必要があり、情報は制御ポートに保存されます。

情報伝達の方向に応じて、ポートは入力ポート、出力ポート、または入出力の双方向ポートに分けることができます。

データを出力するためだけに使用されるデータポートはデータ出力ポートと呼ばれ、データを入力するためだけに使用されるデータポートはデータ入力ポートと呼ばれます。

入力ポートの機能:

入力ポートからの場合はCPUの入力データを、外部機器は、データは、データがCPUの外に送信する際に、事前に準備ができて必要な、データが入力ポートに格納する必要があり、直接、システムバス上のデータを入力しないであなたが読むために必要がある場合データが入力されると、入力ポートはデータをデータバスに配置します。これは、入力ポートに必要なオン/オフ制御機能です。

バス構造を持つコンピュータシステムは、CPUを除いて、データをデータバスに直接ロードできません。デバイスのインターフェース回路はシステムバスに接続されていますが、デバイスによって出力されたデータをデータバスに直接ロードすることはできません。そのため、インターフェースには「スイッチ」回路が必要であり、CPUが外部デバイスのデータを読み取ると、「スイッチ」がデバイスのデータをデータバスにロードし、CPUがデータバスを介してデータを受信します。つまり、書評入力ポートには「オンオフ」制御機能が必要です。

出力ポートには次の機能があります。

周辺機器の速度が遅いため、CPUが出力ポートにデータを出力するとき、周辺機器がデータを正しく受信できるように、データを一定時間出力ポートに保持する必要があるため、出力ポートにはデータラッチ機能が必要です。

I / Oポートのアドレス指定方法

CPUはポートをアドレスで認識し、ポートアドレスはポート番号とも呼ばれます。I / Oポートにアドレスを割り当てることをアドレッシングと呼びます。I / Oポートに対処するには2つの方法があります。

- メモリとの統合アドレッシング

- 独立したアドレス指定

1.メモリとの統合アドレッシング

この方法は、メモリマップドアドレッシングとも呼ばれます。I / Oポートをメモリユニットとして扱い、CPUはアドレスを均一に割り当てます。通常、入出力システムのポートアドレス範囲の一部は、CPUのアドレス空間に描画され、メモリアドレスとしては使用されなくなります。

通常、ペリフェラルの各ポートに連続したアドレスを割り当てます

-

利点:I / Oポートへのアクセスは、メモリユニットへのアクセスと同じです。メモリにアクセスするためのすべての命令は、特別なI / O命令を設定する必要なくI / Oポートにアクセスできます。また、専用のI / Oポート制御信号を必要としないため、システムが簡素化されます。バス。

-

データ交換命令は、CPUとI / Oポート間のデータ交換を実現できます。

-

testコマンドを使用して、ポートのステータスビットをテストし、周辺機器のステータスを理解し、入出力操作の実行を判断できます。

-

-

短所:CPUアドレス空間の一部を占有します。引き出されたポートアドレス範囲はメモリアドレスとして使用できなくなり、メモリアドレス空間が削減されます。

2.独立したアドレス指定方法

CPUは独立したアドレス空間をI / Oポートに割り当て、専用の制御信号を提供します。I / Oポートアドレス空間は、メモリアドレス空間から分離されています。

- 利点:メモリスペースを占有せず、I / Oポートアドレスラインの数が少ないI / Oポートアドレススペースはメモリほど大きくなく、それほど大きなスペースを必要としないため、デコード回路は単純です。

- 短所:特別な制御信号と特別なI / O命令が必要です。

3. 8088 / 8086CPUのコンパイル方法

8088 / 8086CPUは独立したアドレス指定を使用してI / Oポートを管理し、メモリ空間は00000H FFFFFH(1MB)であり、A0 A19を使用して20のアドレスラインすべてをアドレス指定します。アドレス信号線A0〜A15を使用し、最大64Kポートを管理できます。ポートアドレス範囲は0000H〜FFFFHです。専用の制御信号IORおよびIOWまたはIO / M、RDおよびWR、専用の命令INおよびOUTを備えています。

CPUがバスを介してメモリおよびI / Oとデータを交換するのに必要な時間は、バスサイクルと呼ばれます

M / IO:= 1、バスサイクル、CPUおよびメモリが情報を交換することを示します

= 0、バスサイクル、CPUおよびI / Oインターフェイスが情報を交換することを示します

W / R:= 1、バスサイクル、CPU書き込み操作を示します

= 0、バスサイクルを示し、CPUが読み取り操作を実行する

D / C:= 1、バスサイクルがデータを送信していることを示します

= 0、バスサイクルが命令コードを送信していることを示します

これら3つの信号の組み合わせにより、現在のバスサイクルで完了した操作が決まります。

- I / Oアドレス空間の0000 03FFH範囲は通常、システム機器とISAバスポート用に予約されています。0000 00FFHセクションのポートアドレスは、クロック、タイマー、キーボードインターフェイス、割り込みコントローラー、DMAコントローラーなどのシステムボード上のデバイスにアクセスするために使用されます。このセクションのアドレス信号のA8〜A15はすべて0であるため、使用の便宜上、このセクションのポートアドレスはINおよびOUT命令では8ビットアドレスの形式で表示され、A0〜A7の内容のみを反映しています。

- 0100〜03FFHの範囲は、ディスクコントローラー、ディスプレイ、シリアルポート、パラレルポートなどのインターフェイスに使用されます。

- 0400H〜FFFFHアドレス範囲は、ユーザーアプリケーション、マザーボード機能、およびPCIバスに使用されます

CPUデータ転送制御方式

マイクロプロセッサとI / Oデバイス間の情報は同期している必要があります。一般的に使用されるデータ転送制御方法には、無条件転送モード、プログラムクエリ転送モード、割り込み転送モード、ダイレクトメモリアクセスモード(DMA)があります。

1.無条件送信

同期モードとも呼ばれる無条件送信モードは、スイッチ、リレー、ステッピングモーター、発光ダイオードなどの単純な周辺機器のデータ入力および出力に適しています。これらの周辺機器は、いつでもデータを受信し、いつでもデータを提供でき、常にCPUと同期できます。CPUは直接データを交換できます。データの入出力の制御プログラムは非常に簡単です。

2.プログラムクエリ送信方法

実際のアプリケーションでは、ほとんどのI / Oデバイスは、マイクロプロセッサよりもはるかに遅い速度で情報を送受信します。デバイスと一致させるには、CPUデータ転送の速度を下げる必要があります。CPUが情報を交換するとき、CPUはまずデバイスの現在の動作ステータスを照会する必要があります。デバイスの準備ができると、CPUは情報を交換します。それ以外の場合は待機します。この動作モードは、プログラムクエリモードまたはハンドシェイクと呼ばれます。

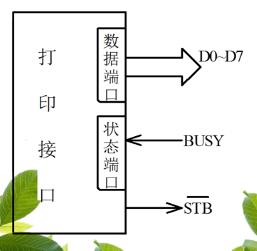

たとえば、プリンタは毎秒200文字を印刷できますが、マイクロプロセッサが文字を送信する速度は、プリンタが文字を印刷する速度よりもはるかに高速です。マイクロプロセッサとプリンタ間の接続には、速度の一致が必要です。

プロセス:

CPUは、データポートDataPを介してデータ(D0〜D7)を送信し、プリンターへのデータ選択通信信号としてSTB信号を生成します。プリンターはBUSY信号をロジック1に設定してプリンターが「ビジー」であることを示し、CPUはステータスポートStatePを介してステータス情報BUSYを読み取ります。

情報を送信する前に、CPUは最初にBUSY信号を照会またはテストします。BUSYが論理1の場合、プリンターはビジーでCPUは待機します。それ以外の場合は、データポートに文字を送信してから、STBピンにパルス信号を設定します。プリンターは、STBパルス信号を使用して、D0からD7までのデータを受信します。プリンターはデータを受信すると、BUSY信号を1に設定して印刷し、印刷後にBUSY信号を論理0に設定します。

-

短所:

この転送モードでは、CPUがデータを送信するたびに、ペリフェラルのステータスをクエリする必要があります。ペリフェラルは低速で動作します。CPUは、クエリを繰り返し実行するか、ペリフェラルと一致するまで待機する必要があります。CPUはペリフェラルとのタイミングマッチングを完了するために多くの時間を費やすため、CPUの動作効率は非常に低くなります。

3.割り込み転送方法

出力デバイスがアイドル状態または入力デバイスデータの準備ができると、インターフェイスはCPUに割り込み要求信号を送信します。アプリケーションを受信した後、CPUは時間内にインターフェイスの割り込み要求に応答し、メインプログラムの実行を一時停止し、割り込みサービスプログラムの実行に移行します。データ送信が完了した後次に、メインプログラムに戻って実行を続けます

-

利点:

このようにして、CPUはペリフェラルのステータスを検出またはクエリしなくなります。デバイスはステータスをアクティブに反映することができ、プログラムクエリモードのブラインドテストを排除します。このデータ転送モードは割り込みモードと呼ばれます。プログラムクエリ方式と比較して、割り込み転送方式は優れたリアルタイムパフォーマンスを備え、CPU時間を節約し、ペリフェラルはサービスを申請するイニシアチブを持ち、デバイスとCPUはある程度並行して動作します。

-

短所:

割り込み方式でも、ペリフェラルとCPU間の情報転送を実現するためにCPUを介してプログラムを実行する必要があります。CPUが割り込みを行うたびに、ブレークポイントとシーンの保護に時間がかかり、高速I / Oデバイスの速度要件を満たすことができません。

無条件転送方式、プログラムクエリ方式、割り込み方式は、すべてデータ転送処理中にCPUで処理する必要があります。CPUはメモリからデータを読み出して外部デバイスに出力します。したがって、これら3つの方法をまとめてプログラム制御の入出力と呼びます。プログラム(プログラムされた入出力)、PIOモードと呼ばれる

4.DMA方式

ダイレクトメモリアクセス(Direct Memory Access)方式は、単にDMA方式と呼ばれます。これは、CPUの介入なしに、内部メモリとI / Oデバイスの間にデータパスを確立して、メモリとデバイス間の高速データ転送を実現することです。

DMAモードを実現するには、周辺機器とメモリ間のデータ転送を制御するために、特別なハードウェアデバイスDMAコントローラ(DMAC)が必要です。

DMAデータ転送ワークフロー

①周辺デバイスが「DMA転送要求」信号(DRQ)をDMACに送信します。

②リクエストを受け取った後、DMACは「バスリクエスト」信号HOLDをCPUに送信し、CPUがバスを占有したいことを示します。

③CPUはデータバス、アドレスバス、対応する制御信号線をハイインピーダンス状態に設定し、3つの主要バスの使用権を譲り、DMAコントローラに「バス応答」信号(HLDA)を発行します。

④DMACがHLDA信号を受信すると、バスの制御を開始し、DMA応答信号DACKを外部デバイスに送信します。

⑤DMACはアドレス信号と対応する制御信号を送信して、周辺機器とメモリ間、またはメモリとメモリ間の直接データ転送を実現します。

specified指定されたデータの転送後、DMACはCPUに送信されたHOLD信号をキャンセルします。CPUはHOLDの失敗を検出すると、直ちにHLDA信号をキャンセルし、次のクロックサイクルでバスを制御するために再起動します。