第1章コンピュータシステムの概要

1.1基本的な構成

-

四つの主要な構造的構成要素:プロセッサ、主メモリ、入力/出力モジュール、システムバス

-

メモリとプロセッサの間でデータの送受信を行う:MAR、MBR

プロセッサと交換データ入力/出力モジュール:I / O AR、I / O BR

プロセッサPC、IR

1.2マイクロプロセッサの開発

わずかに

1.3命令実行

-

サイクル:フェッチステージ、実行ステージ

-

プログラムカウンタPC、命令レジスタIR

-

処理データ送信処理部とメモリと、プロセッサと、入力/出力モジュールデータ転送、データ(実行順序を変更)(プロセッサが実行する算術論理演算)、制御:4つの主な操作指示

-

例(プロセッサ、メモリ、データ転送、データ処理を含みます)

(1)PC = 300、命令のメモリアドレスからプロセッサ300は命令フェッチユニット1940、IRへの命令は、PC 301にインクリメントされます

(2)命令を実行し、メモリセルアドレスのプロセッサ940は、アキュムレータACに、0003データから取得され

(3)PC = 301、プロセッサ命令は、メモリ5941のユニット301をフェッチ、IR、PCへの命令からのアドレスが302にインクリメントされます

命令を実行する(4)、プロセッサ941は、アドレスAC、結果の背面からACへのデータの追加、データ記憶部0002を取り

(5)PC = 302、メモリアドレスの命令からプロセッサ302は、ユニット2941をフェッチ、IR、PCへの命令が303にインクリメントされます

(6)、プロセッサ格納アドレスデータAC、メモリセル941の命令を実行します

1.4割り込み

-

一般的な割り込みカテゴリー:割り込み、タイマ割り込み、I / O割り込み、ハードウェア割り込みの障害

-

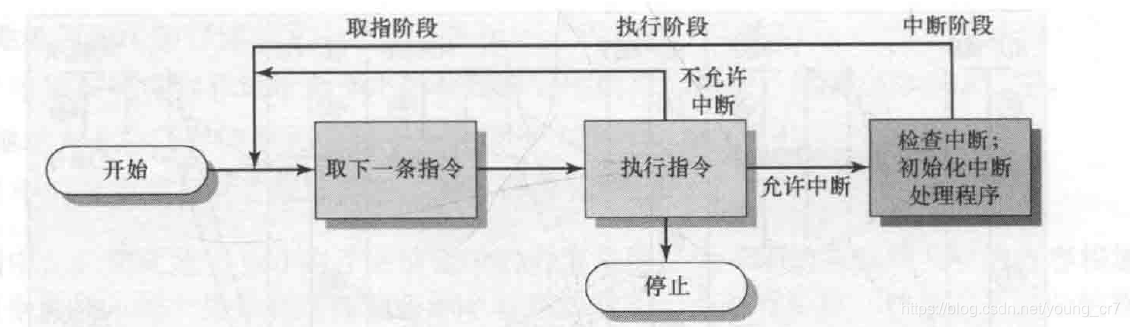

命令サイクル

-

ロングI / O待ちと短いタイミング解析プログラムI / O待ち

-

ソフトウェアとハードウェア割り込みイベント処理

-

複数の割り込み

割り込みを処理するとき(1)、割り込みが再び禁止を発生します

(2)低優先度の割り込み操作を可能にするために、割込み優先度、優先度の高い割り込みの定義

メモリ階層1.5

- コンピュータメモリの設計目標:スピード、容量と価格の間のトレードオフ

- メモリ階層

トップダウンからストレージ階層:プロセッサのレジスタ、キャッシュ、メモリ、ディスク

(1)ビット当たりの価格を下げます

(2)アクセス速度を低下させます

(3)増分キャパシティ

(4)プロセッサへのアクセスの頻度を減少させます

1.6キャッシュ

-

意義キャッシュ:プロセッサ速度の保存期間の制限が実行する命令、スピードとコストのトレードオフ、局所性の原則の使用を考慮すると、レジスタとメモリ間のメモリ容量と速度の小さな増加

-

局所性の原則:キャッシュとメモリ間のブロック転送

-

マルチレベル・キャッシュの使用

-

原則

(1)メモリ容量 単語、Kワードを含む各ブロック(ブロック)の合計 ブロック

(2)Cキャッシュメモリスロット(スロット)、各溝K単語及びタグ(ブロック記憶された識別)を有しています

(3)(ワードプロセッサは、アドレスRAを読み出し)、読み出しワードプロセッサ、RAは、キャッシュ内のブロックがない含まれている場合、プロセッサは、キャッシュスロットを割り当て、RAに含まれるメモリブロックにアクセスしますその後、CPUへのワード転送のRAが、メモリブロックキャッシュスロットをロードするステップと、RAがキャッシュに含まれている場合、ブロック、CPUへのワードのRAへの直接アクセス

1.7ダイレクトメモリアクセス

-

当I / O操作の実行:プログラム可能なI / Oを、I / O、ダイレクト・メモリ・アクセス(DMA)を割り込み駆動

(1)プログラム可能なI / O操作:Iにプロセッサ/ Oモジュールは、定期的にI / O動作が完了したかどうかを決定するために状態を確認し、命令を実行するように指示した後、プロセッサは、長い時間を待機します

(2)割り込み駆動型I / O

-

ダイレクトメモリアクセス(DMA、ダイレクト・メモリ・アクセス)

プロセッサは、データのメモリモジュール全体のブロックと直接DMA転送するDMAモジュール、命令を送信すると(1)、DMAモジュールは、完了後にプロセッサに割り込み信号を送ります

命令(2)DMAプロセッサモジュール備えるへ送ら:読み出し要求動作、I / Oデバイスかアドレス開始、メモリセル、読み出しおよびワードの書き込みを

1.8構造体の上に、マルチコアプロセッサコンピュータ

-

対称型マルチプロセッサ(SMP)

(1)定義:匹敵する性能プロセッサ、複数の共有メモリ、及びI / Oデバイス(システム・バスを介して)、I / Oデバイスへの共有アクセス、同じ機能、実行統一オペレーティングシステムの制御を、操作を行うことができます、プロセス、ファイルとの相互作用の他のデータ要素レベル

(2)単一のプロセッサと比較し

1)パフォーマンス

2)状況:シングルプロセッサ障害、ダウンタイムをもたらさないであろう

3)増分成長

4)スケーラビリティ(3)構造

キャッシュ・コヒーレンシの問題は通常、ハードウェアによって解決されます

-

マルチコア・コンピュータ:複数のプロセッサ(コア)は、チップと呼ばれる単一のシリコン・コンピュータ(シート)上に組み立てられたマルチプロセッサ