1チップの初期化

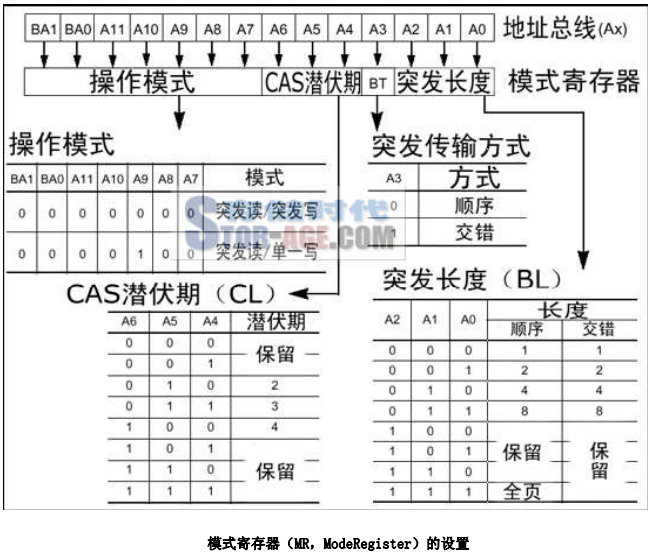

多くの人々は、SDRAMチップと論理制御ユニット内で、想像、および制御パラメータを提供するために、モードレジスタを持っていることはできません。そのため、あなたはSDRAMの電源を入れるたびは、第1制御ロジックコアを初期化する必要があります。リフレッシュプリチャージ用と以下程度の意味、モードレジスタ(MR、モードレジスタ)が設けられていることを重要な段階を持って、MRS(MRセット)と呼ばれるこの作品は、BIOS、情報レジスタの制御下で、ノースブリッジチップによって行わアドレスラインが提供します。

SDRAMモードレジスタは、動作パラメータを制御さ:0/1アドレスラインは、異なるパラメータを得るために異なる信号を提供します。MRに設定した後、我々は通常の作業条件を入力するようになりました。

2.ラインは有効です

初期化の後、アレイをアドレス指定におけるL-銀行ためには、まずその結果、アクティブ状態(アクティブ)、ロウ(行)を決定し、次いで、カラムを決定しなければなりません。BE前チップ宛が選択し、L-銀行、それらはアクティブラインと同時に行ってもよいです。

図形、CS#1から分かるように、L-銀行は、RAS(行アドレスストローブ、行アドレスストローブ)もアクティブで同時に対処しました。この時点ではアドレスラインは、特定の行アドレスを送信します。図A0-A11は、バイナリ表現であるように、12本のアドレスラインの合計で4096株(= 4096 212)の合計に、異なる値A0-A11は、特定の行アドレスを決定します。L-銀行対応する有効ラインもアクティブであるため、そう株もまたL -Bank有効有効と呼ぶことができます。

読み取りと書き込みの列3.

行アドレスが決定された後、それは、列アドレスをアドレスするために必要です。しかし、アドレスラインA0-A11はまだ(この例では)行アドレスによって使用されています。はい、SDRAMに、ロウアドレス及びカラムアドレスラインが共有されています。しかし、リード/ライトコマンドは、どのように発行されましたか?実際には、ではない信号を読み取りまたは明示的な順序を記述、それだけに送信される状態によって記述することができ、リード/ライト制御チップの目的を達成します。明らかに、WE#信号が鍵となります。WE#が有効でない場合は、もちろん、それがリードコマンドです。

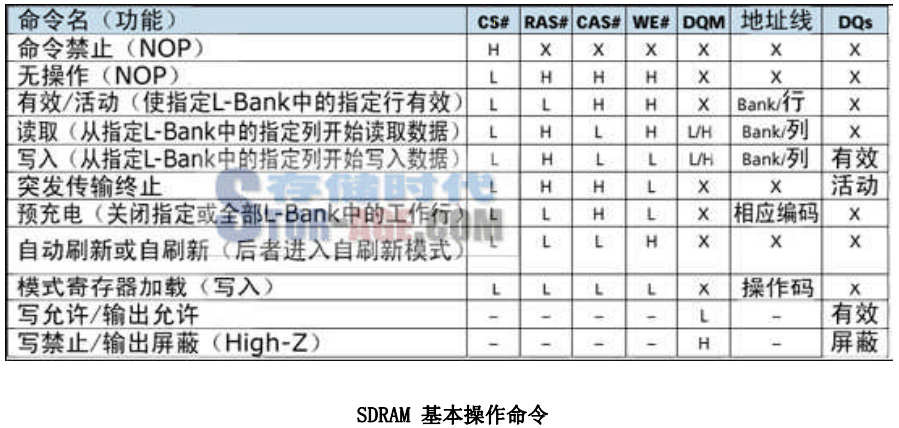

図基本的な動作を完了するために、制御/アドレス信号の種々の組み合わせを介して、SDRAMコマンドである(Hはハイレベル、Lを示すローレベルを表し、Xは、平均電力レベルが影響を及ぼさない表します)。この表では、セルフリフレッシュコマンドに加えて、すべてのコマンドは、有効なCKEのデフォルトです。セルフリフレッシュコマンドの場合は、以下が詳しいです。カラムアドレス信号と、読み取りおよび書き込みコマンドが同時に発行されています。アドレス線と共通の行アドレスが、CAS(列アドレス・ストローブ、列アドレス・ストローブ)信号は特定を決定するために、コラムアドレスのA0-A9、A11(この例では)と、アドレッシング異なる行と列と区別することができるが。

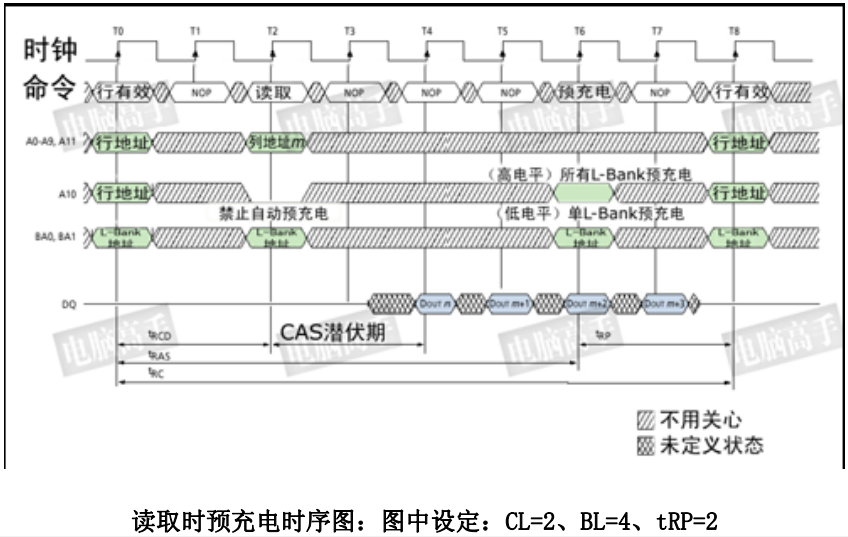

有効なコマンドライン間隔で送信されなければならない場合に列書き込み及び読み出しコマンドを、この間隔は、CAS遅延(CAS遅延にRAS)に、すなわちRASのtRCD、として定義されているが、我々は、行ストローブ期間、必要としても理解することができます応答時間が遅延によって開発された(一つの状態から別の状態変更処理の)メモリアレイチップ型電子部品です。Tは、RCDは、SDRAMの重要なタイミング・パラメータであるマザーボードノースブリッジチップを介してBIOSを介して調整することができるが、製造者の所定の範囲を超えることができません。一般のtRCDクロックサイクル(TCK、クロック時間)がかかるのtRCD = 2として単位の数であり、2つのクロックサイクルの遅延時間を表し、正確な時刻に特定は、それがPC100 SDRAM、のtRCDのクロック周波数を設定する必要があります= 20nsの代表は、PC133の遅延2は、15NSました。

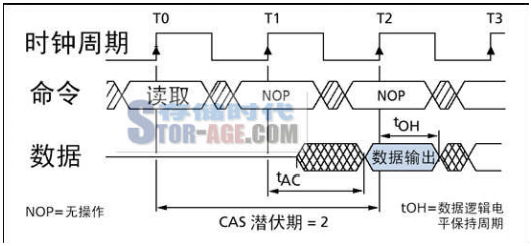

4.データ読み出し

カラムアドレスが選択された後、それは特定のメモリセルと判断された、すべてのその遺骨はI / Oチャネル(DQ)を介してメモリデータバスへのデータ出力です。それでも出力データ、第1のデータ出力の期間にCASから送信されたリードコマンドに一定の時間が経過した後、CASを発行した後、として定義され、CL(CASレイテンシ、CASレイテンシ)。CLを読むときにのみ表示されますので、それはまたCL(RL、リードレイテンシ)の読み込みの待ち時間として知られています。クロックサイクルのtRCD同数にCLユニットは、クロック周波数は、時間のかかる特定することによって決定されます。しかし、CASはCLサイクル後に記憶部に提供されていません。CASとRASは、実際にモーメントが到着したのと同じですが、応答時間が速くCAS番号です。なぜ?チップのNビット幅の」ビットを仮定し、列の数は、メモリバンクにロウアドレスストローブN×C、及びカラムアドレスストローブのみn個のメモリバンクCです。しかし、応答時間はトランジスタのボディに格納されたデータがCASと同じエッジトリガであることができない原因となり、確かに少なくとも1つのクロックサイクル遅延されます。チップの容量に、メモリセルの容量が小さいために、信号は、その効果的な可視性、S-AMPの原因この増幅/ドライバ確実にするために増幅されるチャネルS- AMPに対応するバンク。それは、すなわち、データ(決意論理レベルにも先立って電圧比較)送信信号の強度、データ出力開始の立ち上がりエッジの前にI / Oバスクロックからしたがって、データを確保するためにリードタイムでなければなりませんこれは、S-AMPに送信された、この時点で言う我々 TACの(CLKからのアクセス時、クロック・トリガを呼び出しデータの送信I / Oバスへの最終的な出力の特定の運転時間の後、データがトリガされましたアクセス時間)。タックユニットは、そうでない場合は、低い効率にアクセスするには、あまりにも長くなり、異なる周波数のNSは、異なる明確に定義されているが、あまり1つのクロックサイクルよりでなければなりません。例えば、クロック・サイクルは、PC133の7.5ns、TACは5.4nsです。各データの読み出しは、TACが第二のデータながら始まる最初のデータ送信中に、連続的な読み取りを含む、TACに有するが、それは、それを強調しています。

CL値は、チップの設計仕様を超えることはできませんそれ以外の場合は、メモリが不安定につながる、あるいは(オーバークロック選手が経験を持っている必要があります)切り替えることはできませんが、データを読む前に、暫定的に変更することはできません。CLサイクルが初期ブートMRS段階で提供され、BIOSは、典型的には、ユーザがアドレス線A4-A6ブートによりレジスタMR変化でノースブリッジチップBIOS情報CLを調整し制御することを可能にします。しかし、放電による読み出し動作後のキャパシタの元の論理状態は、論理0になり、図バンクの構造から理解することができます。したがって、データの信頼性を確保するために、DRAMの現在の行を閉じる前に、銀行は、任意の元の情報を書き換えるために、タスクが論理レベル状態に応じてリフレッシュ増幅器を完了するためにデータを渡し、データ書き換える新たな遅延が上書きされないように、この操作の出力は、データと同期と競合しないされているので、(論理0ではない上書き)。その後、改善された技術によって、リフレッシュアンプが解除され、それが再び直接読み取りによってそれに送られたキャッシュの役割を、果たし、データの論理状態を読んで残っているため、その機能は、S-AMPに置き換え、新しいアドレス出力を持っていない、とデータ書き換え動作は、プリチャージフェーズ中に完了することができます。

質問:なぜ、ハイレベルを読んだ後、離れて行くことはありませんか?上の段落への答え。

データ書き込み

データ書き込み動作ものtRCD後に行われるが、CL(CLのみ読み出し動作に現れる、覚えて)なしでこの時間、および列ハント以外は、上述したように、行アドレス指定と列をアドレス指定するためのタイミング図アドレスは、WE#がアクティブであるとき。

データとすることができるので、それは、データ信号が制御端末によって放出されるので、入力チップは、任意の調整を行うことなく、図から明らか単にデータ入力レジスタに直接伝達され、ライトドライバにより、蓄積キャパシタの、次いで充電動作でありますCASは、書き込みレイテンシが0であることを意味し、同時に送信しました。しかし、リアルタイムデータは、ストレージ容量に書き込まれていないため、トランジスタのゲートと、実際の書き込みデータが一定の期間を要するので、コンデンサは、いくつかの時間のために充電する必要があります(それは読むときと同じように)。十分な書き込み/補正時間(tWRの、書き込み回復時間)をできるようになります書かれた信頼性の高いデータを確保するために、この動作は、ライトバック(ライトバック)と呼ばれています。tWRのは、少なくとも1クロックサイクル以上のポイント(クロック周波数が高いほど、より多くのtWRの占有期間)を占め、影響は後でそれについてさらに話になります。

6.バーストモード

バースト(バースト)が連続してデータ伝送のための隣接するメモリセルの同じ行の方法を指し、記憶部(コラム)に関与する連続した送信の数は、バースト長(BLと略記、長バースト)です。メモリコントローラは、8バイトで読み出し/書き込みデータのビット幅P-銀行であるがため、現時点で、データは、複数のサイクルを経ることが一般的であり、8バイト未満が実際には稀ですデータの伝送。上記読み出し/書き込み動作は、メモリセルがアドレス指定の一つであり、連続的に読み取られるべき/書かれている場合だけでなく、現在のメモリセルの次のセルがアドレス指定されるため、列アドレスが送信され続けることです及び(アドレッシングライン上ので、もはや、ロウアドレス変更)/ライトコマンドを読みません。読み取り/書き込みレイテンシは、I / O端子に同じデータ転送を行うことができますが、早期FPE(連続しているが、それは、データの連続送信のための新しいコマンドを入力するメモリ制御リソースの多くを占める、効率が非常に低く、 / EDOメモリデータ転送)は、このように連続しています。この目的のために、バースト伝送技術が開発されてきた長い列アドレスとバースト長を開始指定されたように、メモリは自動的に連続列を提供するために、コントローラを必要とせずにバックメモリセルの読み出し/書き込み動作の対応する数に変わりますアドレス。したがって、データ伝送に加えて、最初のペン(主遅延は、一般のtRCD + CL前)、後続の各サイクルについてのデータが一つだけが得られるサイクル数を必要とします。X-1-1-1の両方で同様の多くのノースブリッジワードを導入する、Xは、ペンが使用するサイクルの最初の数を表し、それが表す意味を指します。

= 1 BLと同等であってもよい。この時点で、順次個別にアドレス指定可能なバーストを送信しなく:連続読み取りモードを非バースト。それは、データの連続送信を行うことができますが、それぞれの時間が大幅にカラムアドレスおよびコマンド情報、制御リソースの消費を送ることが。

バースト連続読み取りモード:アドレッシング及びデータの読み出し、カラムアドレス及びバースト長を開始指定した場合であれば、二つのリードコマンドインターバル期間(BLと同じ)バースト制御として行うことができ、自動的に実行さ連続バースト伝送。BLの値として、前方又は仮判定データ伝送だけでなく、が設けられています。MRSステージの初期化処理が必要であり、上述したBLを設定します。現在利用可能なオプションは、1,2,4,8、フルページ(全ページ)、ある4と8の共通セット。ところで、BLはノースブリッジチップのデザインは素晴らしい関係を持って変更することができ、誰もがBLとしてCLを調整するためにノースブリッジの調整のようにすることができます。BLは、IntelのチップセットBLとして、集合死変更されないされ、一部のチップセットは、実質的に4であるため、BLが配置され、対応するマザーボードのBIOSでnoオプションはないだろう。データ伝送システムはそれほど発現もBIOS QWORDといくつかのBL(4つのワード、すなわち64ビット)で、現在のSDRAM 64ビット/サイクルに基づいているからです。BLは、4 =こと4QWord。さらに、MRS BLの設定値の位相を除くだけでなく、特定のリード/ライト動作モードと送信のバーストモードを決定します。バースト読み出し/書き込みバースト読み出しおよび書き込み動作は、バースト転送によって表され、各読み出し/書き込み動作は、従来の設定である長BLセット、継続されます。リード/シングルライトバースト読み出し動作は、ただ1つの書き込み動作が個々に行われ、バースト転送によって表されます。バースト転送モードは、バースト期間に関与するメモリセルの送信順序を表します。順次始動セルから読み出されるシーケンシャルトランスミッションを指します。BL = 4の場合、出発細胞数をn、順序がNであり、n + 1、N + 2、N + 3。破壊通常の送信は、データ送信のインターリーブされた順番(実行されるように第1のセルの伝送としてはNであり、第2の送信部は、N + 2、N + 1ではない)であるSDRAM仕様でルールをインタリーブするように、詳細な表の定義が、この空間にし、この検討の必要性が記載されていません。

7.プリチャージ

同じL-銀行の別の行宛場合排他的アドレッシング特定のSDRAMので、それは元のアクティブ(作動)行が閉じられなければならない、読み出しおよび書き込み動作を実行した後に終了し、再送信を行/列アドレス。新しい行操作を開く準備ができてオフラインLバンク先行作業は、プリチャージ(プリチャージ)です。プリチャージコマンドによって制御される、設定が自動的に読み取りまたは書き込み動作後のプリチャージにチップを可能にすることによって支援することができます。実際には、作業は、すべてのメモリバンク、行アドレスおよびリセット書き換えプリチャージラインデータがS-AMP(の放出が比較電圧を再結合しながら、コンデンサ電圧が特定するために、一般的に1/2でありますS-AMPの論理値を格納位置のライン電圧と基準電圧とを比較することによって判断されるため、新しい行の調製に)、データの論理レベルを読み取ります。具体的には、データが戻ってSAMPに書かれている、それはSAMPを書き換え読み込みする必要がので、何の銀行はストロボ蓄積コンデンサの作品で働いてませんがあっても、乱されます。このとき、コンデンサ充電(またはそれが生成する電圧)が、これはそれよりも、閾値、半分の典型的には静電容量を設定しなければならない(読み取り時にも必要)論理状態に応じて決定されます論理1、上書き、さもなければ論理0が書き換えられていない(放電に相当)。この理由のために、今、基本的にコンデンサの他方の端子が所定の電圧にアクセスするために(すなわち1/2コンデンサ電圧)の代わりに助けに接地は、上書きの決定された時間を比較します。今、私たちは、アドレスラインA10は、コントロールが自動的に上記の「補助設定であるプリチャージ電流L-銀行、後に読んでいるかどうかことを発見することができ、背中と見たときに、読み取りおよび書き込み操作のタイミングチャートのコマンドで行きます。 " 別個のプリチャージコマンドでは、A10は、制御は、L-銀行指定されるか、または全てLバンク(L-銀行が複数存在するアクティブ/アクティブ状態である)、提供するかつて必要がプリチャージされますL-単にハイレベル信号A10に配置され、バンクアドレス、。プリチャージコマンドを発行した後、しばらくの間は間隔がtRPの(プリチャージコマンド期間、アクティブプリチャージサイクル)と呼ばれ、行アクティブRAS作業ラインを開くために、新しいコマンドを送信することを許可します。そして、のtRCD、CLのTrp単位としては、依存特定のクロック周波数の値に応じて、クロックサイクルの数です。

この図のようにオートプリチャージ開始時刻。、しかし、誰別のプリチャージコマンドとリードコマンドが発行されていない、A10アドレスラインは(オートプリチャージを可能にするために)高くなるように設定されています。可視コントロール、プリチャージ開始時刻が重要であり、すぐに運用効率を確保するため、読み取り操作の最後に新しい行を入力するに対処することができます。神話:読者がライトバックを考慮して、いくつかの記事を延期しなければならない場合は、原因ライトバックに操作した後、ストレスを受けた読み取り/書き込み操作は、いくつかの遅延を持っていますが、この記事の執筆の導入も書き換えすぐに読んで見ることができますそれは、出力データと同期されているので、デザインは、遅延はありません。唯一の書き込み操作の後に他の操作を実行し、この点で影響力を持つことになります。書き込み動作はゼロ遅延であるが、実際のデータは、ライト・バック・サイクル(tWRの)にこの時間を確保するためにあらゆるニーズに十分な期間を書かれているが。プリチャージおよび書き込み操作を同時に行うことができないので、それは順番に、tWR経過後にプリチャージコマンドを発行する必要があります書かれた信頼性の高いデータを確実にするため、書き換えられたり、データがライトバック遅延が生じ間違っているとすることができます。

映像番組データの書き込み動作のプリチャージタイミングチャート:、その存在のために、プリチャージ動作がライトバック遅延を生じる、遅延、ノートtWRのパラメータ。

8.更新

それが最も重要なDRAM動作であるので、それは常に、データを保持するために(更新)を更新する必要がありますので、それは、DRAMと呼ばれています。リフレッシュ動作や上書きのプリチャージ動作は、第1のS-AMPの書き込みによって読み込まれます。しかし、なぜ、プリチャージ動作を持っているだけでなく、それを更新するには?プリチャージがLバンクまたは全ての作業ライン操作で、リフレッシュ周期を固定したまま、不規則であるため、すべての行が順次長い時間リライタブルために経験していないこれらのバンクを維持するために操作されますデータ。しかし、そのL-バンク、行以外の全てのプリチャージは、本明細書に全て同じLバンクアドレス線を指し、それぞれのL-銀行で働く行アドレスプリチャージは、必ずしも同じではありません。限り、すべてのリフレッシュ回以上繰り返しますか?現在の標準的な受け入れ、データバンクストレージ容量の上限の有効期間は、リフレッシュ周期の各ラインが64msのであると言うことです64msの(ミリ秒、1/1000秒)、です。ライン/ 64msの数:このようなリフレッシュレートです。我々はメモリの仕様を見ると、多くの場合、あなたは4096と8192は、それぞれL-銀行のチップ内の行数を表しロゴ4096のリフレッシュサイクル/ 64msのか、8192 RefreshCycles / 64msのを参照してください。リフレッシュコマンドが有効ラインと、送信間隔は、行の数と変更され、行4096は、15.625μs(マイクロ秒、1/1000秒)、8192 7行にあります。8125μs。(SRと呼ばれるセルフリフレッシュ、)(ARと呼ばれる自動更新、)オートリフレッシュとセルフリフレッシュ:リフレッシュ動作は、2つのタイプに分けられます。これは内部の自動操作であるため、どのようなリフレッシュモードで、あなたは、外部ロウアドレス情報を提供する必要はありません。ARは、(また、リフレッシュカウンタと呼ばれる)SDRAM内部ロウアドレス・ジェネレータは自動的に順次行アドレスを生成するために使用されます。リフレッシュが一列にすべてのバンクに対して実行されているので、そう何列アドレッシングない、またはRASの前にCAS有効。だから、また、CBR(RAS前CAS、前方位置の行の列)としても知られているAR、リフレッシュ。リフレッシュが全てLバンクを含むため、これリフレッシュプロセスは、すべてのLバンクが停止され、そして時間は、各リフレッシュによって占有9つのクロックサイクル(PC133規格)であり、その後、通常動作状態に入ることができ、 9つのクロックの期間にわたり、唯一のすべての作業指示を待つことができ、この手段が実行することはできません。その後、再び、64msの後に何度も何度も循環リフレッシュを同じ行を更新します。有料のコスト優位性を達成しながら明らかに、SDRAMのリフレッシュ操作のパフォーマンスは確かに影響を受けることになりますが、これは物事の方法はありませんが、また、DRAM、SRAMに関して(スタティックRAMは、まだ更新せずにデータを保持することができます)がかかります。SRは、主に低電力スリープモード状態でデータ格納のために使用され、この態様の適用は、最もよく知られたSTR(Hibernateがメモリにサスペンド、RAMへのサスペンド)です。CKE不活性状態を発行するときにARコマンド、SRモードが入力され、その後、システムクロックは動作しませんが、リフレッシュ動作は内部クロックに応じました。SRの間、CKEを除くすべての外部信号は、(外部リフレッシュ指示はありません)有効で、唯一に終了セルフリフレッシュモードにCKE効果を再度有効にし、通常の動作状態に入ります。主に低電力ハイバネーション状態でデータ格納のために使用される、この局面の適用は、最もよく知られたSTR(Hibernateがメモリにサスペンド、RAMへのサスペンド)です。CKE不活性状態を発行するときにARコマンド、SRモードが入力され、その後、システムクロックは動作しませんが、リフレッシュ動作は内部クロックに応じました。SRの間、CKEを除くすべての外部信号は、(外部リフレッシュ指示はありません)有効で、唯一に終了セルフリフレッシュモードにCKE効果を再度有効にし、通常の動作状態に入ります。主に低電力ハイバネーション状態でデータ格納のために使用される、この局面の適用は、最もよく知られたSTR(Hibernateがメモリにサスペンド、RAMへのサスペンド)です。CKE不活性状態を発行するときにARコマンド、SRモードが入力され、その後、システムクロックは動作しませんが、リフレッシュ動作は内部クロックに応じました。SRの間、CKEを除くすべての外部信号は、(外部リフレッシュ指示はありません)有効で、唯一に終了セルフリフレッシュモードにCKE効果を再度有効にし、通常の動作状態に入ります。

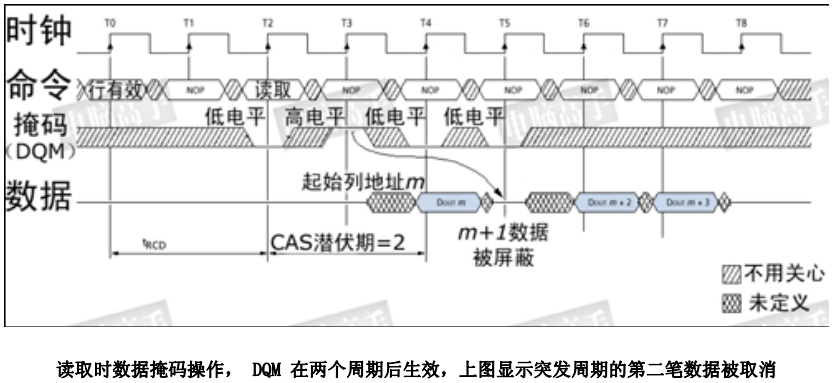

9.データマスク

読み取り/書き込み操作を伝えるとき、私たちは、バースト長について話しました。BL = 4であれば、その4×64ビットのデータ転送一度。データの第二トランシェのいずれかが必要とされていない場合は、どのようにしますか?彼らはまた、それを送信していますか?不要なデータを保護するために、それは技術(データI / Oマスクは、DQMと呼ばれる)マスクデータを使用しています。DQMすることで、入力または出力ポートがキャンセルされたメモリI / Oデータを制御することができます。

読み出し時に、データがまだ銀行からの発信マスクされます、と強調したが、時にマスクされるべき「論理ユニットをマスクします。」正確Pバンクをスクリーニングするために、ノースブリッジによって制御DQMは、各バイトのバイトのための各信号を8本のDIMM DQM信号線との各幅ビット。このように、チップ4ビットのビット幅のために、2つのデバイスが8ビットのビット幅のためのDQM信号線を共有し、一つのチップは、DQM信号を占め、16ビットのビット幅のために、2本のDQMピン。SDRAM規程は、すぐに結果としてDQM、書面で、DQMと書き込みコマンドを読んだときに、2つのクロック・サイクルを発行した後に有効になります。