Comme nous le savons tous, Ethernet a pénétré partout dans nos vies. Les entreprises, les campus, les grands centres de données et les familles ne peuvent pas se passer du réseau, sinon notre vie en sera sérieusement affectée.

Le taux d'interface d'Ethernet se développe également rapidement : 10M, 100M, GE, 10GE, 40GE, 100GE, et maintenant progressivement mûri 2,5GE, 5GE, 25GE, 50GE et même 400GE, ce qui représente fondamentalement une tendance de développement multipliée par 10 chaque 10 années.

De nombreux centres de données et opérateurs se préparent également à étendre leurs réseaux de 100GE à 400GE pour prendre en charge la technologie sans fil de cinquième génération (5G), l'intelligence artificielle (IA), la réalité virtuelle (VR), l'Internet des objets (IoT) et les voitures autonomes. La bande passante et le temps de réponse requis par les technologies émergentes telles que

Cependant, tout nouveau taux d'interface réseau, la recherche et le développement d'équipements réseau pour former le produit final et la nouvelle technologie réseau de la recherche à la mise en œuvre, chaque étape est indissociable de la vérification des tests et a posé de grands défis au test. Dans le même temps, le développement de testeurs de réseau hautes performances, stables et à haut débit ne peut pas répondre aux besoins de recherche et développement des équipements réseau.

Par conséquent, le développement de testeurs de réseau stables et à haut débit est urgent, en particulier les produits de test de réseau domestique qui maîtrisent la technologie de base.

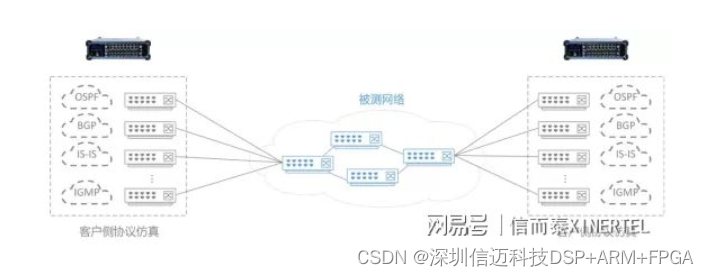

Les scénarios de test des commutateurs de centres de données à grande échelle ou des routeurs centraux réalisés par les opérateurs de télécommunications nationaux imposent des exigences extrêmement élevées au testeur.

- · La stabilité

- Il a la capacité de streaming stable à long terme, de statistiques et de simulation de protocole, comme 7x24 heures de fonctionnement stable à long terme ;

- · Répétabilité

- Le même environnement physique et les mêmes conditions de réseau, plusieurs résultats de tests doivent être cohérents ;

- · Précision

- Les résultats des tests doivent refléter avec précision les indicateurs réels de l'appareil ou du système testé, tels que les indicateurs de débit, la précision du retard et de la gigue, la précision de la planification du trafic et la précision des statistiques de trafic ;

- · Haute performance

- Prend en charge toutes les longueurs de paquets (telles que 64 à 16 000 octets ou longueur de paquet mixte IMIX), les capacités statistiques et de streaming à vitesse filaire, les capacités de simulation de protocole de routage et de commutation ultra-élevées (telles que BGP/OSPF/ISIS/PPPOE/IPOE/EVPN, etc. .); capacités de simulation de scénarios de trafic multiports (tels que des centaines de 100GE/10GE) multiservices (tels que IPV4/IPV6/MPLS/Multicast) ;

- · Standard

- Avec les normes de test internationales RFC-2544, RFC-2889, RFC3511, RFC3918, etc. ;

- · Types d'interfaces riches

- Prise en charge 1GE/2,5GE/5GE/10GE/

- 25GE/40GE/50GE/100GE/400GE et d'autres types d'interfaces prennent en charge la mise en cascade multi-châssis pour créer des scénarios de test à grande échelle.

Actuellement, les testeurs de réseaux actuellement sur le marché disposent principalement de deux architectures.

Testeur basé sur la carte réseau x86+DPDK+

La programmation de X86 est relativement simple, les méthodes de débogage sont plus abondantes et le coût présente certains avantages. C'est un bon choix pour les tests fonctionnels avec de faibles exigences.

Testeur basé sur hybride FPGA+x86

Un système de test combinant logiciels et matériels tels que FPGA+x86 convient aux scénarios de test avec des performances élevées, une couverture complète, des scénarios de test à grande échelle et des services de test complexes.

L'architecture hybride du FPGA+x86, d'une part, utilise le parallélisme des données de plus en plus puissant du FPGA au niveau matériel, et d'autre part combine la flexibilité de traitement du CPU au niveau du contrôle. Le FPGA et le CPU sont essentiellement programmables. Selon les besoins du traitement métier, le système peut déplacer de manière flexible la frontière entre le matériel FPGA et le logiciel CPU pour réaliser l'optimisation globale de l'ensemble du processus métier.

Selon les exigences complexes des scénarios de tests des opérateurs télécoms mentionnées ci-dessus, nous effectuons une analyse comparative complète des testeurs des deux architectures comme suit :

Streaming à vitesse filaire et capacités statistiques d'une longueur de paquet de 64 à 16 000 octets

Carte réseau x86+DPDK+ : en prenant le réseau 100G illustré dans la figure comme exemple, dans le cas d'une longueur de paquet de 64 octets, environ 150 millions de paquets de données seront envoyés et reçus par seconde, ce qui ne peut pas être géré par le processeur de calcul actuel. et les capacités d'accès au stockage. Les testeurs basés sur des structures FPGA n'ont pas cette limitation. Selon les dernières données publiées publiquement sur le site officiel du DPDK (2019·10·9) [source de données : site officiel du DPDK www·dpdk·org], en utilisant la configuration du système de la figure 1, il est clairement visible qu'il ne peut pas être obtenu dans le cas de petits octets tels que 64, 128, 256 paquets d'envoi et de réception à vitesse filaire 100G ;

FPGA+x86 : tous les octets peuvent réaliser un envoi de paquets et des statistiques à vitesse filaire.

Figure 1. Configuration du système de test X86+DPDK

Les performances de vitesse de ligne réalisables pour des longueurs de paquets de petits octets sont présentées dans la figure ci-dessous (la figure ci-dessous représente les performances de test de chaque longueur de paquet du système X86).

Précision du délai et de la gigue

La précision du test de retard est un indice très important dans le test du réseau.

Carte réseau x86+DPDK+ : le système X86 est un système informatique à usage général, et sa propre précision d'horloge de référence n'est pas élevée, et l'erreur de planification du système d'exploitation est au moins de l'ordre de nous ; si la carte réseau du système x86 ne prend pas en charge l'insertion d'horodatages au niveau de la couche physique. Le délai du réseau doit être géré par le système logiciel, ce qui entraînera d'autres erreurs ; par conséquent, le délai précis de l'ordre de 10 ns habituellement requis par le test du réseau est difficile à atteindre. sur la plate-forme x86 à usage général orientée informatique ;

FPGA+x86 : sur la plate-forme FPGA, une horloge jusqu'à 400 M est générée via un oscillateur à cristal avec une précision de 0,1 à 0,001 PPM, et la précision du retard peut être contrôlée au niveau de 2,5 ns.

flexibilité du système de stockage

Carte réseau x86+DPDK+ : Le système x86 est orienté vers l'informatique générale. Le système de mémoire courant actuel est la mémoire DDR4, qui a une large bande passante mais également un délai d'accès important. En fonction du mode d'accès en lecture et en écriture, il peut y avoir une gigue de retard ;

FPGA+x86 : la mémoire FPGA peut combiner diverses technologies de mémoire telles que la RAM sur puce (qui peut réaliser la fonction de cache) + DDR+QDR+RLDRAM selon les besoins, et optimiser les besoins en bande passante et retarder les besoins d'accès.

Capacité à accélérer les protocoles

x86+DPDK+carte réseau : aucune ressource supplémentaire pour implémenter des fonctions d'accélération de protocole telles que le déchargement TCP ;

FPGA+x86 : FPGA est un système programmable par matériel. Selon la quantité de ressources matérielles et les besoins du traitement métier, il peut diviser de manière flexible les limites de l'interface avec le système x86 en termes de traitement de protocole, réaliser des fonctions d'accélération de protocole telles que le déchargement TCP. , et intégrer le traitement du protocole Les tâches sans état gourmandes en calcul sont parallélisées au niveau matériel, ce qui peut considérablement améliorer la capacité de traitement de l'ensemble du système.

Précision de la planification du trafic de couche 2-3

Carte réseau x86+DPDK+ : le système x86 ne peut pas réaliser une transmission à vitesse de ligne de longueur de paquet de petits octets sur des ports à haut débit, sans parler d'une planification précise du trafic ;

FPGA+x86 : face à des commutateurs et des routeurs avec un trafic de test de plus en plus complexe et à plus grande échelle, l'architecture du système FPGA prend en charge la génération de dizaines de milliers de flux (comme les flux 64K typiques dans les testeurs haut de gamme), et elle peut contrôler avec précision le rapport de bande passante entre chaque flux et le mode de planification d'envoi, même à 5 décimales près.

Performances et précision statistiques en temps réel

Carte réseau x86+DPDK+ : la mise en œuvre du logiciel de fonction de test du processeur est essentiellement un jeu d'instructions série. Avec la réalisation de nouvelles technologies telles que l'hyperthreading multicœur, un parallélisme partiel peut être réalisé au niveau des instructions, mais pour certaines données statistiques, telles que temps réel Le nombre de trames d'envoi et de réception par seconde, etc., est défini par au moins deux paramètres (un certain delta d'intervalle de temps et le nombre de paquets d'envoi et de réception dans cet intervalle), si la lecture de ces deux paramètres est implémenté sur un cœur de CPU, La nature série de l'instruction entraînera inévitablement une erreur importante ; si la lecture de ces deux paramètres est implémentée sur deux cœurs, il est difficile pour la technologie CPU actuelle d'atteindre une synchronisation de niveau ns entre les cœurs , ce qui apporte également une imprécision de valeur aux statistiques ;

FPGA+x86 : à l'intérieur du FPGA, grâce à la technologie de programmation matérielle, la fonction d'instantané de valeur statistique peut être facilement réalisée, et la lecture des deux paramètres ci-dessus est strictement garantie de correspondre avec précision.

Évolutivité du système

x86+DPDK+carte réseau : pour un système testé à grande échelle, qu'il s'agisse d'une implémentation logicielle x86 ou d'un système hybride tel que FPGA+X86, une seule machine ne peut pas terminer la tâche de test. Mise en cascade et synchronisation du système au niveau 10ns sont des options inévitables. Le système x86 est orienté vers l'informatique générale et peut réaliser une synchronisation multi-machines en exécutant le protocole NTP, mais la précision de synchronisation de NTP ne peut pas répondre aux exigences du secteur des tests de retard ;

FPGA+x86 : dans le système hybride FPGA+x86, des technologies de synchronisation de haute précision telles que la mise en cascade de câbles locaux/GPS/1588v2 peuvent être réalisées via FPGA pour garantir la précision des tests de temps.

De plus, dans la mise en œuvre du système hybride FPGA+x86, les 2 à 3 couches de traitement du trafic sont implémentées dans le FPGA sans passer par la pile de protocoles du CPU ou les applications de couche supérieure. Le CPU n'a besoin que d'implémenter une livraison de configuration légère et présentation de l'interface, etc. Le calcul évite les défauts naturels du CPU dans le traitement des flux d'envoi et de réception à vitesse de ligne ; du côté X86, la technologie DPDK peut également être déployée de manière flexible, et la partie de traitement accéléré du protocole pur est réalisée par le système X86 , combinant les avantages du FPGA et du x86 pour réaliser un traitement métier efficace.

De toute évidence, l’adoption du système hybride FPGA+x86 est le meilleur choix pour créer un testeur de réseau hautes performances.

- Ces dernières années, la technologie étrangère de test Ethernet s'est développée rapidement et de nouveaux produits ont émergé dans un flux incessant. Avec des années d'accumulation de technologies pour les plates-formes logicielles et matérielles de test à haute vitesse et hautes performances, Spirent et Keysight, deux sociétés aux États-Unis. , occupent depuis longtemps une position de leader mondial dans le domaine des tests Ethernet. L'industrie est à l'avant-garde mondiale.

- La recherche nationale sur la technologie de test Ethernet a commencé au début du 21e siècle. Après plus de dix ans de travail acharné, les capacités indépendantes de conception et de développement de produits de test associés ont également fait de grands progrès.

Le testeur de réseau adopte la forme d'une structure de châssis + cartes enfichables.La solution matérielle globale adopte une architecture informatique distribuée, qui est logiquement divisée en un plan de données et un plan de gestion, et le module de test et le module de contrôle principal sont séparés sur le Unité physique Conception, utilisant l'architecture de système hybride FPGA+x86 pour atteindre l'objectif d'un testeur de réseau haute performance.