Annuaire d'articles

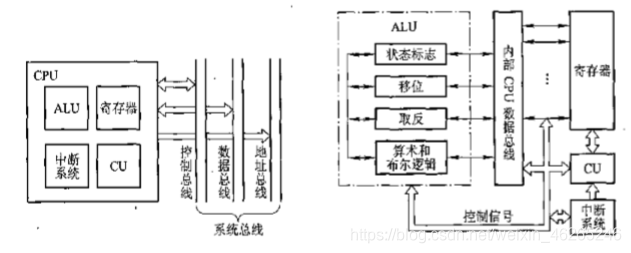

Structure du processeur

Fonction CPU

- Pour les ordinateurs structurés par von Neumann, une fois que le programme est entré dans la mémoire, l'ordinateur peut effectuer automatiquement les tâches de récupération et d'exécution des instructions. Le contrôleur est responsable de la coordination et du contrôle de chaque composant informatique pour exécuter la séquence d'instructions du programme.

- Récupération de l'instruction : le contrôleur est tenu de former automatiquement l'adresse de l'instruction, d'émettre une instruction de récupération de l'instruction et de récupérer l'instruction correspondant à cette adresse dans le contrôleur. L'adresse de la première instruction peut être spécifiée manuellement ou définie par le système.

- Instruction d'analyse : analyse quelle opération à effectuer, c'est-à-dire quelle commande d'opération le contrôleur doit émettre. Analysez l'adresse de l'opérande participant à cette opération, c'est-à-dire l'adresse effective de l'opérande.

- Instruction d'exécution : formez la séquence du signal de commande de fonctionnement et exécutez chaque instruction par le biais du fonctionnement de la mémoire, de l'unité arithmétique et du périphérique IO.

- Contrôler l'entrée du programme et la sortie du résultat de l'opération et la gestion du bus, gérer les conditions anormales et les demandes spéciales qui se produisent pendant le fonctionnement du processeur, c'est-à-dire la capacité de traitement d'interruption .

Schéma fonctionnel du CPU

Registres CPU

-

Registres visibles par l'utilisateur: registres où le CPU effectue un accès au langage machine. Avant d'appeler le sous-programme, le contenu de tous les registres visibles par l'utilisateur doit être enregistré, soit automatiquement par la CPU, soit programmé par le programmeur.

Registre général: il peut être utilisé pour stocker des opérandes et peut également être utilisé comme registre pour répondre à un certain mode d'adressage.

Registre de données: stockez l'opérande.

Registre d'adresses: enregistrez l'adresse.

Registre des codes de condition: stocke le code de condition, qui est partiellement transparent pour l'utilisateur.

-

Registres de contrôle et d'état: transparents pour les utilisateurs

MAR: registre d'adresse mémoire.

MDR: registre de données mémoire.

PC: compteur de programmes.

IR: registre d'instructions.

Unité de contrôle

- Fournit des composants de séquence de commandes de micro-opération qui complètent toutes les opérations d'instructions informatiques

Cycle d'instruction

- Cycle d'instruction: le temps total requis par l'UC pour extraire et exécuter une instruction est appelé cycle d'instruction, c'est-à-dire le temps qu'il faut à l'UC pour terminer une instruction. La phase d'extraction d'instruction termine la récupération et l'analyse des instructions. Elle est également appelée cycle d'extraction d'instruction et phase d'exécution. L'achèvement de l'opération d'exécution des instructions est également appelé cycle d'exécution. En raison des différentes fonctions de fonctionnement, les cycles d'instructions des différentes instructions sont différents.

- Instruction fetch cycle fetch instruction fetch, inter-address fetch adresse effective fetch adresse, exécute fetch cycle fetch opérande fetch, interruption du cycle de protection programme de point d'arrêt.

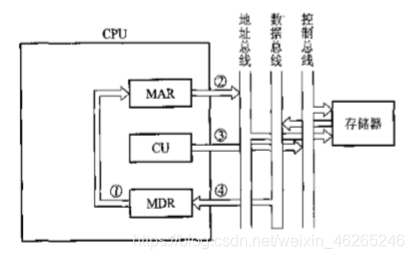

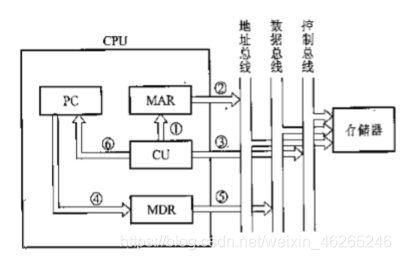

Flux de données du cycle d'instruction

L'adresse de l'instruction en cours est stockée dans le flux de données PC du cycle d'extraction . Cette adresse est envoyée au MAR et envoyée au bus d'adresse, puis l'unité de contrôle CU envoie une commande de lecture à la mémoire, de sorte que le contenu de l'unité pointée par le MAR correspondant soit envoyé au MDR via le bus de données. , Puis envoyé à IR, et la CU contrôle le PC pour ajouter 1, formant l'adresse de l'instruction suivante.

Une fois le flux de données du cycle inter-adresses terminé, le CU vérifie le contenu dans l'IR et détermine s'il a un fonctionnement inter-adresses. Si l'opération inter-adresses est requise, les N bons bits de l'adresse formelle dans le MDR seront envoyés au MAR , Puis envoyé au bus d'adresse, après quoi le CU envoie une commande de lecture à la mémoire pour obtenir une adresse valide et l'enregistrer sur le MDR.- Flux de données du cycle d'exécution

Étant donné que différentes instructions ont des opérations différentes dans le cycle d'exécution, le flux de données du cycle d'exécution est diversifié, ce qui peut impliquer un transfert de données entre les registres internes du processeur, des opérations de lecture et d'écriture vers la mémoire ou IO ou ALU L'opération ne peut pas être représentée par un flux de données unifié. - Le flux de données du cycle d'interruption Le

contenu du PC actuel doit être sauvegardé afin que la routine de service d'interruption puisse être retournée avec précision à l'interruption du programme après l'exécution de la routine de service d'interruption. La CU envoie la mémoire géologique spéciale pour stocker les points d'arrêt du programme au MAR et l'envoie au bus d'adresse, puis la CU envoie une commande d'écriture à la mémoire et envoie le contenu du PC au MDR. En plus de la mémoire, la CU doit également envoyer l'adresse d'entrée du programme au PC pour préparer le cycle de récupération du prochain cycle d'instructions.