requisitos de temporización del sistema para el diseño de la señal de reloj es muy estricto, porque todos nuestros cálculos de series se basan en una señal de reloj constante como referencia. Sin embargo, la señal de reloj real a menudo no es siempre tan perfecta, habrá fluctuación (jitter) y compensar problema (inclinación).

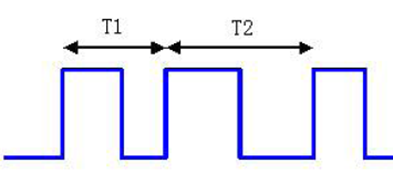

La fluctuación de fase llamada (Jitter), se refiere a la diferencia entre dos ciclos de reloj, los errores se generan en el generador de reloj interno, y el oscilador interno o el circuito PLL relacionada con ningún efecto sobre el cableado. Como se muestra a continuación:

Además, dado que el ciclo de trabajo hay una fluctuación llamado ciclo medio señal de cambio de temblor que se produce. En general, la fluctuación puede ser considerado variación de suma incierta y ocasional de la señal de reloj en sí algún proceso de transmisión.

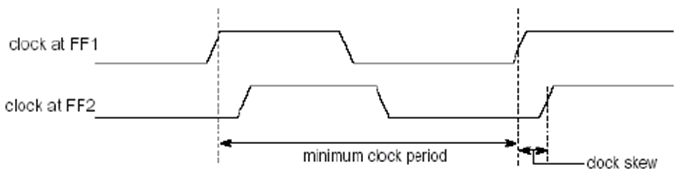

desplazamiento de reloj (inclinación) se refiere a una pluralidad de diferencia sub-retardo entre las señales de reloj generadas por el mismo reloj. Representa muchas formas, tanto comprende una pluralidad de desplazamiento entre la salida del controlador de reloj, que comprende también un desplazamiento entre el extremo de accionamiento y una señal de reloj extremo receptor ya que los errores causados trazas de PCB.

Consulte el mismo reloj skew una diferencia de tiempo de llegada de la señal de reloj entre dos registros diferentes, desvío de reloj siempre allí, en cierta medida, que afectará seriamente el circuito de temporización. Como se muestra a continuación:

integridad de la señal de sincronización, tales como la diafonía afectará a la línea de microcinta retardo de propagación; señal de reflexión de datos provoca fluctuaciones cerca de la puerta lógica de umbral, lo que afecta el tiempo máximo / mínimo de vuelo; trazas de reloj interferencia puede causar algo de desvío de reloj. Algunos de error o incertidumbre en la simulación es impredecible, el diseñador sólo para aumentar gradualmente el nivel de diseño del sistema a través de la acumulación de pensamiento cuidadoso y la experiencia práctica.

Desvío de reloj y el reloj de fluctuación es el principal factor que afecta la estabilidad de la señal de reloj. Muchos libros son de diferentes ángulos dentro de ellos explicaron.

En el que la interpretación de "ver" un libro da la más esencial:

Desvío de reloj: La variación espacial en tiempo de llegada de una transición de reloj en un circuito integrado;

fluctuación de reloj: El vatiation temporal del periodo de reloj en un punto dado en el chip;

Brevemente, skew es generalmente incierto en la fase del reloj, y la fluctuación de fase se refiere a la incertidumbre (incertidumbre) en la frecuencia de reloj. Causa de inclinación y jitter

Una gran cantidad de razones. Desde la fuente de reloj a diferentes posiciones en diferentes registros experimentó caminos de conductor y de carga, los bordes de reloj varían, con lo

oblicua. Y razones de estabilidad, la fuente de alimentación y las variaciones de temperatura provocadas por el propio cristal, la frecuencia de reloj se cambia, es decir, la fluctuación de fase.

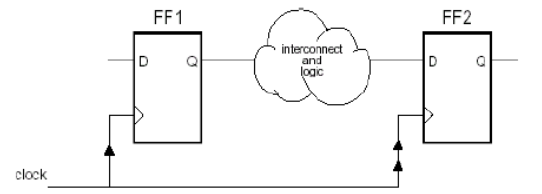

Efectos de las fluctuaciones y de inclinación del circuito pueden ser un modelo simple de explicar el tiempo. Hipótesis T (CQ) representa el retardo máximo del registro de salida FIG.

t (CQ, cd) representa el retardo de salida máxima; t (Do) y t (espera) representan la configuración de registro, tiempo de retención (no considerar Pvt) diferencia; t (lógica)

Y T (lógica, cd) representan el máximo y retardo de transmisión mínimo lógica combinatoria retardo de propagación lógica combinatoria;

En el caso sin la consideración de asimetría y la fluctuación de fase, y t (clk1) y t (clk2) misma frecuencia y fase, y el periodo de reloj T t (espera) necesita satisfacer

T> t (CQ) + t (lógica) + t (su)

t (espera) <t (cq, cd) + t (lógica, cd)

A fin de garantizar el funcionamiento normal del circuito, y para evitar la competencia. Teniendo en cuenta fase CLK1 CLK2 posterior a t1, y oblicuidad = t1.

则 t (espera) <t (cq, cd) + t (lógica, cd) - t1

Esto significa que el tiempo de retención circuito generador de violación de una mayor tendencia; consideración CLK1 CLK2 fase posterior que t2, y oblicuidad = -t2,

则 T> t (CQ) + t (lógica) + t (su) + t2

Esto significa que el rendimiento del circuito se redujo, sino porque R2 siempre cumple con el tiempo de mantenimiento, por lo que no hay competencia existen problemas. las fluctuaciones de reloj

Siempre un impacto negativo en el rendimiento del diseño general requiere muestras especiales de alrededor de 10% de margen de ser garantizada.

la incertidumbre del reloj = reloj jitter + reloj skew. jitter es la fluctuación de fase producida por la fuente de reloj. Es la diferencia en la demora de la llegada sesgar registrar dos árbol de reloj de desequilibrio. Después de cts, skew se calcula por la herramienta, la incertidumbre de reloj de modo sta puede ser proporcionada cuando un valor relativamente pequeño. Además, al hacer el registro de retención debido a que el cheque es el mismo borde de reloj, lo que no hay fluctuación única posición oblicua.