conocimiento incorporado -ARM metal desnudo - Notas de Estudio (11): Comunicación del bus I2C

A, bus I2C

1. Introducción bus I2C

I2C (Inter-Integrated Circuit) de bus desarrollada por Philips es un simple, de dos hilos bidireccional de bus serie síncrona . Sólo se requiere dos cables a la información de transmisión entre los dispositivos conectados al bus.

Un bus maestro para iniciar una transferencia de datos y genera el reloj para dispositivo de transferencia abierta, cualquier ser dispositivo esclavo direccionado en este momento se considera que es desde el dispositivo. En el bus maestro y el esclavo, y el receptor en la relación no es constante, sino que depende de la dirección de la transferencia de datos en este momento . Si los datos que se transmiten desde el dispositivo host, el dispositivo host desde la primera dirección y, a continuación, envía los datos al dispositivo esclavo, la terminación definitiva de la transmisión de datos desde el host; si desea recibir datos desde el dispositivo principal, desde el primer dispositivo dirigida por un dispositivo maestro, el dispositivo host recibe los datos transmitidos desde el host recibe el procedimiento de terminación final.

interfaz física 2. I2C

Interfaz física: la SCL la SDA + (utilizar sólo dos cables puede ser comunicación compleja)

la SCL (Reloj Serie) (1.): una línea de reloj de transmisión de la señal CLK, típicamente para proporcionar un reloj desde el dispositivo maestro canal I2C.

(2) SDA (datos en serie) : datos de la línea, los datos de comunicación se transmiten a través de la línea SDA.

3. Características de comunicación I2C

comunicación I2C es una serie, sincrónico no diferencial,, de baja frecuencia en modo de comunicación.

(1) de serie: la comunicación en serie I2C pertenece, todos los datosEn bits transmitidos en serie en la línea SDA.

(2) Synchronous: comunicación sincrónica es la comunicación tanto de trabajo en el mismo reloj , típicamente a la A-parte B a través de una línea de comunicación para transmitir la señal CLK A propio reloj, el trabajo B A reloj de transmisión. Por lo tanto, una característica importante de la comunicación sincrónica es:Hay CLK línea de comunicación.

(3) no Diferencia: debido a que la velocidad de comunicación I2C no es alta, y la comunicación a distancia cerca de ambos lados, de modo que la comunicación por medio del nivel de señal.

(4) baja tasa: I2C utilizado generalmente enLa comunicación entre las dos tablas en el mismo ICY la cantidad de datos para la transmisión, la velocidad de comunicación en sí es baja (típicamente de unos pocos cientos de kHz, diferentes chips velocidad de comunicación I2C puede ser diferente, que están utilizando el dispositivo depende del tiempo permitido en la programación de la más alta I2C de comunicación la tasa no puede exceder esta velocidad).

+ Desde el dispositivo maestro

cuando la comunicación I2C, comunicación partes son condición desigual , pero el sub-maestro y esclavo. La comunicación es iniciada por el dispositivo maestro, el dispositivo maestro por un dominante, pero el dispositivo de acuerdo con el protocolo I2C de la aceptación pasiva de la comunicación con el dispositivo maestro, y la respuesta oportuna.

Que es el maestro, que es desde el dispositivo mediante la comunicación de las partes en un dado (protocolo I2C no son necesarios), en general, un dispositivo de chip sólo puede llamar a los disparos, sólo se puede hacer desde el dispositivo, es posible no sólo cuando el dispositivo principal y cuando la energía desde el dispositivo (Pero no al mismo tiempo, cuando dos).

Puede ser una pluralidad de dispositivos en el bus (de dirección del dispositivo)

la comunicación I2C puede ser uno (1 dispositivo maestro de un dispositivo), puede ser uno a muchos (una pluralidad de dispositivos esclavos al dispositivo maestro).

Será responsable de la programación de bus maestro, decide que un tiempo de comunicación y desde qué dispositivo. Nota: el mismo tiempo, sólo un par de información de comunicación dispositivo transmisor en el bus I2C, al mismo tiempo, sólo un dispositivo maestro del dispositivo de comunicación y el otro dispositivo se encuentra en estado "hibernación", no es un problema, de lo contrario la comunicación haría se armó la gorda.

Cada dispositivo I2C esclavo tiene una dirección de esclavo comunicación I2C , la dirección del dispositivo del dispositivo de las propiedades inherentes, entoncesCuando el dispositivo de comunicación primaria necesita saber que iban a abordar la comunicación desde el dispositivo, A continuación, si la dirección no está en la comunicación desde el dispositivo que buscan. (Esta dirección es sólo una placa de circuito, no único a nivel mundial).

4. I2C sincronización de la comunicación de bus

Interpretados literalmente, el momento es la secuencia de tiempo, el tiempo es, en realidad las variaciones de nivel de línea de comunicación se producen en secuencia de tiempo, y la importancia de estos cambios se llama una secuencia de comunicación en la comunicación.

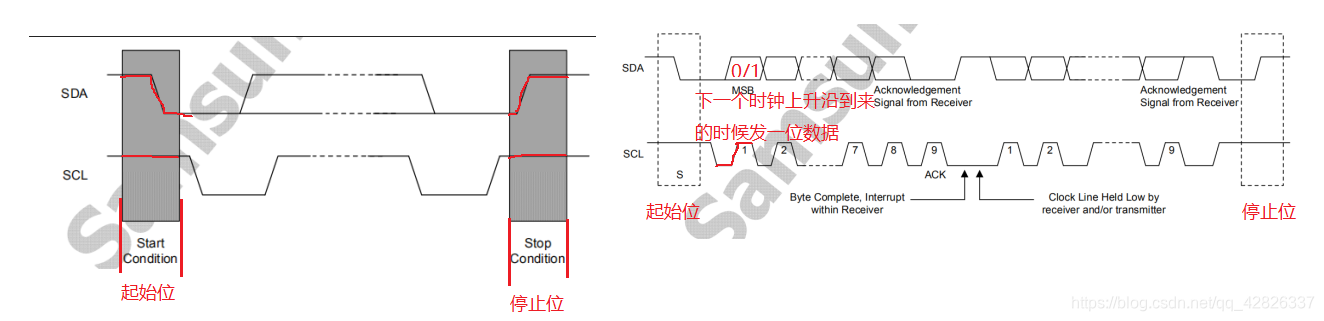

I2C estado de reposo del bus, el bit de inicio, el bit final

Hay un dispositivo host, n esclavos (n> = 1) en el bus I2C. bus I2C tiene dos estados; estado de reposo (y ninguno de todos los dispositivos desde el dispositivo de comunicación maestro, cuando el bus está inactivo) y ocupado (en la que A y un dispositivo de comunicación desde el dispositivo maestro, al bus está ocupado en este momento, otro hay que recuperar desde el dispositivo). Un ciclo de comunicación se divide en todo un ciclo, ciclo de comunicación de dos vecina estado de reposo .Cada ciclo de comunicación comienza con un bit de inicio, un final poco extremo, los datos intermedios en este ciclo de comunicación.

Bit de inicio no es un punto en el tiempo, el bit de inicio es un período de tiempo , cambia el estado del bus durante este período es:línea de CLK mantiene el nivel alto, la línea SDA es un alto a bajo va borde.

Al igual que el bit de inicio, el bit final es un período de tiempo . Durante este tiempo los cambios de estado de bus son:la línea SCL mantiene el alto nivel, el flanco ascendente de la línea SDA de bajo a alto de una.

enEl borde al lado de subida del reloj se puede producir un bit de inicio de la transmisión de datosSe debe estabilizarse antes de venir el flanco ascendente. La transmisión de datos, línea de datos de 0 a 1, antes de un flanco ascendente de la siguiente debe ser completado.

5. Formato de transferencia de datos I2C

Cada iniciado y al final del ciclo de comunicación es por el maestro para hacer , y sólo responde al dispositivo maestro a partir de una pasiva, incapaz de hacer nada por sí mismos espontáneamente. dispositivo maestro en cada período de la comunicación a partir dirección del esclavo de 8 bits (de hecho, sólo ocho dirección del esclavo es de 7, y uno frontal por debajo del dispositivo a ser escrito o leído) al bus (dispositivo host es enviado como emisión, siempre que todos los dispositivos del bus en realidad puede recibir esta información). A continuación, el dispositivo puede recibir de esta dirección, y la dirección de cada recibida en el autobús y su comparación dirección del dispositivo para la igualdad. Si la igualdad se explican el maestro de esta comunicación es hablar conmigo, si no se quiere explicar esto y otro tipo de comunicación no tiene nada que ver conmigo, no se escucha independientemente.

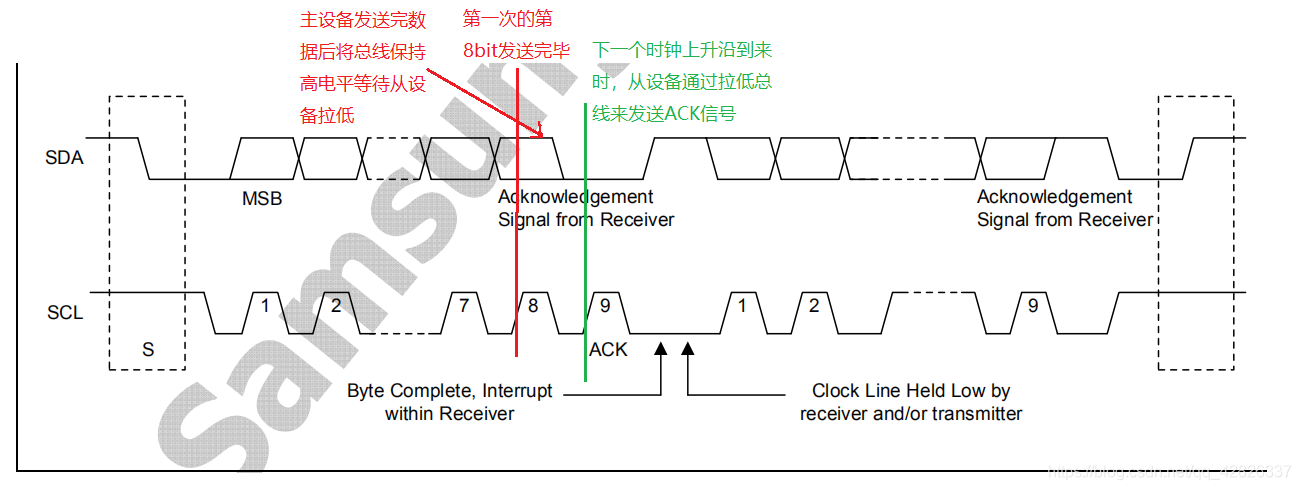

El emisor envía un fragmento de información, las necesidades receptores para responder a la ACK una . Esta respuesta en sí es sólo una posición de bit, no lleva información útil, solamente 2 representa la media (representada por cualquiera de los datos recibidos, es decir, respuesta eficaz; representa los datos o bien no recibidos, respuesta no válida).

En un determinado momento una comunicación, el dispositivo maestro y el dispositivo esclavo puede tener un solo después de la (bus ocupado, es decir, escribir al bus), el otro en el cerrado (de lectura del bus). Si en algún momento el maestro y el esclavo están tratando de escribir en el bus se terminó, la comunicación ha fallado.

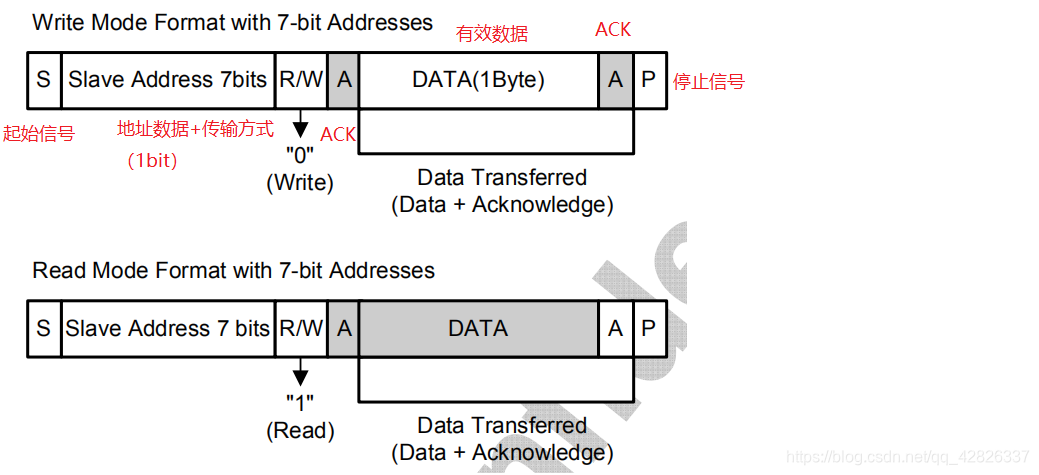

A continuación se muestra el formato de transmisión de salida:

en dondedispositivos basados en blanco a partir del dispositivo, desde el gris al aparato maestro.

Cuando el modo de escritura cuando: El primero envía una señal de arranque del maestro, seguido por el siguiente flanco de subida del reloj a una dirección temporal, se envía desde el dispositivo a través del bus (7, en donde los datos de dirección indica un modo de escritura) después de recibir la dirección de cada dispositivo en el bus de la propia dirección de contraste, si se seleccionaron los correspondiente, a continuación, una señal ACK es transmitido desde el dispositivo le dice al dispositivo maestro está listo, el maestro envía 8 datos de bits recibidos desde el dispositivo a se envía una señal de ACK para los datos transmitidos por el dispositivo maestro después de la señal de parada indica la transferencia se ha completado.

Cuando el modo de lectura cuando una situación: transmitir una primera señal de inicio desde el maestro, seguido por el siguiente flanco de subida del reloj a una dirección temporal, se envía desde el dispositivo a través del bus (7, en donde los datos de dirección indica un modo de lectura) , de cada dispositivo en el bus después de la dirección recibida con su propia dirección relación relativa, si se seleccionaron los correspondiente, a continuación, una señal ACK es transmitido desde el dispositivo le dice al dispositivo maestro está listo, y luego para iniciar la transmisión de datos de 8 bits, el dispositivo maestro recibe después de ACK para enviar una señal, y luego envía una señal de parada marcas final.

unidad de comunicación I2C cuando los datos básicos está en bytes ,Cada efectiva de datos es un byte (8 bits).

8 clk y después del bit de inicio se transmiten en el dispositivo maestro (el dispositivo que bus de control), el bus en este momento se puede leer desde el dispositivo al dispositivo maestro que la información enviada desde el aparato de lectura a través del bus; luego a noveno ciclo, de acuerdo con un protocolo predeterminado a partir de un dispositivo necesita para transmitir un ACK para el maestro, por lo que en este caso el dispositivo maestro debe liberar el bus (el dispositivo maestro de bus está ajustado a un nivel alto y no se mueven, de hecho, similar al estado de reposo bus), mientrasACK enviado desde los intentos de dispositivos para tirar hacia abajo el autobús. Si el bus de bajada de fallas en los equipos, o simplemente no tienen el equipo por el bus, el dispositivo maestro es el autobús para ver el fenómeno sigue siendo alta en el noveno ciclo, que es el maestro, significa que no reciben ACK, acabamos de considerar el dispositivo maestro al dispositivo esclavo envía 8 bytes (fallo de recepción) equivocada .

Dos, bus I2C S5PV210

controlador 1. I2C

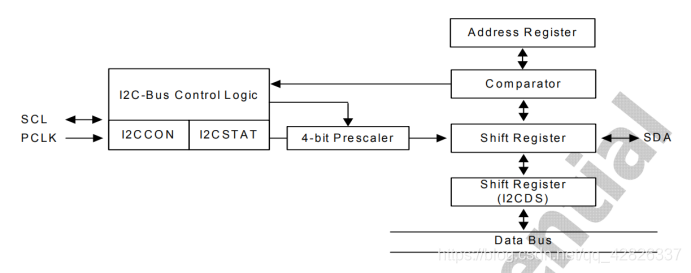

Desde el dispositivo de comunicación principal es esencialmente dos lados midiendo el tiempo de la obra, pero el momento serían software de SoC más complicado no es propicio para la terminación, y por lo tanto la solución es SoC interno controlador integrado de hardware genera una sincronización de la comunicación . Tan sólo hay que escribir los valores de configuración de software pueden escribirse en el registro del controlador, el controlador generará el momento adecuado en las líneas de comunicación y otras comunicaciones.

(1) fuente de reloj es PCLK_PSYS (65MHz) , a través del nivel de división interna 2 obtenido finalmente controlador CLK I2C. La primera fracción es la frecuencia de bit6 I2CCON, puede ser una I2CCLK reloj intermedia (igual PCLK / 16 o PCLK / 512); segunda fracción era el controlador final de frecuencia de reloj I2C trabaja para I2CCLK la fuente de reloj intermedio, factor de división de frecuencia [1,16], porque de 4 bits (que corresponde a 15 además de 0 a 1). Para obtener la etapa final después de que el reloj se divide por 2 relojes, tal ajuste está disponible: 65000KHz / 512/4 = 31kHz CLK comunicación se pasa desde el dispositivo a través de la línea de SCL .

(2) de lógica de control de bus I2C (representantes delanteros son I2CCON, I2CSTAT ambos registros), es principalmente responsable de la secuencia de comunicación I2C. programación real para enviar un bit de inicio, bits de parada, etc., están recibida a través del registro de dos ACK (representado detrás del módulo de circuito) implementado.

(3) un registro de desplazamiento (registro de desplazamiento), los datos de código de bytes a transmitir en un bit por registro de desplazamiento de un bit lanzó la línea SDA para la transmisión / recepción .

+ Registro de direcciones comparadores. controlador I2C a hacer con el tiempo presente desde el dispositivo.

(4) El I2CADD : para escribir su propia dirección del esclavo.

(. 5) I2CDS : se colocan de transmisión / datos recibidos aquí.

2. Proceso de comunicación de bus

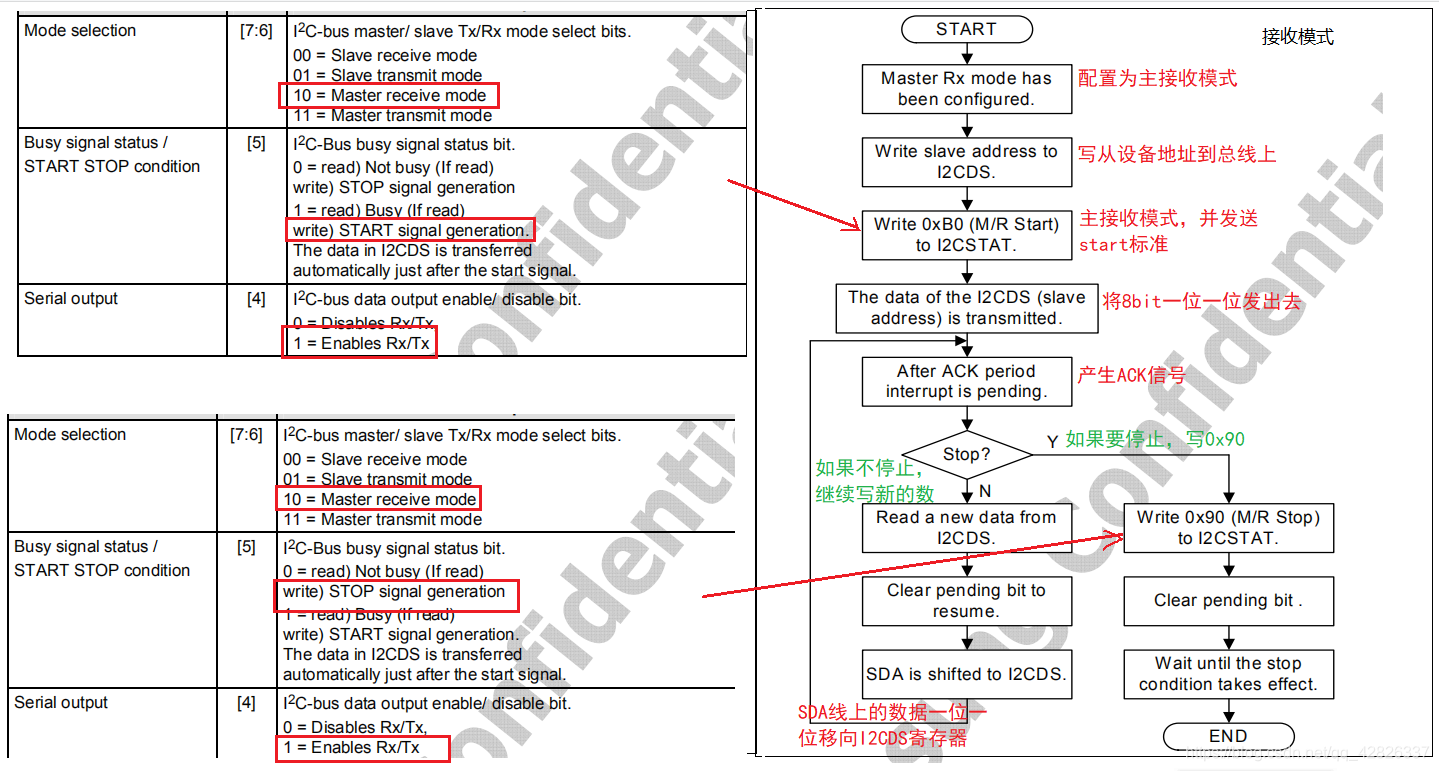

Maestro / recibir modo de

añadir aquí que: es decir, cuando la transmisión de datos de 8 bits de direcciones, de hecho, es la dirección de + 1 bit dirección de 7 bits.

Por ejemplo:

KXTE9 dirección I2C fija 0b0001111, dirección I2C esclavo en sí es 7 bits, pero transmite un I2C comunicación I2C transmite realmente cuando la dirección del esclavo es de 8 bits, los 8 bits 7 bits (bit7-bit1 ) que corresponde a la dirección I2C esclavo del dispositivo 7, el más bajo (LSB) se almacena en R / W información (es decir los siguientes datosaparato de escritura para la lectura desde el dispositivo maestro (correspondiente a 0), el dispositivo maestro lee de, o dispositivo de escritura (correspondiente a 1)). Así, por KXTE9 es, cuando el dispositivo maestro (SoC) emitió información Gsensor, el SAD debe ser: 0b00011110 (0x1E), mientras que el maestro lee Gsensor información, que debe ser 0b00011111 (0x1F).