ARMv8 TTBRx register

1 TTBR0_ELx and TTBR1_ELx

Selection between TTBR0_ELx and TTBR1_ELx when two VA ranges are supported

.

Every translation table walk starts by accessing the translation table addressed by the TTBR_ELx for the stage 1 translation for the required translation regime

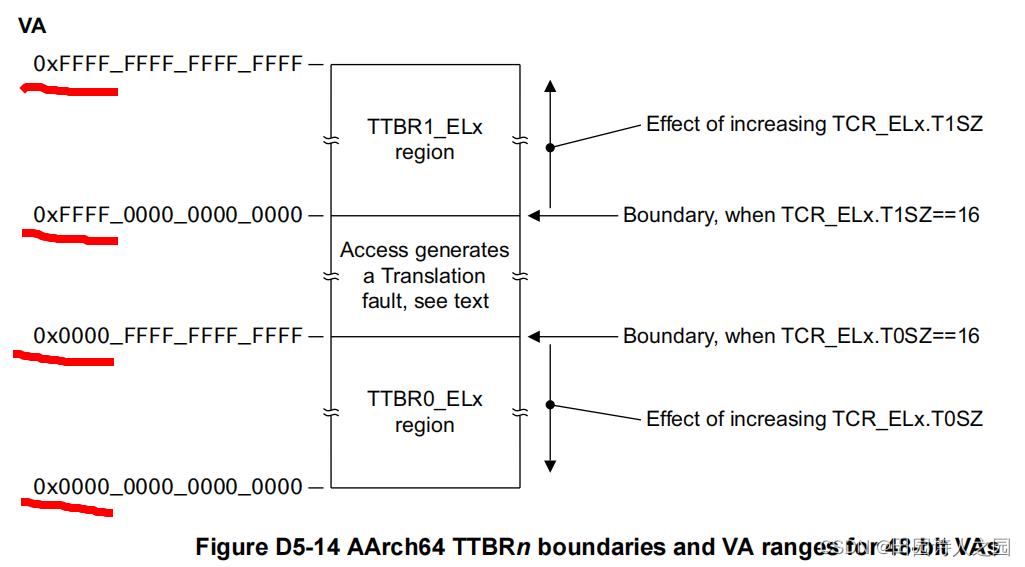

. 1 stage conversion. For a stage 1 translation that can support two VA ranges, Figure D5-14 shows

this VA range split when using 48-bit

VAs, and:

VA range division when using 48-bit VA.

- TTBR0_ELx points to the initial translation table for the lower VA range, that starts at address 0x0000000000000000

- TTBR0_ELx points to the initial translation table for the low VA range starting at address 0x0000000000000000

- TTBR1_ELx points to the initial translation table for the upper VA range, that runs up to address 0xFFFFFFFFFFFFFFFF.

- TTBR1_ELx points to the initial translation table for the upper range of VA values up to address 0xFFFFFFFFFFFFFFFF.

As Figure D5-14 shows, for 48-bit VAs: - The address range translated using TTBR0_ELx is 0x0000000000000000 to 0x0000FFFFFFFFFFFF.

- The address range translated using TTBR0_ELx is 0x000000000000 to 0x0000FFFFFFFF.

- The address range translated using TTBR1_ELx is 0xFFFF000000000000 to 0xFFFFFFFFFFFFFFFF.

- The address range translated using TTBR1_ELx is 0xFFFF000000000000 to 0xFFFFFFFFFFFFFFFF.

Which TTBR_ELx is used depends only on the VA presented for translation. The most significant bits of the VA must all be the same value and:

Which TTBR_ELx is used depends only on the VA presented for translation. The most significant bits of VA must all be the same value, and: - If the most significant bits of the VA are zero, then TTBR0_ELx is used.

- If the most significant bit of VA is zero, then TTBR0_ELx is used.

- If the most significant bits of the VA are one, then TTBR1_ELx is used.

- If the most significant bit of VA is 1, then TTBR1_ELx is used.

2 TTBR0_ELx

2.1 TTBR0_EL1

TTBR0_EL1, Translation Table Base Register 0 (EL1)

The TTBR0_EL1 characteristics are:

Purpose

Holds the base address of the translation table for the initial lookup for stage 1 of the translation of an address from the lower VA range in the EL1&0 translation regime, and other Information for this translation regime.

Saves the base address of the translation table used for the initial phase 1 lookup of addresses translated from lower VA ranges in the EL1&0 translation regime, and other information for this translation regime.

Configurations

AArch64 System register TTBR0_EL1[63:0] is architecturally mapped to AArch32 System register TTBR0[63:0].

Attributes

TTBR0_EL1

is a 64-bit register.

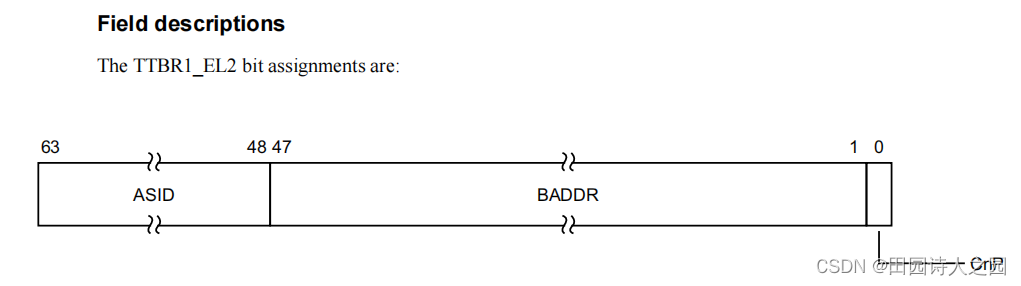

Field descriptions

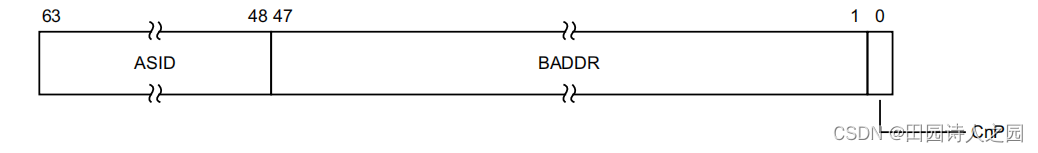

The TTBR0_EL1 bit assignments are:

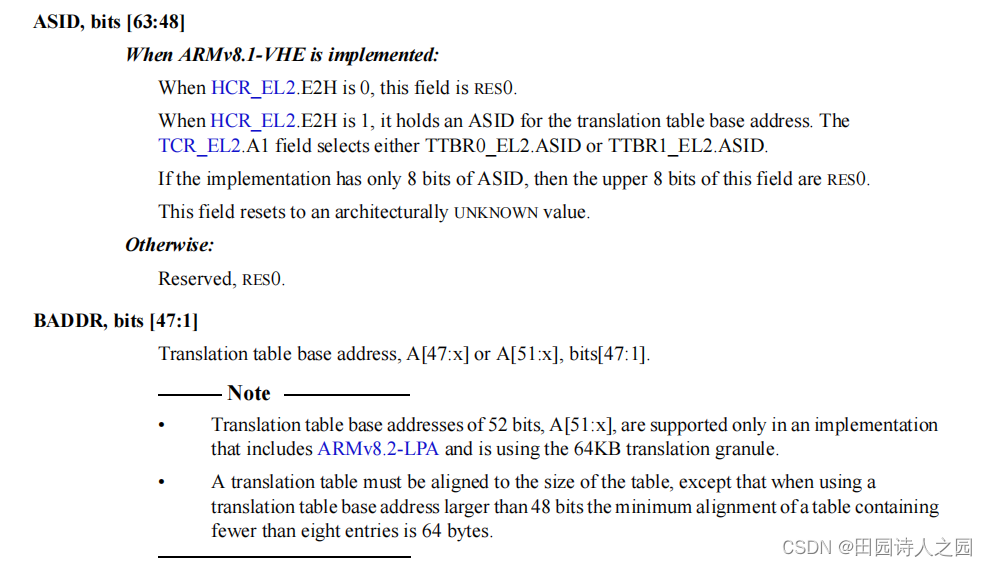

ASID, bits [63:48]

An ASID for the translation table base address. The TCR_EL1.A1 field selects either TTBR0_EL1.ASID or TTBR1_EL1.ASID

. The TCR_EL1.A1 field selects TTBR0_EL1.ASID or TTBR1_EL1.ASID.

If the implementation has only 8 bits of ASID, then the upper 8 bits of this field are RES0.

If the implementation has only 8 bits of ASID, then the upper 8 bits of this field are RES0.

This field resets to an architecturally UNKNOWN value

.

BADDR, bits [47:1]

Translation table base address, A[47:x] or A[51:x], bits[47:1].

Translation table base address, A[47:x] or A[51: x], bits[47:1].

Note:

- Translation table base addresses of 52 bits, A[51:x], are supported only in an implementation that includes ARMv8.2-LPA and is using the 64KB translation granule.

- The 52-bit translation table base address A[51:x] is only supported in implementations that include ARMv8.2-LPA and use 64KB translation granularity.

- A translation table must be aligned to the size of the table, except that when using a translation table base address larger than 48 bits the minimum alignment of a table containing fewer than eight entries is 64 bytes.

- Translation tables must be aligned according to the size of the table, but when using a translation table base address greater than 48 bits, the minimum alignment for translation tables containing less than 8 entries is 64 bytes.

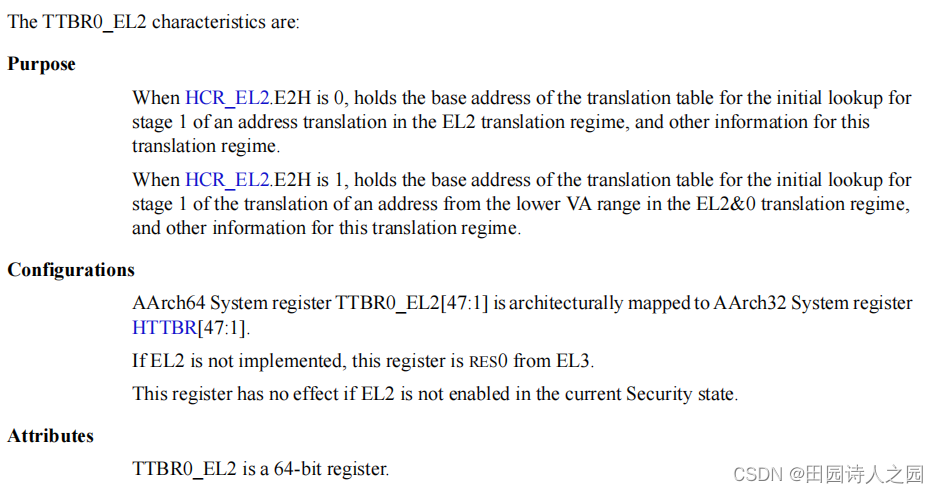

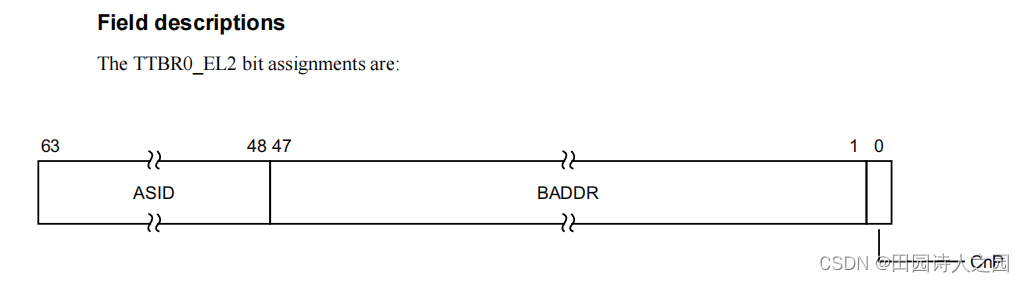

2.2 TTBR0_EL2

TTBR0_EL2, Translation Table Base Register 0 (EL2)

A translation table must be aligned to the size of the table, except that when using a translation table base address larger than 48 bits the minimum alignment of a table containing fewer than eight entries is 64 bytes.

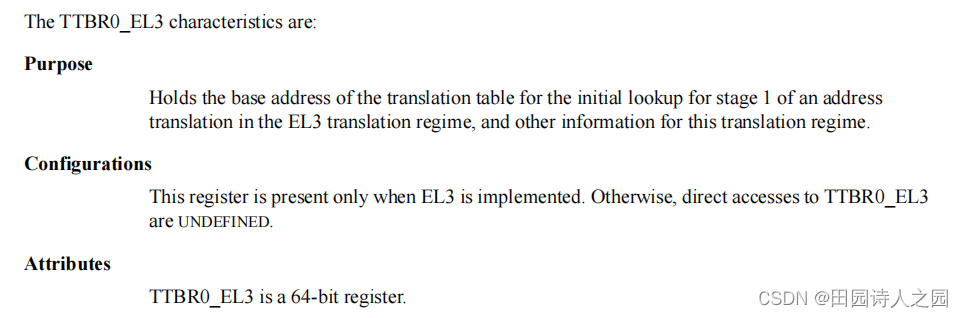

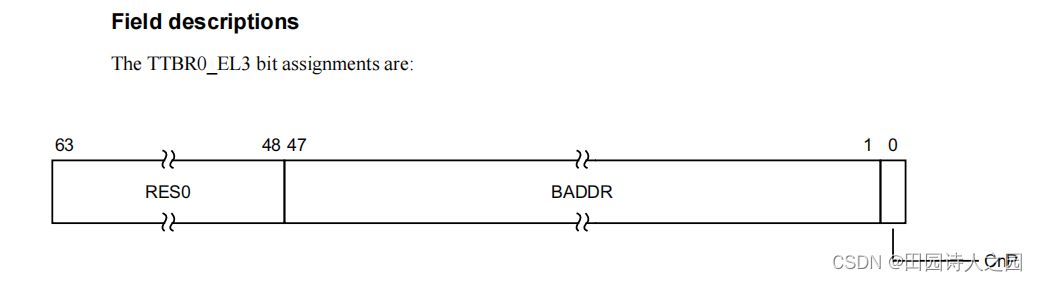

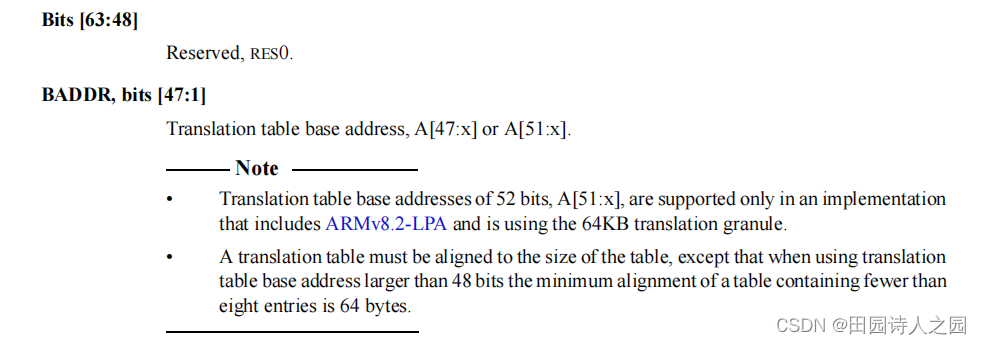

2.3TTBR0_EL3

TTBR0_EL3, Translation Table Base Register 0 (EL3)

3 TTBR1

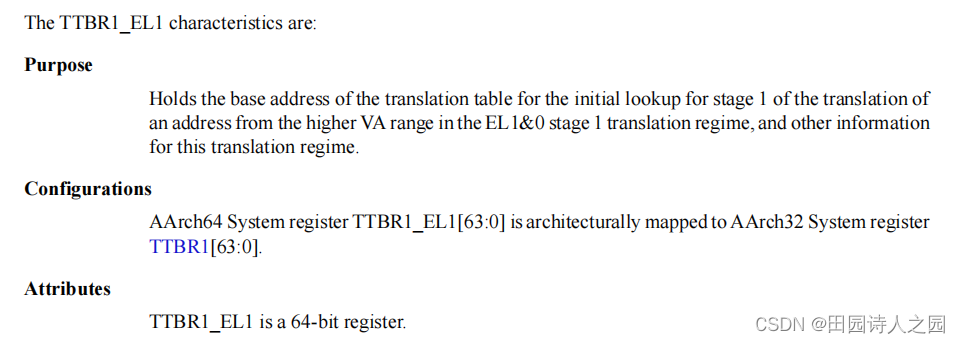

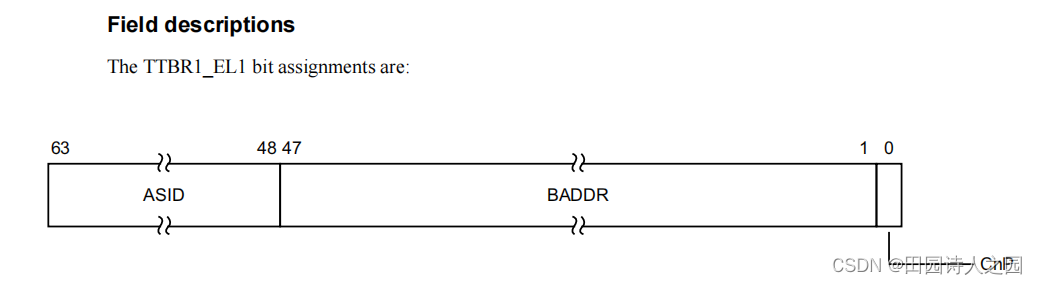

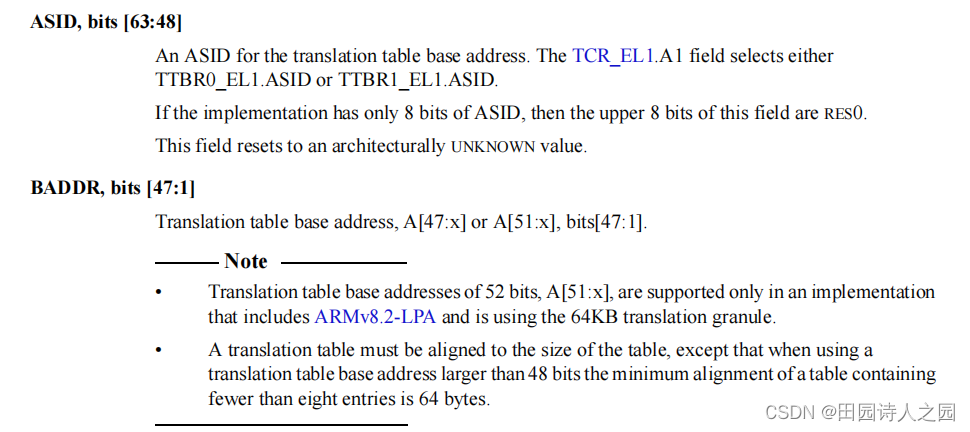

3.1 TTBR1_EL1

TTBR1_EL1, Translation Table Base Register 1 (EL1)

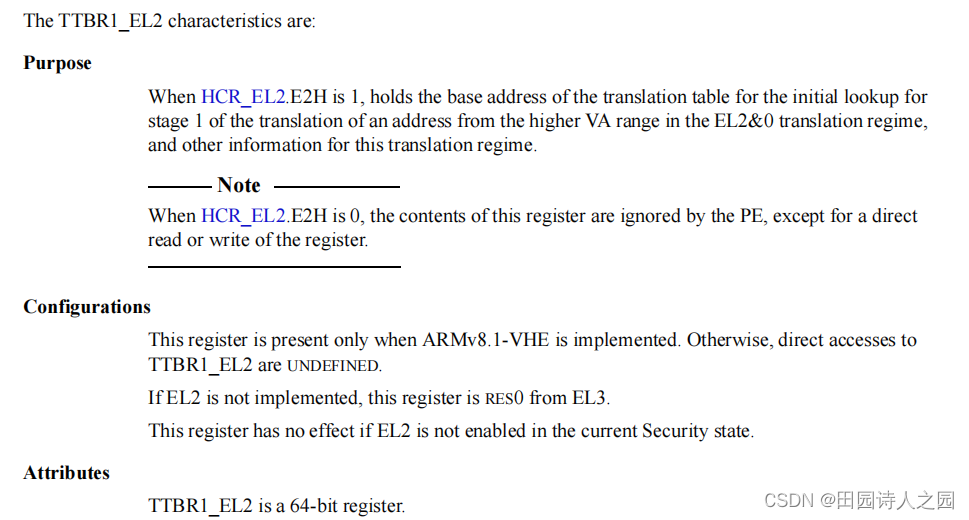

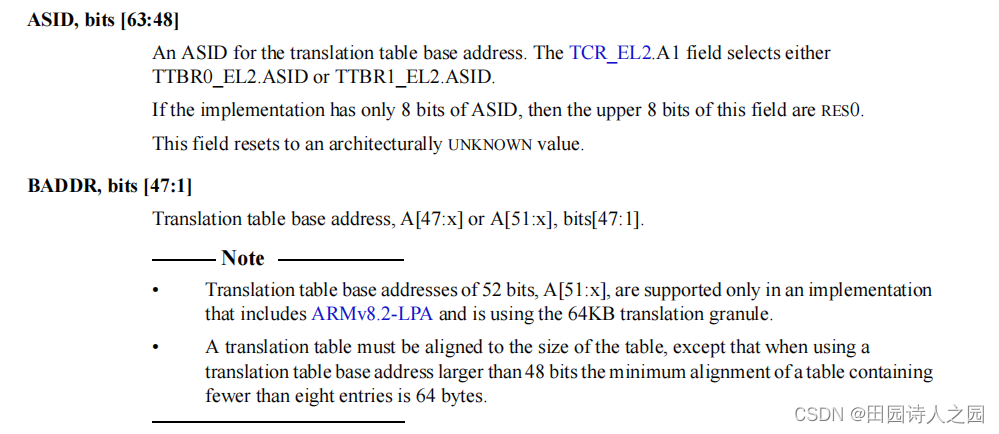

3.2 TTBR1_EL2

TTBR1_EL2, Translation Table Base Register 1 (EL2)

4 Access TTBRx register

4.1 TTBR0_ELx

Read the value of the TTBR0_ELx register into a normal register

mrs <Xt>, TTBR0_ELx

Write the value of the ordinary register Xt into the TTBR0_ELx register

msr TTBR0_ELx, <Xt>

4.2 TTBR1_ELx

Read the value of the TTBR1_ELx register into a normal register

mrs <Xt>, TTBR1_ELx

Write the value of the ordinary register Xt into the TTBR1_ELx register

msr TTBR1_ELx, <Xt>

5 Does TTBRx reserve physical addresses or virtual addresses?

5.1 Is the physical address or virtual address saved?

In the ARMv8 architecture, the TTBR (Translation Table Base Register) register stores the physical address of the first-level page table .

The ARMv8 architecture uses paging memory management. The page table contains the mapping from virtual addresses to physical addresses. When the CPU needs to access memory, the hardware will look up the page table based on the virtual address to obtain the corresponding physical address.

The page table itself is also in memory, so there needs to be a way for the hardware to know where it is. This is what the TTBR register is for. When the page table needs to be looked up, the hardware will read the physical address of the page table from the TTBR register, and then search the corresponding physical address in the page table based on the virtual address. Therefore, the TTBR register holds the physical address of the first-level page table.

5.2 Why is it a physical address rather than a virtual address?

The main reasons for using physical addresses instead of virtual addresses are to avoid recursion and reduce complexity.

If TTBR saves a virtual address, then when converting the virtual address to a physical address, you need to find the physical address of the page table first, and the virtual address of the page table needs to be converted in the same way. This forms an infinite recursion and cannot be completed. Addressing.

Secondly, converting from a virtual address to a physical address is a very frequent operation. If the address conversion is performed again during this process, the efficiency will be extremely low. Direct indexing from physical address reduces time and complexity.

Saving the physical address also reduces the hardware implementation complexity of the processor during address translation. Each time the processor performs address translation, it can directly load the physical base address of the page table from TTBR, without the need for another virtual-to-physical conversion.

Therefore, in order to solve this recursion problem, while improving the efficiency of the processor and simplifying the hardware design, the address of the page table needs to be a physical address.