introducción

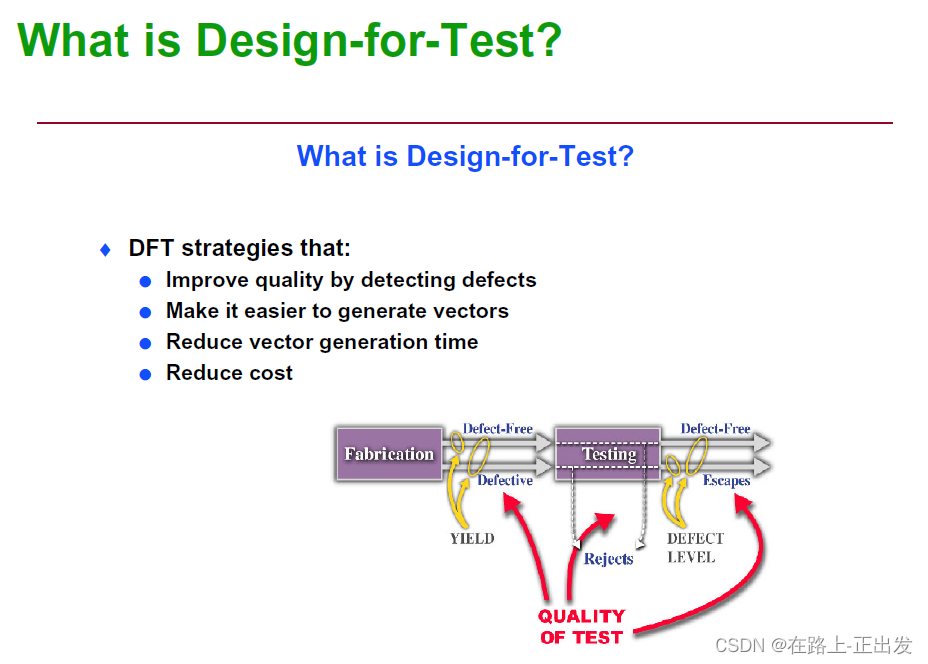

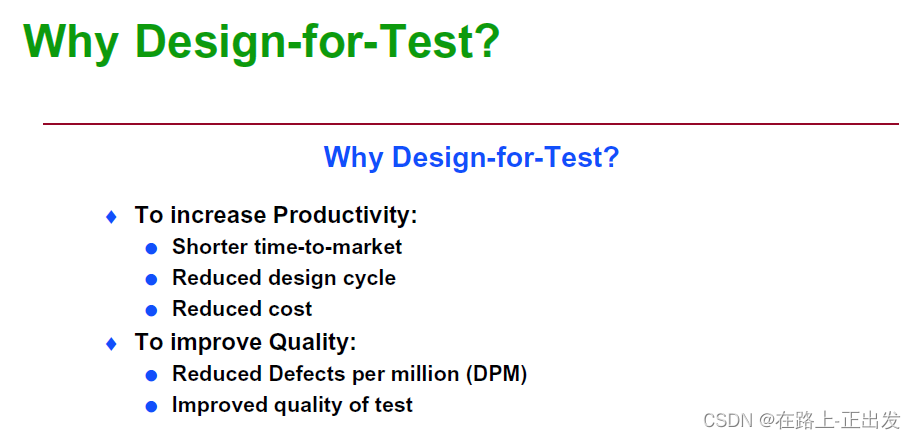

DFT es un vínculo indispensable en el proceso de diseño de chips ASIC. Su objetivo principal es insertar alguna lógica comprobable, como cadenas de registros, después de completar la verificación del diseño del front-end del chip, que puede considerarse como la categoría de diseño de back-end de IC . Principalmente después de que se completa la cinta del chip ASIC, a través de estas lógicas insertadas, se detecta la calidad de fabricación del chip obtenido de la cinta. Detectar algunas fallas fijas, etc.

referencia de aprendizaje

- Pruebas y diseño de sistemas digitales para su capacidad de prueba. 【América】Senara Bodine-Nawabi. Original y traducción.

- Vídeo explicativo de la Academia de Cultivo.

- Curso electrónico de la red DFT.

- Conferencia de Chen Xinwu del Centro de Diseño de Circuitos Integrados de la Universidad de Ciencia y Tecnología de Huazhong "Investigación del método de prueba de circuitos integrados".

- Diseño para prueba: libro de trabajo para estudiantes de capacitación en escaneo y ATPG, gráficos de mentores de derechos de autor.

Comprensión sencilla de DFT

Agregue algo de sobrecarga de hardware para realizar algún diseño de prueba auxiliar. Es necesario generar algunos vectores de prueba eficientes para las pruebas. DFT no solo inserta cierta lógica diseñada, sino que también incluye generación de vectores de prueba específicos, análisis de resultados de pruebas, etc.

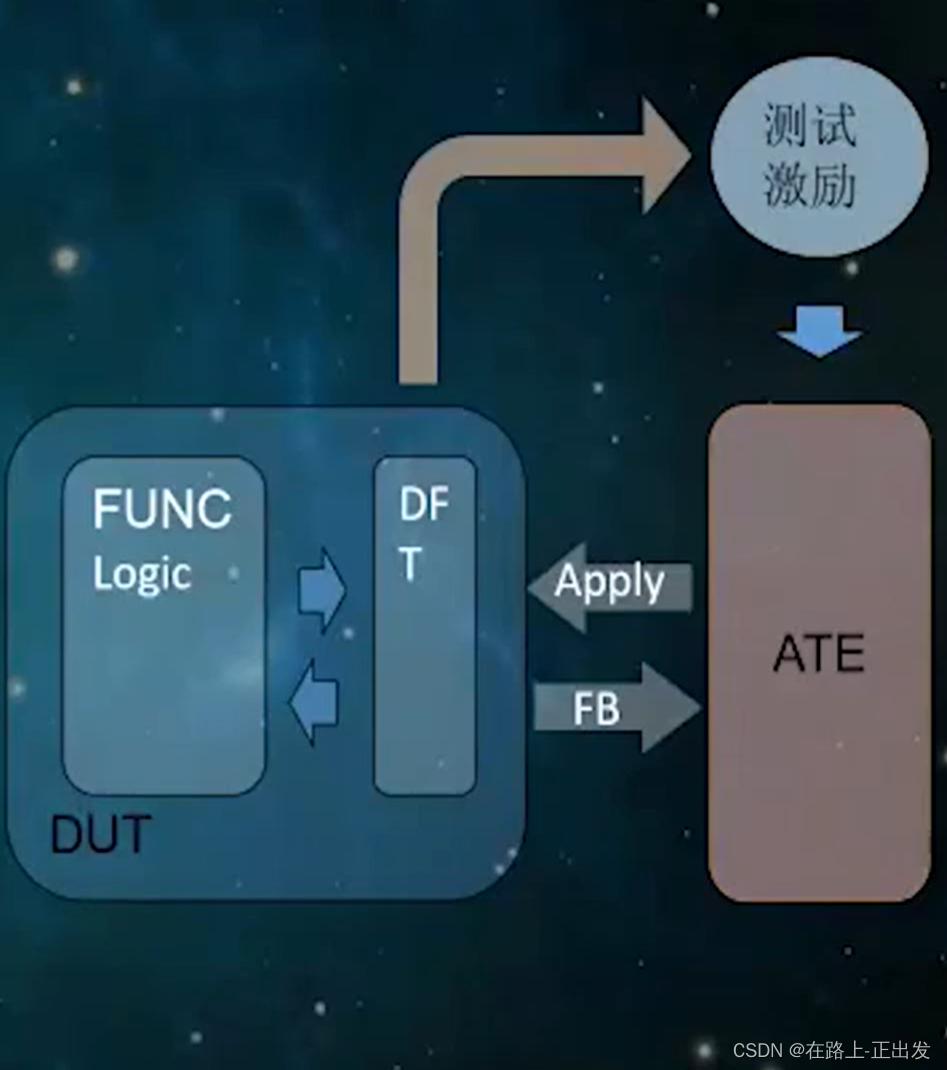

ATE es una máquina de prueba automática, que estimula el DUT a través del vector de prueba, y la retroalimentación del DUT se envía al ATE, el ATE compara si la respuesta recibida es consistente con la respuesta esperada y completa la prueba del DUT.

estrategia DFT

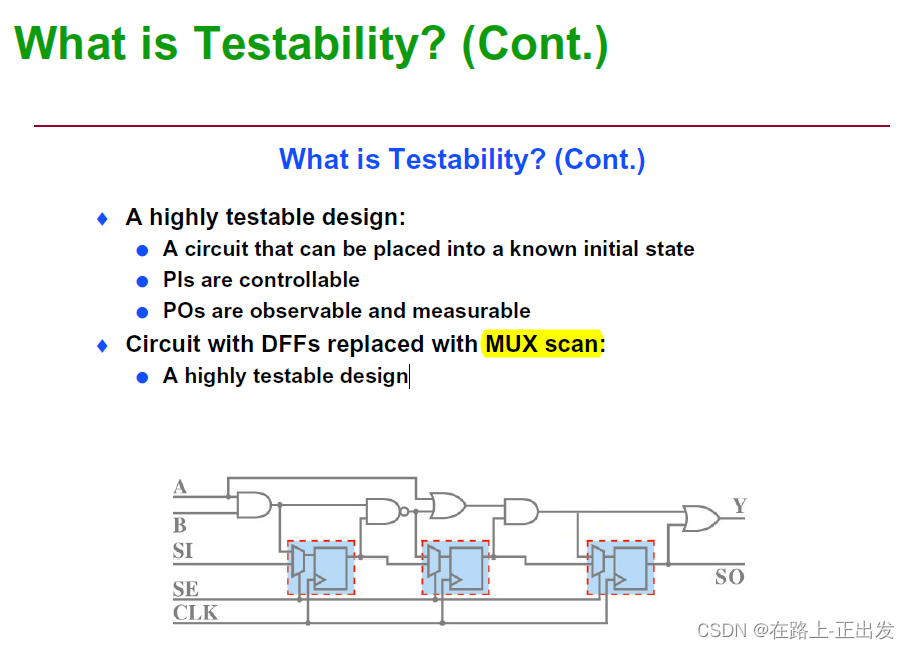

Ejemplo de circuito de comprobabilidad

El registro será reemplazado por una cadena de registros con MUX. Cuando SE es 1, cada registro está conectado de un extremo a otro para formar una cadena de registros para generar en serie los datos emitidos por la prueba.

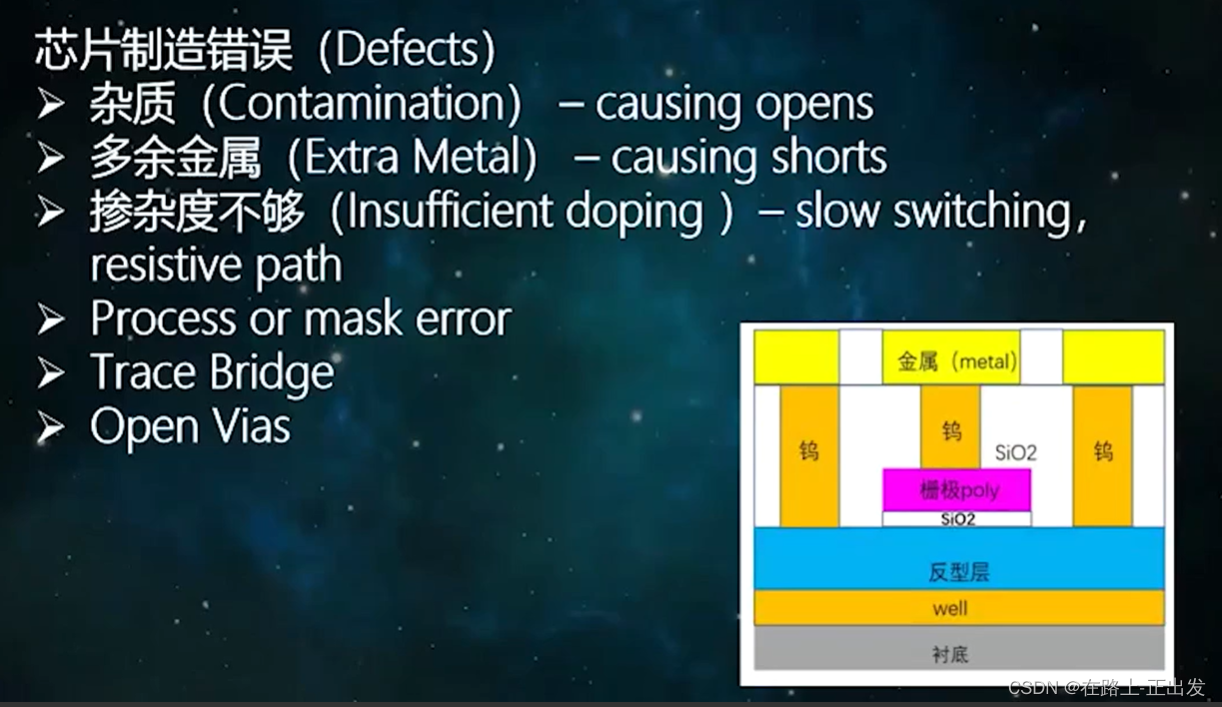

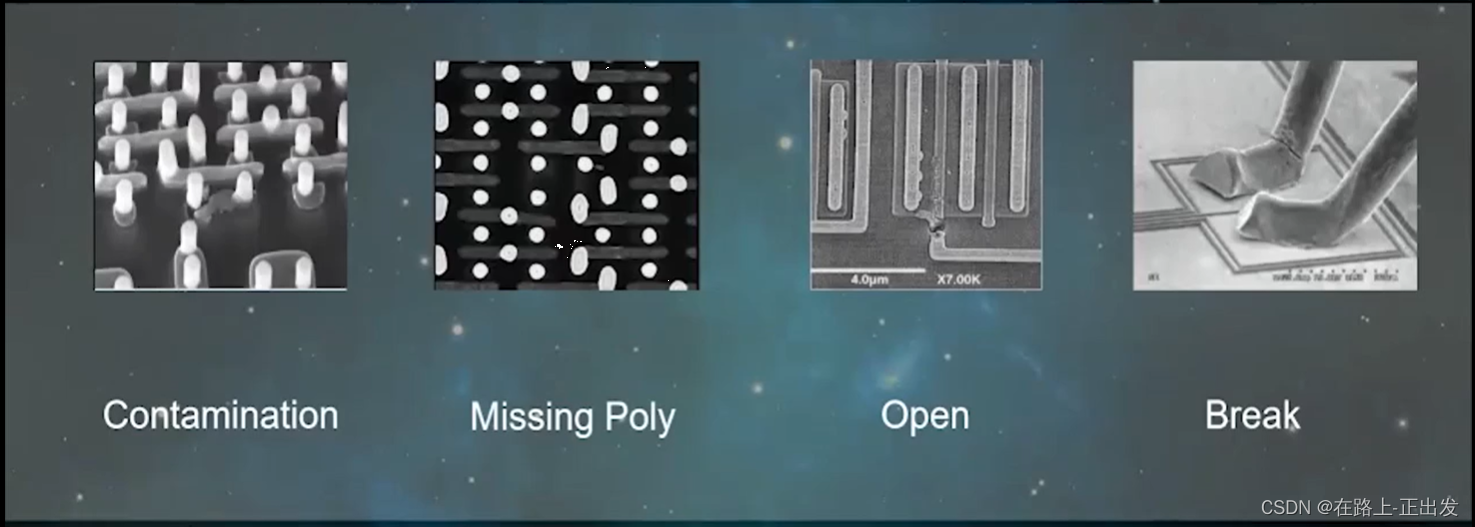

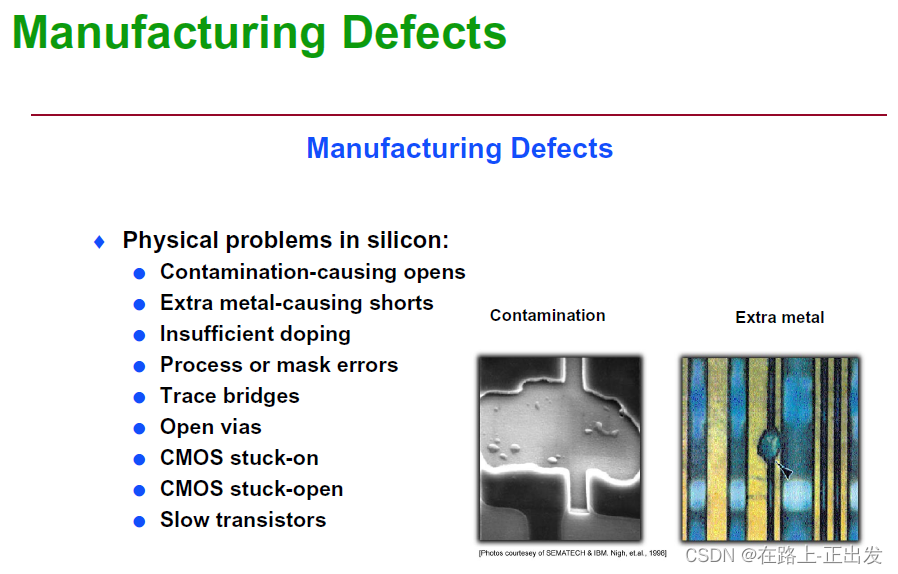

fallo de fabricación del chip

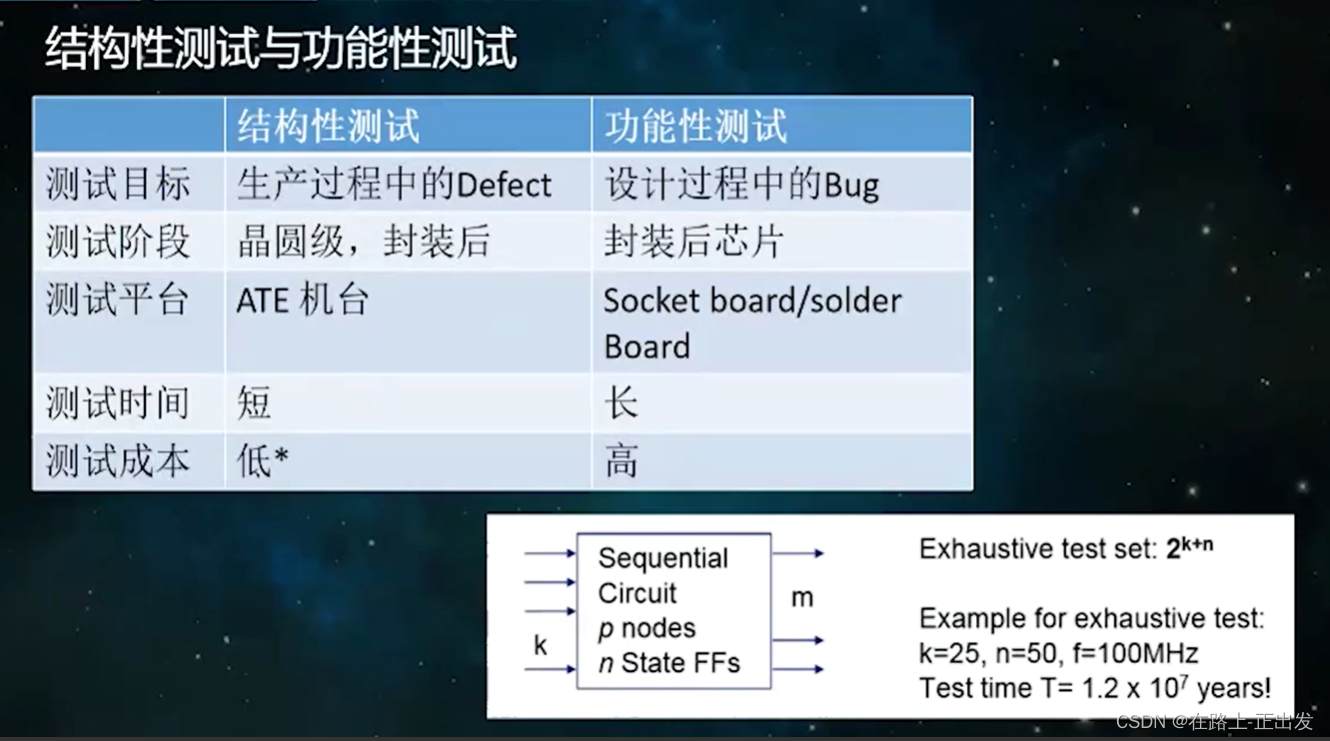

Pruebas estructurales y funcionales.

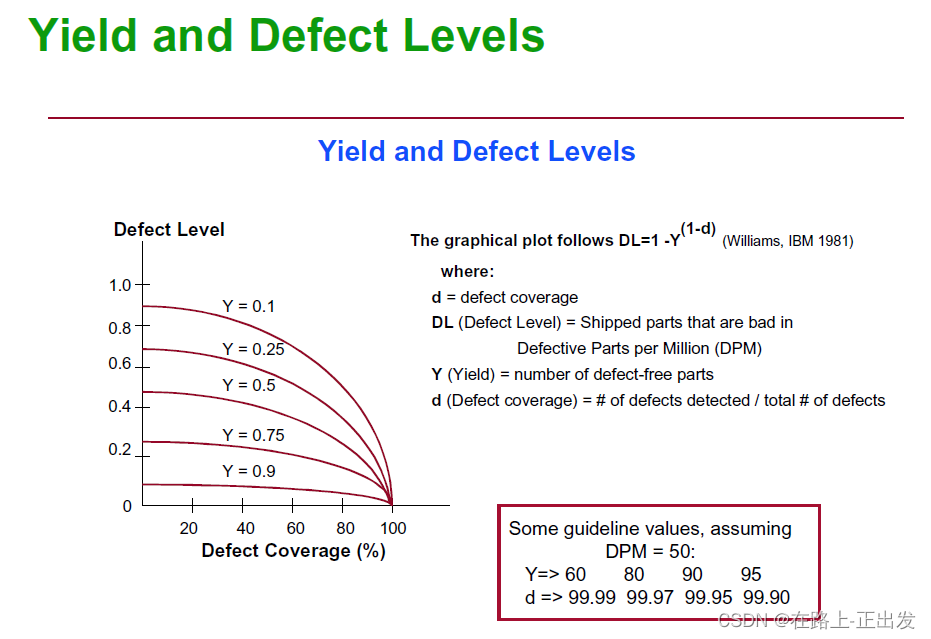

La relación entre rendimiento y calidad.

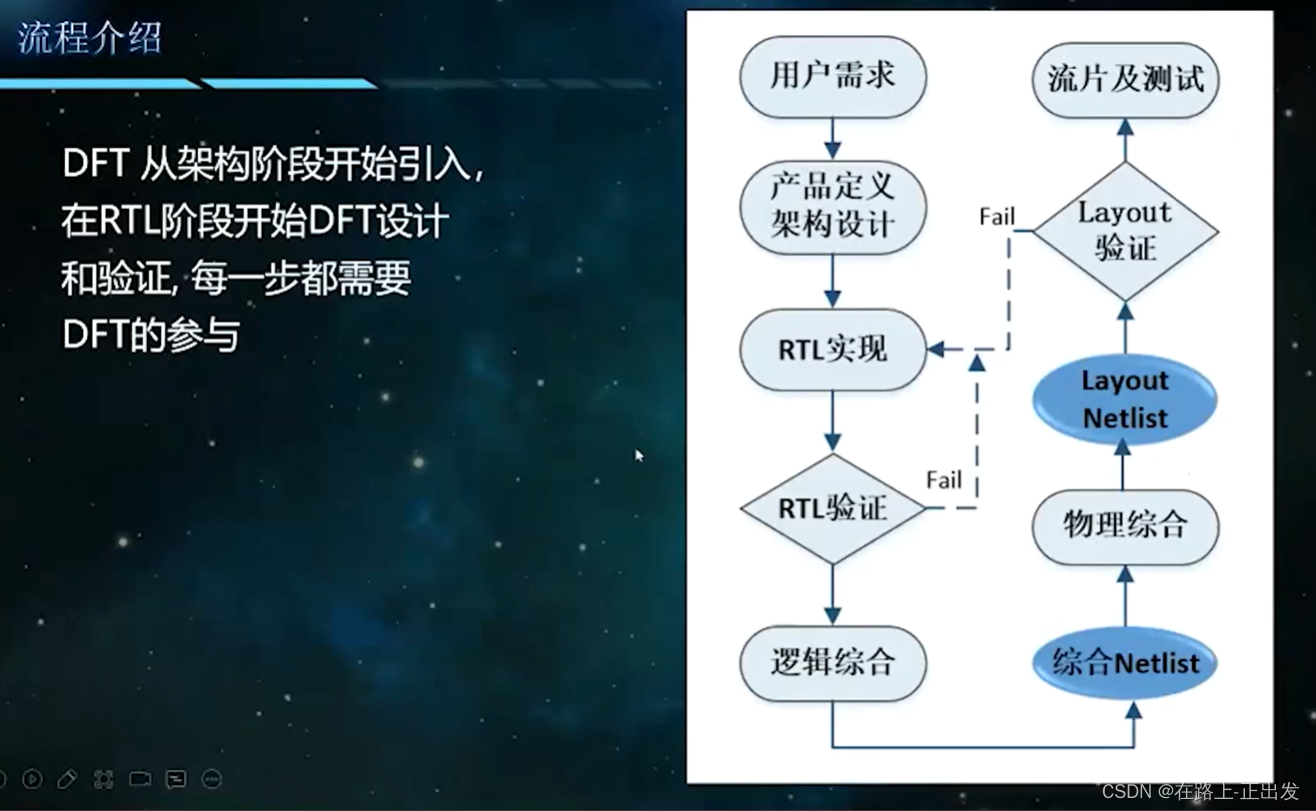

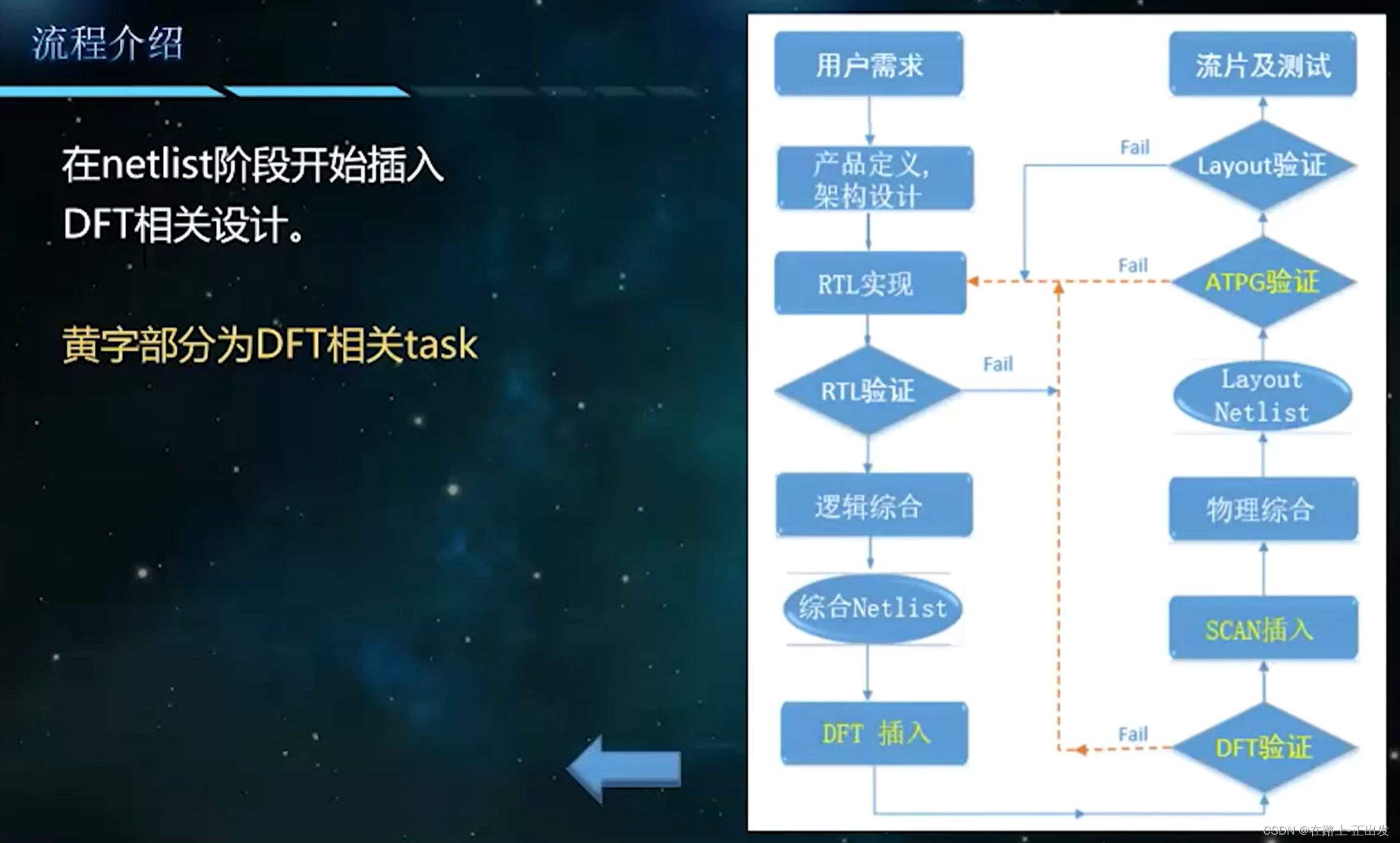

Flujo de diseño

DFT participa en todo el proceso:

Participación tardía del DFT:

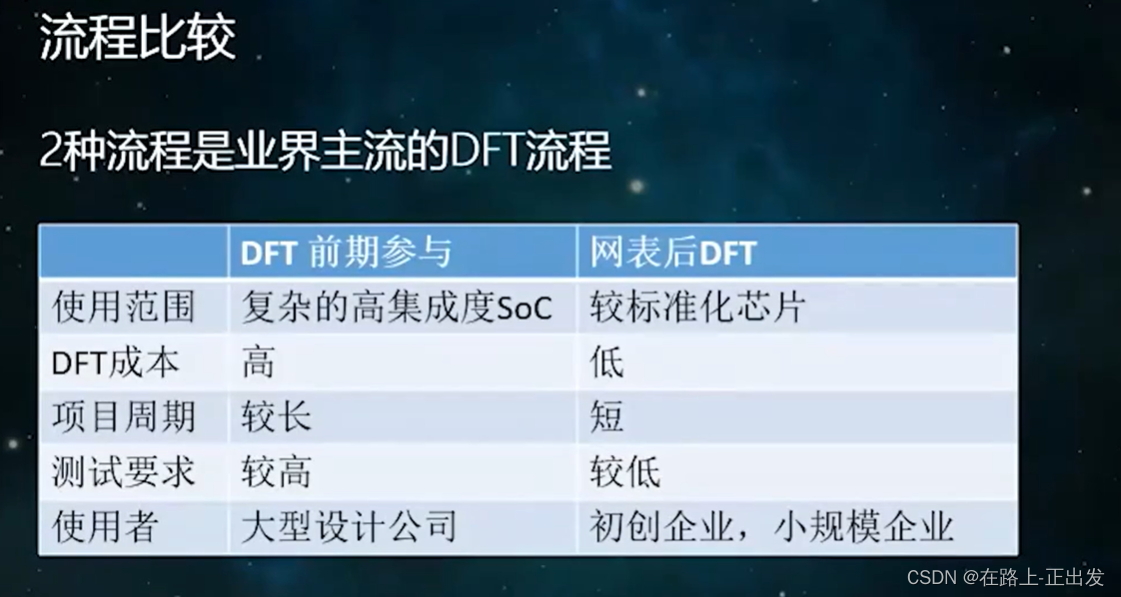

Compara los dos:

método de prueba

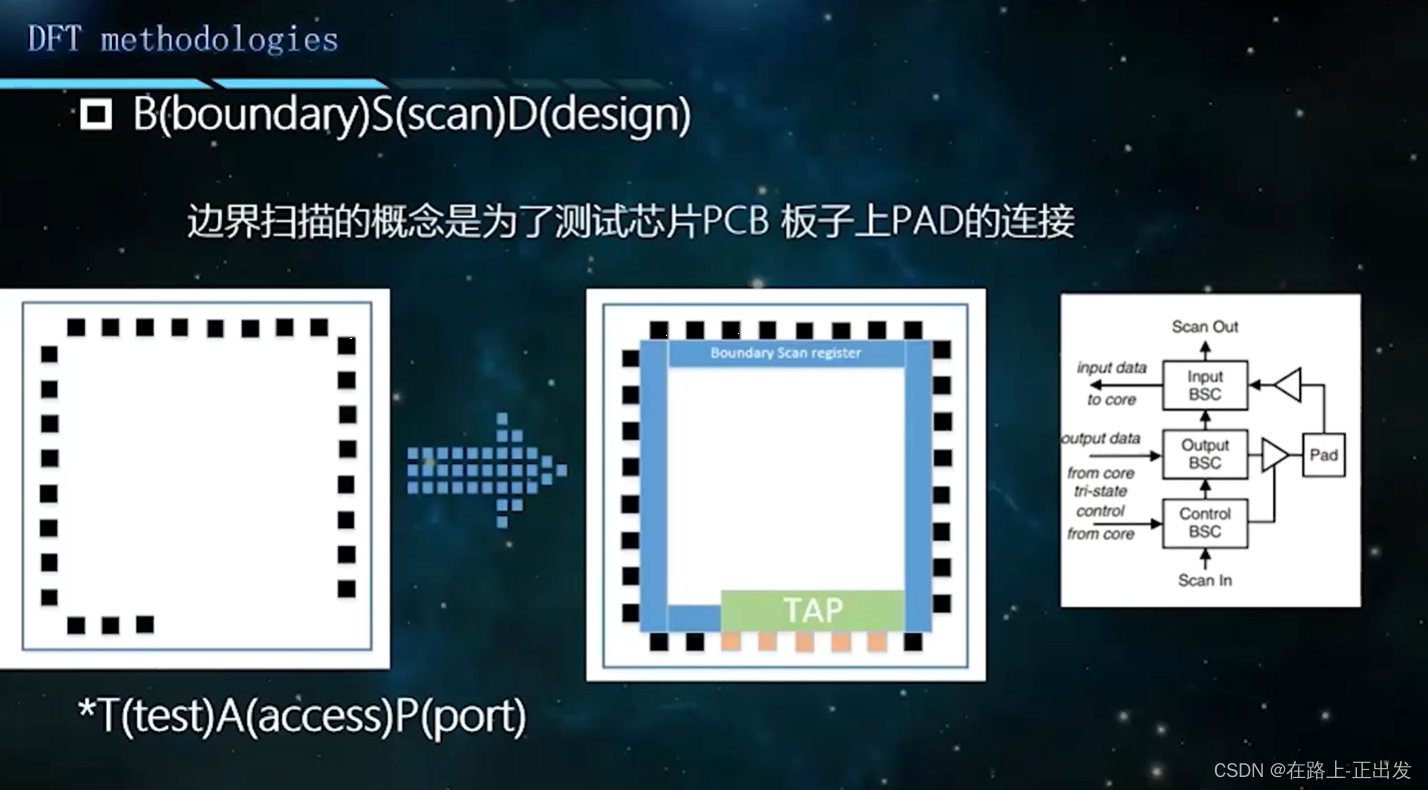

Exploración de límites:

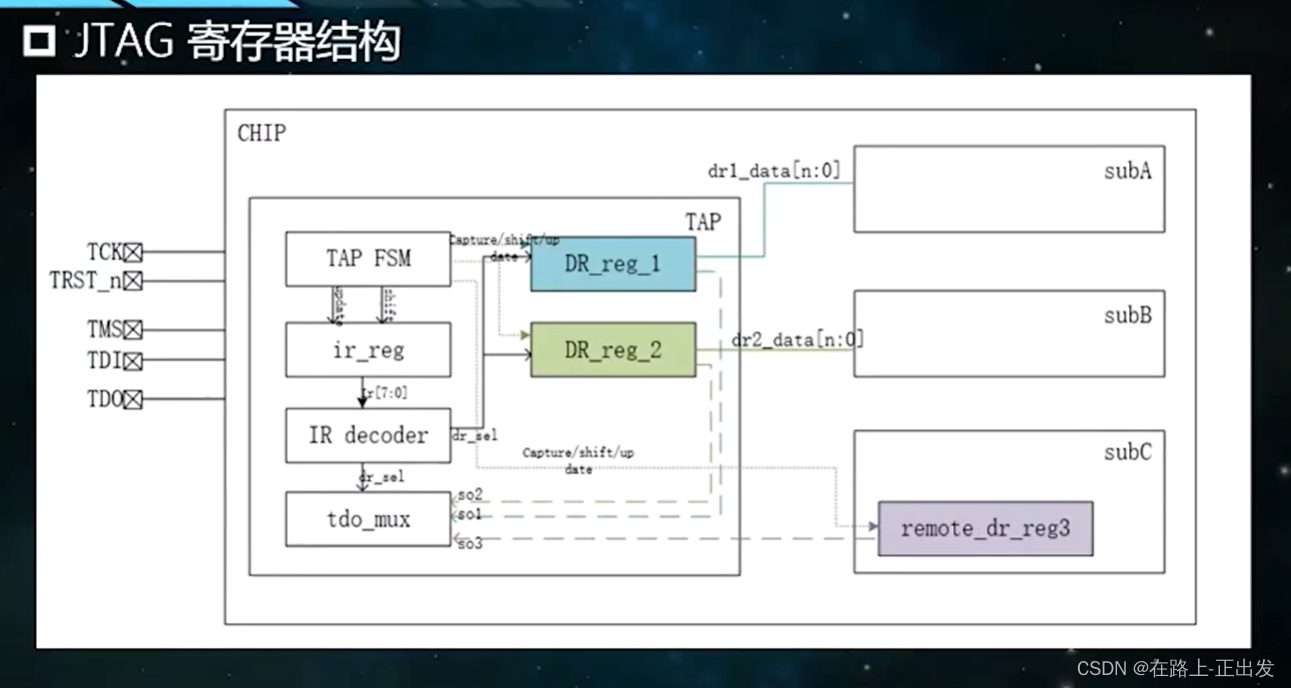

Estructura de registro JTAG

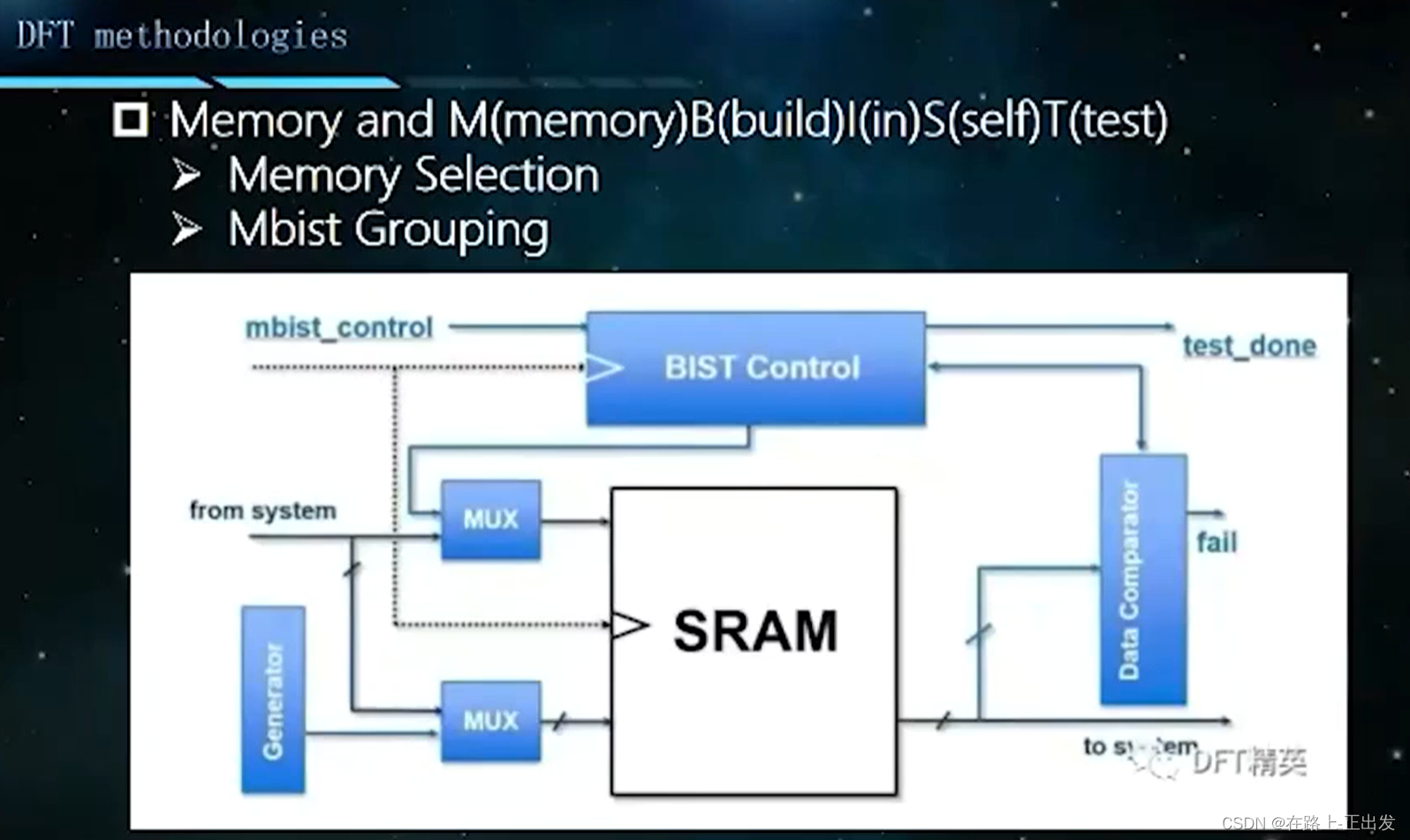

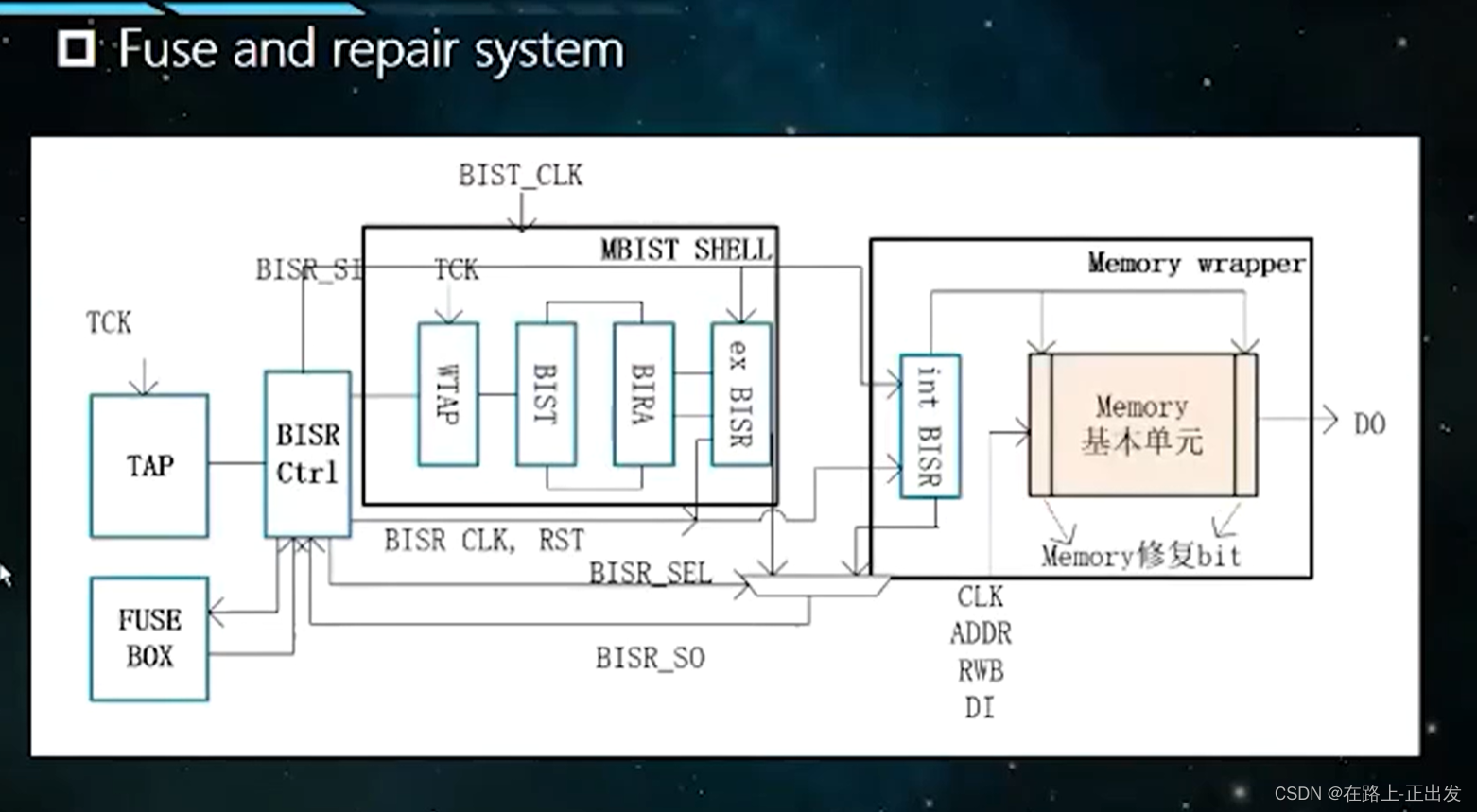

Estructura de prueba MBIST:

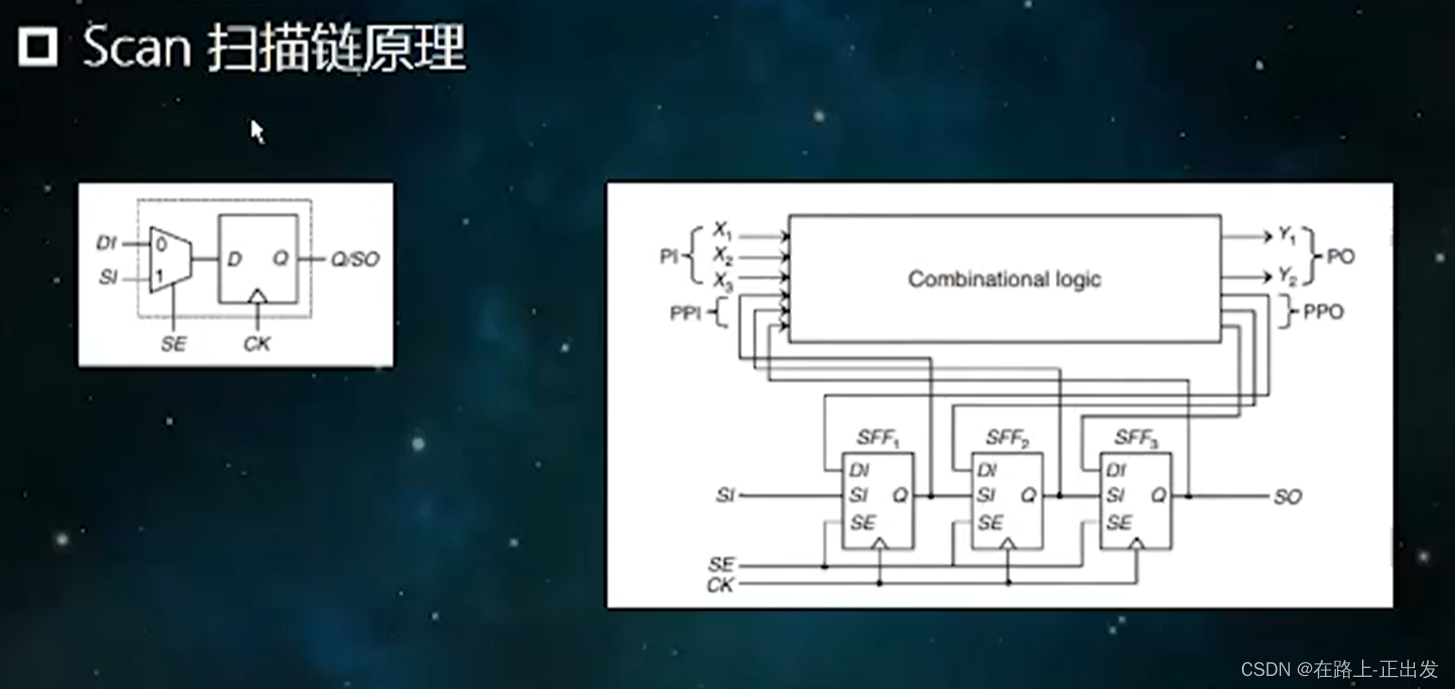

cadena de escaneo

Reemplace el flip-flop D ordinario por un flip-flop D con MUX para realizar la función del circuito de la cadena de escaneo.

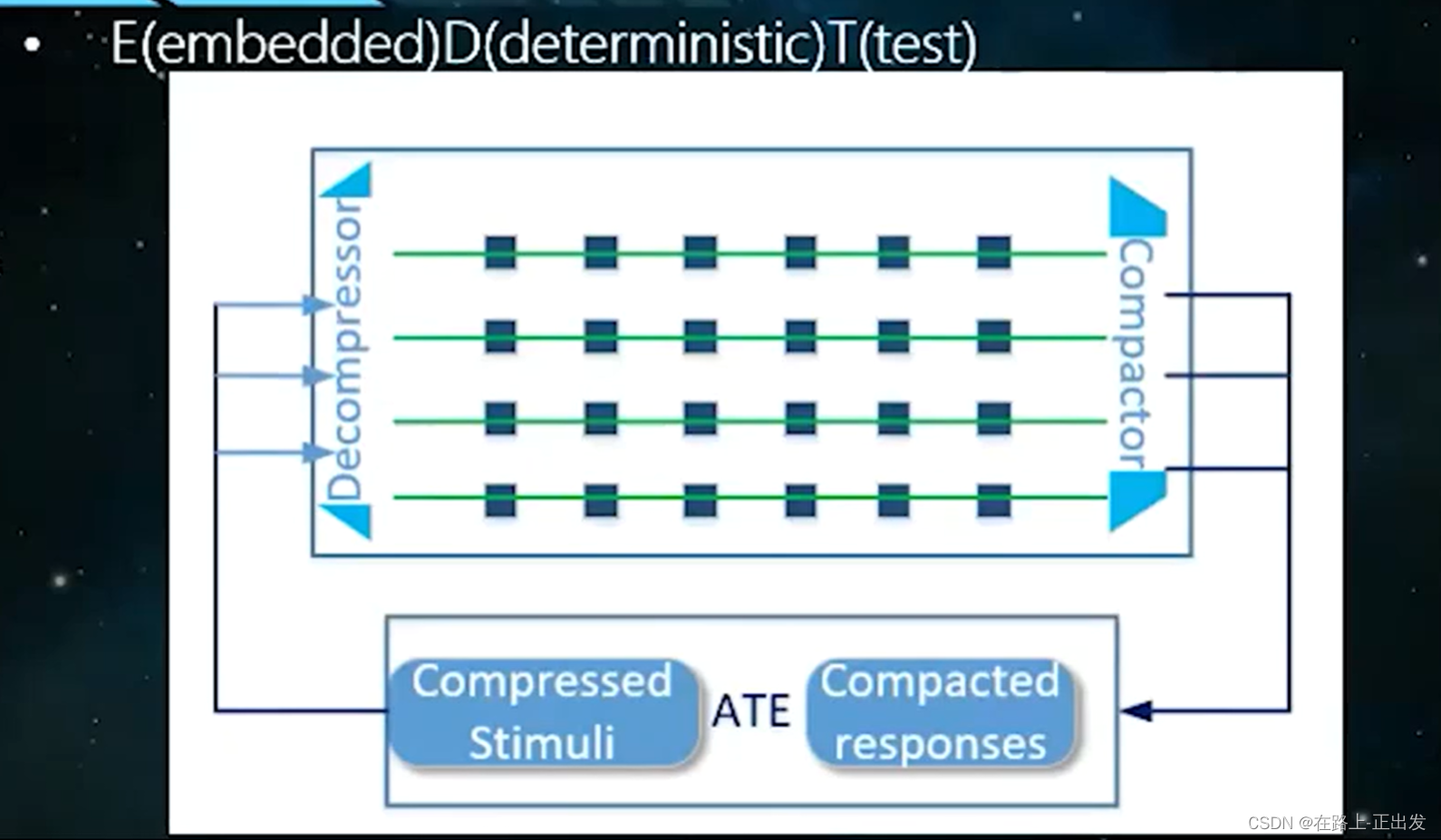

Estímulo/respuesta de compresión

En un circuito integrado grande, hay muchas funciones que deben probarse, pero hay pocas IO disponibles o la conexión de escaneo interno es muy larga, lo que resulta en un gran costo de tiempo de prueba.

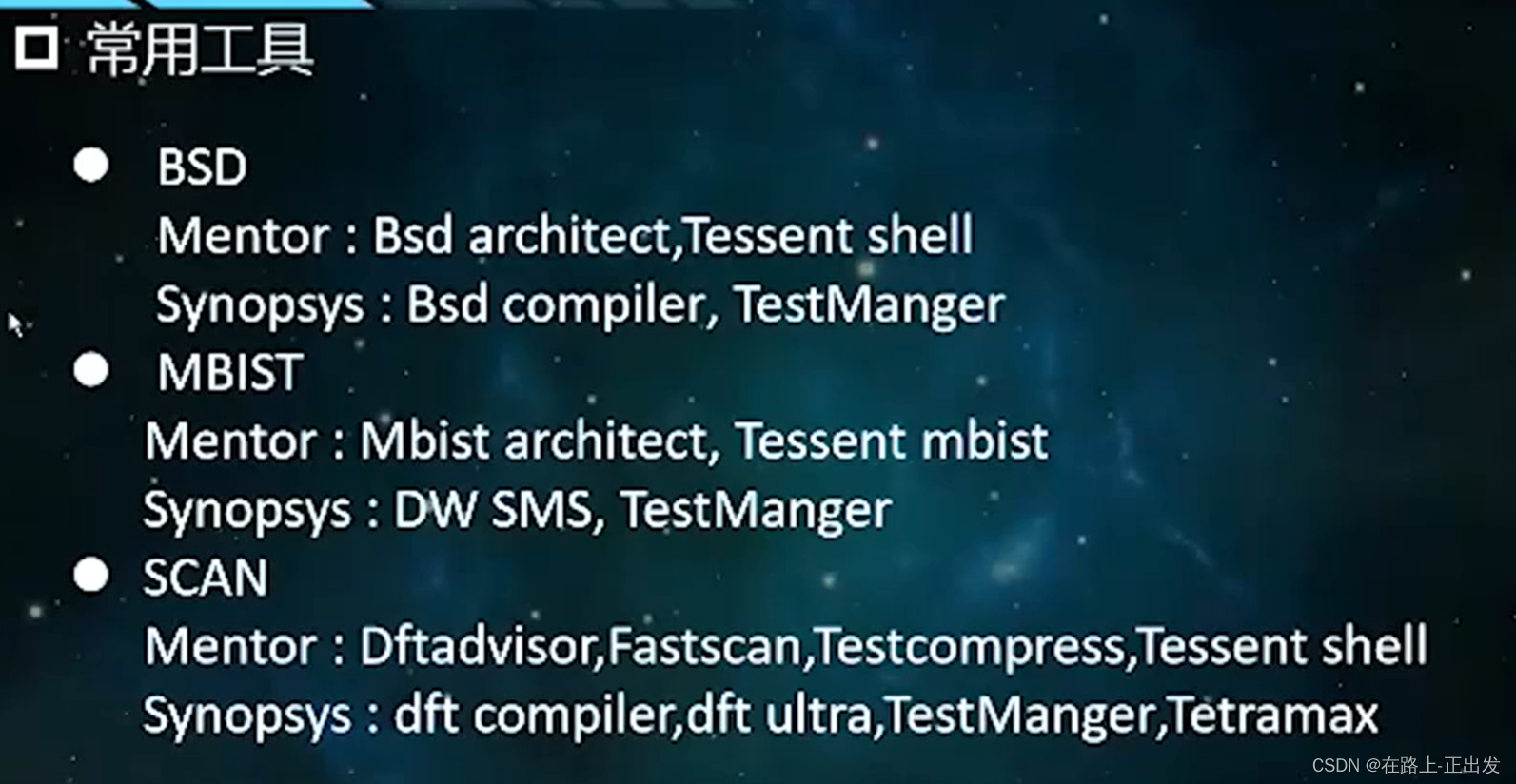

herramienta común

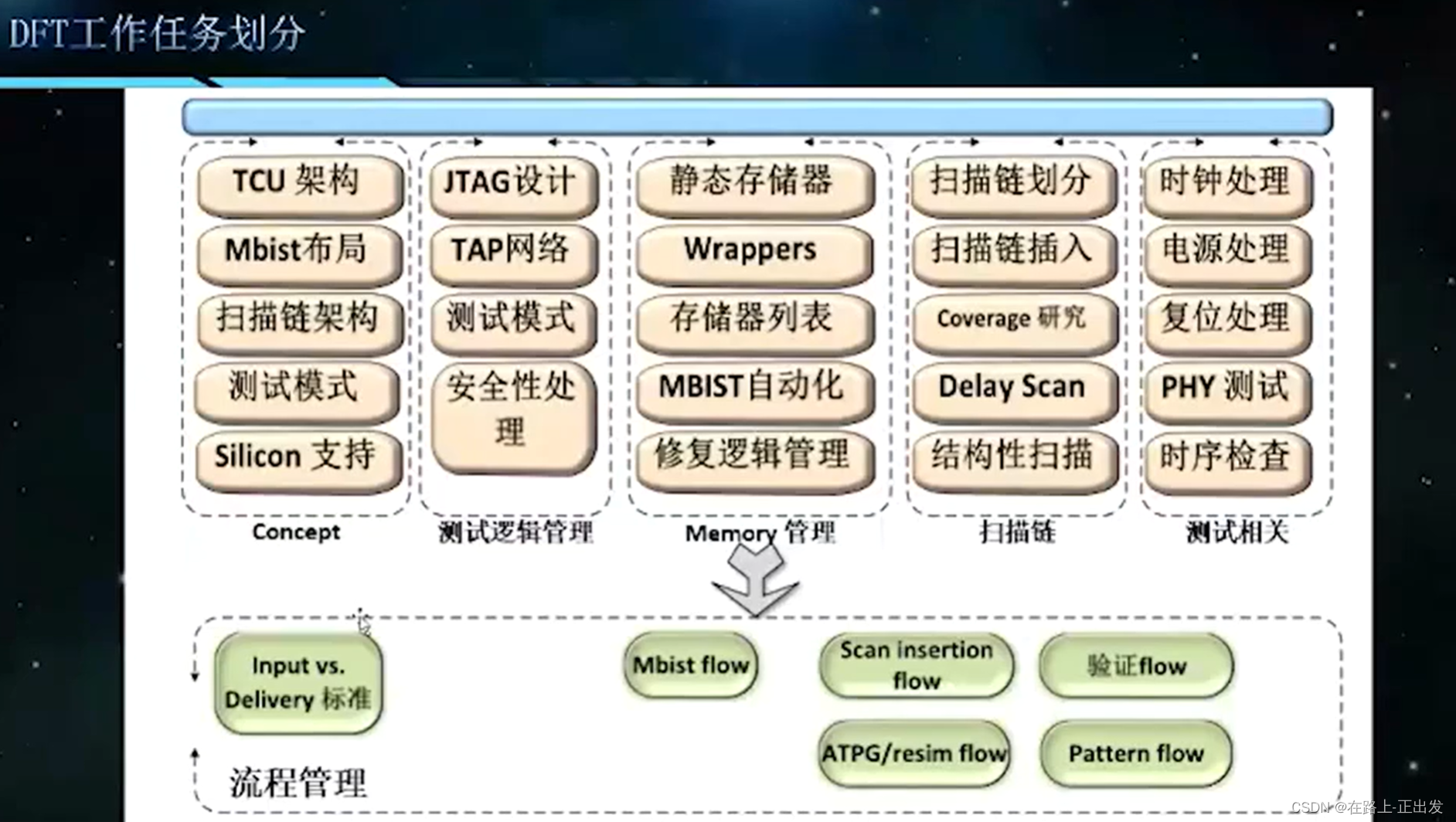

Asignación de tareas