Referencias para el contenido de este artículo:

"Charla interesante sobre el sistema operativo Linux " —— Liu Chao, Geek Time

Aplicación y análisis del código fuente " QEMU /KVM" - Li Qiang, Machinery Industry Press

¡Muchas gracias!

A través de los primeros 30 artículos de esta serie, el autor ha explicado algunos conocimientos básicos de QEMU. A partir de este capítulo, comenzamos oficialmente el análisis del código de cada componente hardware del sistema.

Lo primero que hay que presentar es, por supuesto, la máquina, es decir, la simulación de la placa base y el firmware. El archivo correspondiente es hw/core/machine.c. Pero antes de explicar el código, comencemos con la línea de comandos de QEMU. Un ejemplo de una línea de comando QEMU es el siguiente:

-machine pc-i440fx-trusty,accel=kvm,usb=offpci-i440fx en la línea de comandos es la arquitectura predeterminada para máquinas x86. Aquí hay una breve introducción a i440fx.

Conjunto de chips INTEL 440FX

Intel 440FX (i440fx) es un chip de placa base lanzado por Intel en 1996 para admitir Pentium II (Pentium 2), tiene una historia de más de 20 años y es una arquitectura relativamente clásica. Aunque QEMU ha podido admitir la simulación de la arquitectura q35 más avanzada, actualmente QEMU todavía usa la arquitectura i440fx de manera predeterminada.

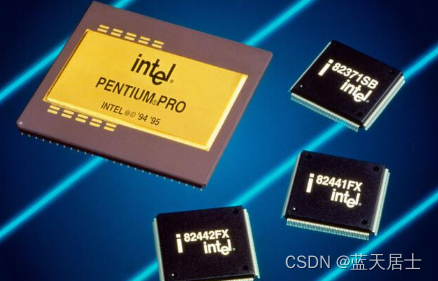

En ese momento, Intel no se relajó después de obtener grandes ganancias con el conjunto de chips de la serie TRITON, porque necesitaban producir un conjunto de chips más nuevo para igualar al PENTIUM PRO, por lo que nació el conjunto de chips 440FX. Este chipset es el primer chipset producido por Intel basado en la arquitectura SLOT 1, conocida como NATOMA. NATOMA consta de cuatro chips: 82441FX/82442FX/82371SB/82093AA. Entre ellos, el 82093AA es opcional y está empaquetado en 1*64-PIN PQFP, y los otros tres están empaquetados en 3*208-PIN PQFP. La función del chip 82093AA es que permite que el conjunto de chips 440FX admita dos CPU y admita el procesamiento APIC de E/S independiente multiproceso simétrico. NATOMA no tiene el problema de la limitación del rango de memoria CACHE, porque el caché L2 en el chip de la CPU PENTIUM PRO puede realizar la operación CACHE en toda la memoria. En cuanto a la gestión de la memoria, la NATOMA también ha hecho un gran progreso, puede admitir una capacidad de memoria de 1 GB. Desafortunadamente, sin embargo, carece de soporte para SDRAM. Además, 440FX adopta el controlador de disco duro PIIX3, admite control de bus y la velocidad máxima de transferencia de datos es PIO MODE 4/DMA MODE 2 (16,6 MB/S), también admite USB y PCI síncrono, y la velocidad de bus admitida es 60 /66MHZ.

El Intel 440FX consta de un North Bridge de dos chips. Los componentes principales son el puente PCI 82441FX y el controlador de memoria, y el acelerador de bus de datos 82442FX para el bus PCI.

El conjunto de chips utiliza el chip de puente sur PIIX3 82371SB, admite la interfaz DMA IDE maestra de bus de alta velocidad y USB, y actúa como un puente entre el bus PCI y el ISA.

La imagen física de la placa base y el chip central es la siguiente:

La estructura del conjunto de chips con i440fx como puente norte y piix3 como puente sur se muestra en la siguiente figura:

Diagrama de arquitectura Intel 440FX

Como se muestra en la figura anterior, el puente norte i440fx incluye PMC (puente PCI y controlador de memoria) y DBX (acelerador de bus de datos). La función del puente norte es conectar varios procesadores hacia arriba y conectar la memoria y el bus PCI hacia abajo. El bus PCI puede derivar un árbol de dispositivos PCI.

El puente sur pii3 se utiliza principalmente para conectar dispositivos de baja velocidad, incluidos controladores IDE, controladores USB, etc. Se pueden conectar varios dispositivos lentos al sistema a través del controlador, como discos duros, dispositivos USB, etc. (correspondientes al controlador). Southbridge también se conecta al bus ISA, a través del cual los dispositivos ISA heredados se pueden conectar al sistema.

Hay otro punto a tener en cuenta aquí, es decir, el APIC de E/S del controlador de interrupción está conectado directamente al procesador, y la interrupción del dispositivo se puede enrutar al procesador a través del APIC de E/S.

Si quieres saber qué pasó después, veamos el siguiente capítulo.