Tabla de contenido

1. Explicación detallada del principio y los pasos de uso del monitor de ECG

(1) Composición básica del sistema:

(2) Estructura y principio del monitor de ECG remoto portátil

(3) Estructura y principio del monitor de ECG portátil

Pasos de uso del monitor de ECG

2. Diseño de monitor de ECG portátil

2 Diseño de hardware del sistema

2.1 Circuito de búfer de entrada y diseño del circuito de preamplificador

2.2 Diseño del circuito de filtrado

2.3 Diseño del circuito del amplificador posterior

2.4 Diseño de circuito de subida de nivel

2.5 Diseño del circuito disparador Schmitt

3 Diseño de la parte del software del sistema

3.1 Breve introducción de LCD, teclado, temporizador y módulo AD

3.3 Resultados de visualización de ECG

3. Solución de monitor de ECG basada en la plataforma del sistema DSP

4. Desarrollo de un nuevo monitor de ECG integrado basado en ARM7

2. El principio de funcionamiento del sistema.

3. Diseño del módulo de hardware del sistema

3.1, circuito de acondicionamiento de señal

3.2 Procesador integrado y circuitos periféricos

3.2.2, memoria de programa del sistema Flash ROM y expansión SDRM

3.2.3, pantalla de cristal líquido LCD y módulo de teclado

3.2.4, diseño del módulo Ethernet

4. Diseño de software del sistema

4.1 Trasplante del sistema operativo uClinux embebido en S3C44B0X

4.2 Implementación de GUI integrada basada en S3C44B0X

4.3 Implementación del controlador RTL8019AS bajo uClinux

6. Circuito de control de accionamiento de motor ultrasónico basado en NiosⅡ

1 Diseño del controlador de accionamiento

1.1 Circuito de control de accionamiento

1.2.1 Construcción del sistema Nios Ⅱ

1.2.3 Módulo contador de pulsos

1.3 Modo de control del controlador de accionamiento

2.1 Investigación sobre la estabilidad de la velocidad del motor ultrasónico

2.2 Prueba de precisión de posicionamiento

1. Explicación detallada del principio y los pasos de uso del monitor de ECG

Con el desarrollo de la tecnología médica, los monitores de ECG son ampliamente utilizados en el monitoreo de condiciones clínicas . Al ver los parámetros fisiológicos monitoreados por él , además de proporcionar evidencia razonable y objetiva para el personal médico, es muy importante para la detección temprana de cambios en la condición y la prevención de complicaciones Ha jugado un importante papel de guía, permitiendo que el personal médico tome medidas de tratamiento efectivas y métodos de tratamiento para pacientes con condiciones cambiantes más rápido y mejor, y lograr el objetivo de garantizar la seguridad de los pacientes. Es precisamente porque este tipo de equipo facilita el seguimiento del estado del paciente por parte del personal médico, y el tratamiento del paciente puede ser más rápido y eficaz. Por lo tanto, es ampliamente utilizado en varios hospitales. Los ingenieros que se dedican a la industria de la electrónica médica pueden tener una buena comprensión de este aspecto del conocimiento, y algunos pueden tener un conocimiento a medias, incluido lo que es un monitor de ECG, sus principios básicos , principios de funcionamiento, pasos de uso correctos y precauciones de uso. etc. Vamos a conocer en profundidad este tipo de equipos a partir de sus principios básicos y pasos de uso.

¿Qué es un monitor de ECG ?

¿Qué es un monitor de ECG? Es una aplicación importante de un monitor (qué es un monitor). Como dispositivo de uso común en hospitales, puede monitorear simultáneamente el ECG, la respiración, la presión arterial, la temperatura corporal, el pulso y otros parámetros fisiológicos del paciente. Instrumentación médica práctica para pruebas y mediciones de precisión . Muestra intuitivamente los datos que deben detectarse y monitorearse en el monitor para que el personal del hospital juzgue y trate a los pacientes. Cada parámetro fisiológico que se puede monitorear generalmente se establece con un valor de seguridad para referencia y comparación.Si el valor real del paciente no está dentro del valor de seguridad, se emitirá una alarma automáticamente.

Principio del monitor de ECG

(1) Composición básica del sistema:

(A) osciloscopio de rayos catódicos

(B) registrador de ECG

(C) Monitor de presión

(D) Monitor de respiración

(E) Monitor de temperatura corporal

(F) Composición del sistema de procesamiento informático

La actividad electrocardiográfica se transmite al procesador a través del cable conductor de ECG, y el sensor de presión convierte la presión arterial en una señal eléctrica y la transmite al procesador. La actividad respiratoria es causada por la exhalación y la inhalación, y el cambio de resistencia torácica se transmite al procesador a través del cable de ECG y la actividad de ECG al mismo tiempo. El procesador amplifica la señal eléctrica del cuerpo del paciente y, después de procesarla por la microcomputadora , se convierte en una salida de forma de onda y una señal digital.La salida se muestra en la pantalla del osciloscopio de rayos catódicos a través del sistema de visualización fotoeléctrica, y su principio de funcionamiento es una referencia importante para el diseño del monitor de ECG.

(2) Estructura y principio del monitor de ECG remoto portátil

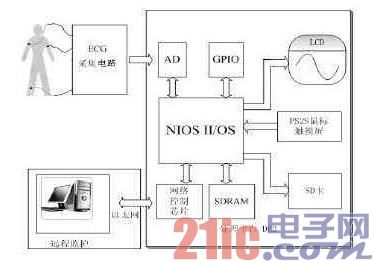

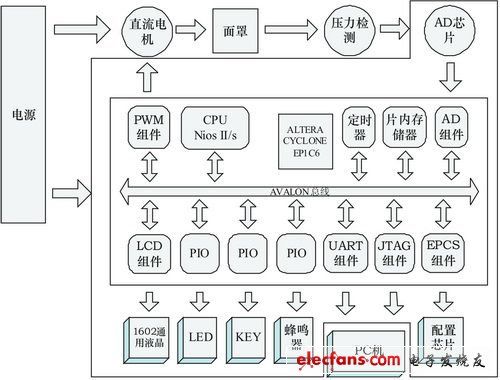

Se compone principalmente de cuatro módulos clave: el módulo de acondicionamiento y adquisición frontal de la señal de ECG, el módulo de procesamiento y almacenamiento de la señal de ECG, el módulo de visualización de datos y el módulo de control de transmisión remota.La estructura funcional del sistema se muestra en la figura. Su plataforma de hardware adopta el chip FPGA CycloneII 2C35, adopta la tecnología SOPC para integrar el procesador de núcleo blando NiosII, la memoria, la interfaz funcional y el puerto de E/S de expansión, etc. en un chip FPGA y expande periféricamente la placa de adquisición de datos ECG, la red y la pantalla LCD , La arquitectura de hardware del sistema se realiza mediante pantalla táctil/teclado, tarjeta de memoria SD y otro hardware, y tiene una interfaz de E/S ampliable, que es conveniente para la futura actualización y expansión de la función del sistema.

Diagrama de estructura y principio del monitor de ECG remoto portátil

(3) Estructura y principio del monitor de ECG portátil

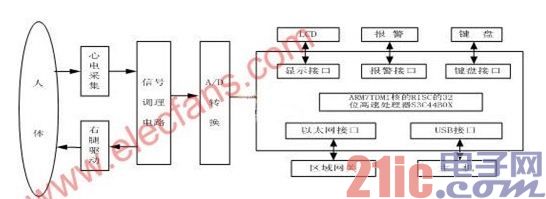

El módulo de hardware del sistema incluye principalmente: circuito de acondicionamiento de señal (amplificador, filtro de paso de banda, filtro de muesca), procesador incorporado y circuito periférico (conversión A/D, Flash ROM y expansión SDRM , pantalla de cristal líquido LCD y módulo de teclado, módulo Ethernet) en dos partes Su estructura y diagrama de principios son los siguientes:

Diagrama de estructura y principio del monitor de ECG remoto portátil

Después de que la señal de ECG se recoge de los brazos izquierdo y derecho de la persona a través de electrodos especiales, se envía al circuito de acondicionamiento de señal , en primer lugar amplificada por el preamplificador , filtrada por el filtro de paso alto para filtrar la señal de CC y baja -interferencia de línea de base de frecuencia, amplificada por el amplificador posterior a la etapa , y luego pasada a través del filtro El filtro filtra aún más la interferencia de frecuencia de potencia de 50 HZ , y la señal de ECG que cumple con los requisitos se obtiene después del filtro de paso bajo y se envía a el ADC del terminal de entrada de señal analógica para conversión A/D de alta precisión. También introdujimos un circuito de conducción de la pierna derecha y un circuito de detección de salida en el circuito.

Pasos de uso del monitor de ECG

(1) monitoreo de ECG

En la actualidad, el color del telegrama del cable conductor del electrocardiograma se ha estandarizado para reducir la confusión, y los electrodos positivo, negativo y de tierra se colocan de acuerdo con el diagrama.

(2) El control de presión debe realizar las siguientes operaciones para obtener datos y formas de onda correctos

(A) Colocación del transductor a nivel de la aurícula derecha

(B) Paso de ajuste a cero, varios tipos de monitores están equipados con un botón de cero.

(C) Toda la tubería de medición de presión se llena con solución salina de heparina para evitar que se obstruyan los coágulos de sangre, y el sistema de tubería no debe contener burbujas de aire.

(D) Enjuague regularmente con solución salina con heparina o enjuague continuamente con una microbomba a una velocidad de 2 ml/h para mantener la permeabilidad de la tubería.

(2) El procedimiento operativo es el siguiente:

(A) Conecte la fuente de alimentación del monitor de ECG.

(B) Coloque al paciente en posición supina o semirrecostada.

(C) Encienda el interruptor principal.

(D) Limpie la piel del tórax del paciente donde está conectado el electrodo con una bola de algodón con solución salina.

(E) Pegue los electrodos, conecte el cable conductor de ECG y el oscilograma de ECG aparecerá en la pantalla

(F) Ate el brazalete hasta dos dedos por encima de la fosa del codo. Presione Medir—Establecer límite de alarma—Medir tiempo.

epílogo

Con el desarrollo de la tecnología médica moderna y la tecnología de monitoreo médico actual, los monitores de ECG se han convertido en una categoría indispensable de equipos electrónicos médicos y desempeñan papeles cada vez más importantes en los hospitales.Tiene las ventajas de una operación simple, es fácil de ver y registrar , puede monitorear muchos parámetros fisiológicos y tiene una amplia gama de aplicaciones y lugares , y ha atraído mucha atención en aplicaciones de tratamiento médico.

2. Diseño de monitor de ECG portátil

Resumen: Basado en la investigación sobre la tecnología de adquisición y procesamiento de señales de ECG , se diseña un sistema de monitoreo de ECG portátil en tiempo real y de baja potencia en combinación con la microcomputadora de un solo chip MSP430F149. Primero, el circuito de hardware se usa para recopilar, amplificar, filtrar y eliminar el ruido de la señal de ECG , y luego usar MATLAB para realizar la simulación del filtrado digital y eliminar el ruido de la señal de ECG.Finalmente, el programa de un solo chip se escribe y depura, principalmente para completar la prueba de frecuencia cardíaca, registro de ECG y análisis simple y otras funciones.

Dirección de citación de este artículo: Diseño de monitor de ECG portátil

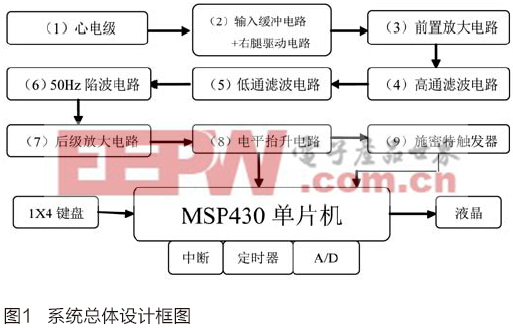

1 Diseño general del sistema

La señal de ECG es una señal fisiológica muy débil, que se altera fácilmente por el entorno circundante. Para que el ECG sea más preciso y claro, el sistema utiliza una combinación de filtrado analógico y filtrado digital para procesar la señal del ECG. La señal de ECG se recopila a través del electrodo cardíaco y la señal de ECG recopilada ingresa al preamplificador a través del circuito de búfer de entrada. Después de amplificar el preamplificador, la señal ingresa al circuito de procesamiento. En el circuito de procesamiento, pasa por paso alto, paso bajo, muesca de 50 Hz, amplificación posterior a la etapa, aumento de nivel, disparador Schmitt y finalmente ingresa al microcontrolador para su procesamiento . . Antes del procesamiento de un solo chip, con la ayuda de la plataforma de simulación MATLAB, primero realice el filtrado FIR y el procesamiento de muesca en la señal de ECG en la base de datos de investigación de arritmias (MIT-BIH) proporcionada por el Instituto de Tecnología de Massachusetts, y obtenga la C de el mejor filtro digital codigo. Luego, el microcontrolador se controla mediante programación para completar las siguientes funciones: sincronización, interrupción, medición de frecuencia cardíaca, conversión AD, muestreo, filtrado digital, eliminación de ruido, visualización de electrocardiograma y análisis simple. El diagrama de bloques de diseño general del sistema se muestra en la Figura 1.

2 Diseño de hardware del sistema

El equipo electrocardiográfico médico a gran escala puede usar una variedad de métodos de derivación para obtener señales electrocardiográficas, y varias señales obtenidas se pueden mostrar en tiempo real en el monitor. Teniendo en cuenta la comodidad de los dispositivos portátiles, el sistema utiliza cables estándar para recopilar una señal de ECG, es decir, se utilizan tres electrodos para obtener señales de ECG. Teniendo en cuenta las características de la señal de ECG, la parte del circuito de hardware debe cumplir con los siguientes requisitos:

(1) Ganancia. El rango de amplitud de una señal de ECG normal es de 10 μV a 4 mV, y el valor típico es de 1 mV. El diseño convencional de la ganancia del amplificador de ECG requiere que cuando la entrada sea de 1 mV, el nivel de salida debe alcanzar aproximadamente 1 V, por lo que el factor de amplificación del amplificador de ECG debe ser de aproximadamente 1000 veces.

(2) Respuesta de frecuencia. El rango de espectro de la señal de ECG es de 0,05 a 100 Hz, y la energía del espectro se concentra principalmente entre 0,05 y 40 Hz, por lo que el rango de la banda de frecuencia debe ser de al menos 0,05 a 40 Hz. Por lo tanto, se debe diseñar un filtro de paso de banda para comprimir el paso de banda.

(3) Alta impedancia de entrada. La señal de ECG obtenida a través de los electrodos de ECG es muy débil y el cuerpo humano tiene una gran impedancia de fuente, por lo que se debe aumentar la impedancia de fuente del amplificador para garantizar la estabilidad de la ganancia.

(4) Alta relación de rechazo de modo común. El contacto entre los electrodos y la piel y la interferencia de la red eléctrica provocarán una interferencia de modo común. Si no se diseña un circuito con una alta relación de rechazo de modo común, la débil señal de ECG se verá superada.

(5) Bajo nivel de ruido y baja deriva. Debido a la alta ganancia, el ruido y la deriva también afectarán la adquisición de señales de ECG. Por lo tanto, para obtener señales de ECG de alta calidad, deben usarse componentes de bajo ruido y deben diseñarse circuitos de deriva de baja temperatura.

(6) Alta seguridad. El uso de cualquier instrumento debe tomar la seguridad del cuerpo humano como un indicador importante y evitar descargas eléctricas al cuerpo humano.

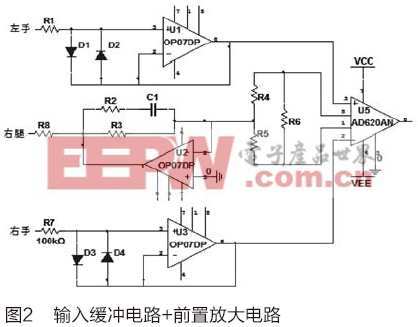

2.1 Circuito de búfer de entrada y diseño del circuito de preamplificador

En todo el diseño del circuito, el circuito de entrada adopta un circuito de etapa intermedia. En términos de amplificación de señal, se utiliza un método de amplificación de dos etapas. El circuito de búfer de entrada puede aumentar la impedancia de entrada de todo el circuito amplificador y reducir la impedancia de salida. De esta forma, se puede obtener una señal de mayor amplitud en la siguiente red de resistencias de adaptación. El circuito del preamplificador adopta AD620 como dispositivo central.

AD620 tiene las siguientes características:

(1) AD620 tiene bajo costo, alta precisión, alta impedancia de entrada y alta relación de rechazo de modo común. Solo necesita cambiar la resistencia Rg (R6 en la Figura 2) para realizar el cambio de la ganancia de amplificación entre 1-1000;

(2) AD620 es de tamaño pequeño y bajo consumo de energía, por lo que es muy adecuado para equipos portátiles alimentados por batería;

Dirección de citación de este artículo: Diseño de monitor de ECG portátil

(3) AD620 tiene alta precisión, corriente de polarización de entrada pequeña, voltaje de compensación bajo y deriva de compensación baja, lo que lo convierte en una opción ideal para sistemas de adquisición de datos.

En una palabra, las características del AD620 de bajo ruido, baja corriente de polarización de entrada y bajo consumo de energía cumplen con los requisitos de este sistema, y la distorsión de la señal después de la amplificación del AD620 es muy pequeña, lo cual es muy adecuado para la aplicación de ECG (electrocardiograma ) . Circuito de simulación de diseño que se muestra en la Figura 2. En la figura, el pin 3 es el terminal de entrada positivo del amplificador, conectado a la señal de entrada del brazo izquierdo; el pin 2 es el terminal de entrada negativo del amplificador, conectado a la señal de entrada del brazo derecho; el pin 7 está conectado a +3V/+5V El voltaje de trabajo de los 4 pines es -3V/-5V; los 4 pines inactivos están conectados a tierra, esto se hace para mejorar el rendimiento antiinterferencias de los dispositivos sensibles y luego mejorar la capacidad antiinterferencias de todo el sistema; entre l y 8 pines Entre la resistencia externa Rg (Figura 2 R6), al cambiar el tamaño de la resistencia puede ajustar la ganancia de amplificación. La relación entre la resistencia Rg y la ganancia G es como la fórmula (1):

Según la experiencia, la ganancia del preamplificador es generalmente de 8 a 10 veces para evitar la saturación del circuito del preamplificador. En este sistema, se conecta una resistencia de 5,1 kΩ entre los pines 1 y 8, de modo que el preamplificador tenga un aumento de 10 veces.

2.2 Diseño del circuito de filtrado

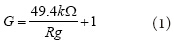

De acuerdo con los requisitos de respuesta de frecuencia, el diseño del filtro se muestra en la Figura 3.

Los parámetros del circuito del filtro de paso alto son:

Frecuencia propia:

2.3 Diseño del circuito del amplificador posterior

Dado que se requiere que el aumento de voltaje total del amplificador de señal de ECG sea 1000 veces, y el aumento de etapa previa es 10, el aumento de voltaje del amplificador de etapa posterior es 100 para cumplir con los requisitos.

Dirección de citación de este artículo: Diseño de monitor de ECG portátil

Como se muestra en la Figura 4, la ampliación:

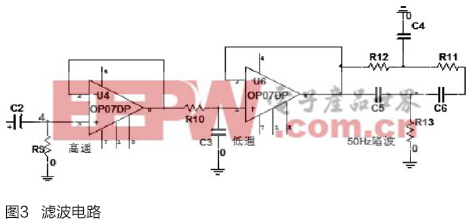

2.4 Diseño de circuito de subida de nivel

La señal de ECG amplificada y filtrada por el circuito analógico es una señal de CA, y el rango de conversión de la microcomputadora de un solo chip de la serie MSP430 es una señal de voltaje positivo (0 ~ 3,3 V), por lo que es necesario aumentar la señal analógica por encima 0V y convertir la señal bipolar en una señal de polaridad única. El diseño del circuito se muestra en la Figura 5.

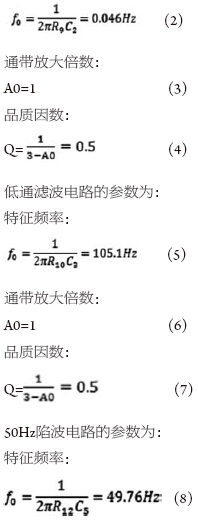

2.5 Diseño del circuito disparador Schmitt

Después de que la señal de ECG se amplifique 1000 veces, el valor máximo puede alcanzar los 4 V como máximo, y el disparador Schmitt se puede usar para transformar la forma de onda para convertir la señal de ECG en una onda rectangular. La onda rectangular tendrá un flanco descendente y un flanco ascendente, siempre que se llame a la interrupción del flanco descendente o ascendente en el microcontrolador , se puede registrar el número de latidos del corazón. El disparador Schmitt está construido sobre la base del temporizador 555. El diseño del circuito se muestra en la Figura 6.

3 Diseño de la parte del software del sistema

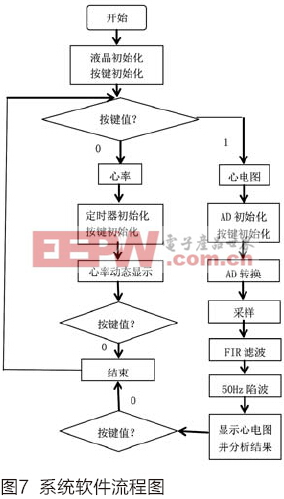

El diagrama de flujo del software del sistema se muestra en la Figura 7. En primer lugar, el menú de funciones se muestra en el cristal líquido de la microcomputadora de un solo chip , y se proporcionan dos opciones de funciones para el usuario: medición de frecuencia cardíaca y registro de electrocardiograma . Después de ingresar a la interfaz de medición de la frecuencia cardíaca, inicie el temporizador y comience la grabación. El valor de la frecuencia cardíaca se mostrará después de registrar 4 latidos. Después de cada pantalla, el registro se actualizará para mostrar el resultado nuevamente, principalmente para que el resultado sea más preciso. . Durante el período de registro, puede presionar el botón para finalizar la medición y regresar al menú principal directamente después de completar la prueba de frecuencia cardíaca. Después de ingresar a la página de grabación de ECG , inicie la inicialización de AD, el sistema completa automáticamente la conversión de AD, la extracción de valores, el filtrado FIR y finalmente muestra el ECG . Después de mostrar el ECG, el usuario puede volver al menú principal presionando la tecla .

3.1 Breve introducción de LCD, teclado, temporizador y módulo AD

Dirección de citación de este artículo: Diseño de monitor de ECG portátil

MSP430F149 proporciona dos interfaces LCD: interfaz LCD 1602 e interfaz LCD 12864. Debido a que la interfaz del cristal líquido 1602 es pequeña, no es fácil mostrar el ECG , por lo que se utiliza el cristal líquido 12864. La inicialización del cristal líquido se puede completar escribiendo instrucciones al controlador.

La placa de desarrollo MSP430F149 viene con 4 botones, que están conectados a P1.0-P1.3 de forma predeterminada. El principio del programa de escaneo de teclado 1X4 es relativamente simple. Primero, dé a estos cuatro botones un nivel alto y luego detecte el nivel del puerto P1.0-P1.3. Una vez que se presiona una tecla, el nivel del puerto correspondiente cambiará A través del Nivel de detección de programa, para que sepas qué tecla se pulsa.

Hay tres temporizadores en MSP430F149: temporizador de vigilancia, temporizador A y temporizador B. Aquí, se utiliza el temporizador A. El temporizador A tiene las siguientes características: conteo/temporizador de 16 bits, 4 modos en total; puede elegir configurar la fuente del reloj; múltiples registros de captura/comparación; latches de entrada/salida asíncronos; registros de vector de interrupción, que pueden decodificarse rápidamente Interrupción generado por el temporizador A.

El módulo ADC12 integrado dentro de MSP430F149 puede realizar la conversión A/D. El módulo ADC12 es un módulo de conversión A/D de precisión de 12 bits, que tiene las características de alta velocidad y versatilidad.

3.2 Diseño del filtro FIR

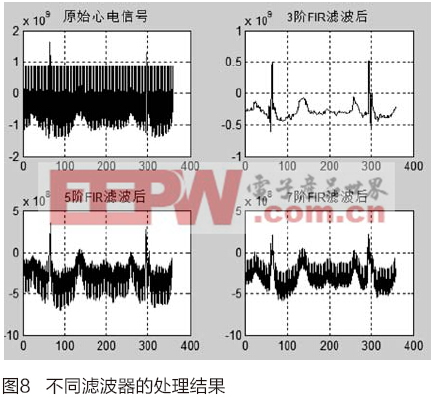

Filtre la señal de ECG con la ayuda de la plataforma MATLAB . Importe la señal de ECG original en MATLAB , diseñe diferentes órdenes de filtros FIR, procese la señal de ECG original y compare los resultados. El resultado del procesamiento del filtro se muestra en la Fig. 8, es obvio elegir el filtro FIR de tercer orden.

3.3 Resultados de visualización de ECG

Después de depurar el circuito de hardware y escribir el programa de software, la señal de ECG que se muestra en la Figura 9 se obtiene en la pantalla LCD.

4. Conclusión

El sistema diseña un electrocardiógrafo portátil basado en la microcomputadora de un solo chip . Una gran cantidad de experimentos y aplicaciones han demostrado que la parte del circuito de hardware puede completar con precisión la adquisición, amplificación, filtrado y otros procesos de la señal; la parte del software puede medir y mostrar con precisión la frecuencia cardíaca con la ayuda de la plataforma operativa MSP430 y el programa de procesamiento de señales MATLAB , pero no está en la función de mostrar ECG Debido a que el sistema es de tamaño pequeño, bajo costo, fácil de usar y preciso en los datos de medición, puede proporcionar una función de monitoreo cardíaco para las personas.

3. Solución de monitor de ECG basada en la plataforma del sistema DSP

Solución de monitor de ECG basada en la plataforma del sistema DSP

4. Desarrollo de un nuevo monitor de ECG integrado basado en ARM7

Resumen : Este documento presenta el diseño de software y hardware de un nuevo tipo de monitor de ECG portátil. El microprocesador de bajo consumo de 32 bits basado en el núcleo ARM se utiliza como núcleo de control del sistema. El sistema adopta el sistema operativo integrado uClinux con código abierto. código para realizar ECG La visualización en tiempo real y el control remoto de las señales tiene las ventajas de ligereza, ahorro de energía, funciones potentes, seguridad y estabilidad.

Palabras clave : ECG, ARM uClinux, pantalla de cristal líquido, protocolo TCP/IP

1. Introducción

La enfermedad cardiovascular es en la actualidad la enfermedad más dañina para el ser humano, siendo el electrocardiograma el principal medio y base para el control, diagnóstico y prevención de dichas enfermedades. Debido a que el monitor de ECG tradicional basado en una plataforma de PC es costoso, voluminoso, incómodo de mover y se concentra principalmente en grandes hospitales, no puede monitorear la condición del paciente en tiempo real, lo que genera grandes inconvenientes para médicos y pacientes. En los últimos años, con el rápido desarrollo de la tecnología de comunicación integrada y de red, hemos desarrollado un nuevo tipo de monitor de ECG integrado basado en el procesador ARM7, que utiliza un procesador de alta velocidad de 32 bits del núcleo ARM7TDMI RISC S3C44B0X de Samsung, con las ventajas de bajo costo, tamaño pequeño, alta confiabilidad y operación simple, es adecuado para individuos, hospitales pequeños y medianos y unidades médicas comunitarias, y proporciona una buena ayuda para los enfoques médicos emergentes como la atención médica domiciliaria (HHC) y la telemedicina (Telemedicine ) con apoyo.

2. El principio de funcionamiento del sistema.

Figura 1 Diagrama de bloques de la estructura del sistema del nuevo monitor de ECG incorporado

Una vez que la señal de ECG se recoge de los brazos izquierdo y derecho de la persona a través de electrodos especiales, se envía al circuito de acondicionamiento de señal, en primer lugar amplificada por el preamplificador, filtrada por el filtro de paso alto para filtrar la señal de CC y de baja frecuencia. interferencia de línea de base, amplificada por el amplificador posterior a la etapa y luego pasada a través del filtro El filtro filtra aún más la interferencia de frecuencia de potencia de 50 HZ, y la señal de ECG que cumple con los requisitos se obtiene después del filtro de paso bajo y se envía al ADC desde el terminal de entrada de señal analógica para conversión A/D de alta precisión. Con el fin de suprimir mejor la señal de interferencia y evitar que el cable se afloje y se caiga, también introdujimos el circuito de accionamiento de la pierna derecha y el circuito de detección de cable desconectado en el circuito. El núcleo de control del sistema adopta el S3C44BOX de Samsung, y la pantalla de cristal líquido (LCD) establece una buena interfaz de interacción humano-computadora.Las señales recopiladas se pueden mostrar y reproducir en tiempo real a través de la pantalla LCD, y los datos se transmiten a través de Internet. sobre TCP/IP (Protocolo de control de transmisión, Protocolo de Internet) Transmite datos de manera secuencial y confiable al centro de monitoreo de ECG, proporcionando una referencia para que el personal médico realice diagnósticos oportunos y precisos. El sistema operativo integrado en tiempo real adopta el popular uClinx, administra y coordina el trabajo de cada módulo y garantiza el funcionamiento confiable del sistema.

3. Diseño del módulo de hardware del sistema

3.1, circuito de acondicionamiento de señal

El circuito de acondicionamiento de señal incluye principalmente: amplificador, filtro de paso de banda, filtro de muesca, etc.

Figura 2 Circuito preamplificador de ECG

La señal de ECG humana es una señal débil de baja frecuencia en el fondo de un ruido fuerte, generalmente solo 0.05-5mV, el rango del espectro es: 0.05-100HZ, la amplitud de la señal de ECG es de aproximadamente 1mV cuando se emite normalmente, y el Voltaje de entrada del convertidor A/D Se requiere que el nivel alcance alrededor de 1 V, es decir, el factor de amplificación de ECG es alrededor de 1000 veces. Dado que la interferencia mioeléctrica puede causar el cambio del punto de funcionamiento estático del preamplificador, o incluso alcanzar la saturación, la ganancia del preamplificador no debe ser demasiado grande. Elegimos el amplificador de instrumentación AD620 como preamplificador del sistema, tiene las características de bajo ruido, baja deriva, alta relación de rechazo de modo común, alta impedancia de entrada, etc. Su ganancia se ajusta por la resistencia Rg de los pines 1 y 8, que puede alcanzar de 1 a 100 veces. La fórmula de cálculo es: G=49,4/Rg+1. Diseño el aumento principal para que esté alrededor de siete niveles, selecciono una resistencia bobinada de precisión con una precisión de 0,01 % y una resistencia de 8,25, y utilizo TL064 en la última etapa para amplificar la señal a los requisitos de nivel de entrada del convertidor A/D. .

Figura 3 Circuito de post-amplificación y filtro de ECG

Para suprimir la deriva de CC y el ruido de baja frecuencia fuera de la banda de paso del amplificador, se diseñó un filtro de paso alto RC; debido a que la frecuencia de la señal de ECG está por debajo de 100 HZ, también se diseñaron un filtro de paso bajo y un filtro de banda de banda para eliminar las señales de alta frecuencia y la interferencia de frecuencia de potencia de 50 Hz. filtro de bloqueo.

Para evitar que el cable se afloje y se caiga, se diseñó un circuito de detección de cable.Cuando el electrodo se cae, el nivel de salida del comparador cambia de un nivel alto normal a un nivel bajo, y se genera una señal de alarma para recordar el paciente para comprobar el cable. En el circuito de accionamiento de la pierna derecha, después de que se detecta el voltaje de modo común del cuerpo humano, se amplifica y retroalimenta a la pierna derecha de la persona a través de la inversión, pero no se conecta directamente a tierra del amplificador, de modo que el desplazamiento La corriente del cuerpo humano no fluye hacia el suelo, sino hacia la salida del amplificador de transporte, el AD620 reduce la captación de voltaje de modo común.

3.2 Procesador integrado y circuitos periféricos

S3C44B0X es una solución de microprocesador que Samsung proporciona rentable y de alto rendimiento para dispositivos portátiles y tipos generales de aplicaciones. El núcleo de la CPU adopta el procesador ARMTDMI RISC de 16/32 bits (66 HZ) diseñado por ARM Company, el voltaje operativo del núcleo es de 2,5 V, con caché de alta velocidad de 8 KB, 8 bancos de controladores de almacenamiento externo, un total de 256 MB, ADC de 8 canales y 10 bits y compatible con controlador LCD de pantalla en color/blanco y negro, con modos de control de consumo de energía normal, lento, inactivo y detenido, diseño estático completo optimizado y excelente adecuado para diseños sensibles a la energía y de bajo costo.

3.2.1, conversión A/D

La consideración de la precisión de la señal de ECG se debe principalmente a los requisitos para el análisis y procesamiento de la anomalía del segmento ST Se ha reconocido que el cambio de nivel del segmento ST es de 0,05 mV, por lo que la precisión del muestreo es de menos 0,025 mV. De acuerdo con el estándar AHA de la American Heart Association y la ley de muestreo de Nyquist, cuando la frecuencia de muestreo de la señal es igual o superior al doble de la frecuencia más alta de la señal, la señal original se puede restaurar a partir de la señal muestreada sin distorsión. El rango de frecuencia de ECG es 0.05-100 HZ, y tomamos la frecuencia de muestreo como 200 HZ, es decir, el período de muestreo es de 5 ms.S3C44B0X tiene un ADC de 10 bits con entrada de señal analógica de 8 canales de aproximación sucesiva, y la entrada a escala completa El voltaje es de 2,5 V, que se puede distinguir El valor mínimo del cambio de voltaje de entrada es de 2,5 V/210 = 2,5 mV, la ampliación de la adquisición de ECG es de aproximadamente 1000 veces y la resolución mínima del terminal de entrada es de aproximadamente 2,5 mV/1000 =0.0025mV, por lo que cumple totalmente con los requisitos del sistema.

3.2.2, memoria de programa del sistema Flash ROM y expansión SDRM

S3C44B0X en sí mismo no tiene ROM, por lo que se debe conectar un dispositivo ROM externo para almacenar códigos de programa y datos que aún deben guardarse después de un corte de energía. Hemos adoptado la Flash ROM multipropósito CMOS con una capacidad de 1 MB × 16 que ofrece SST Company, tiene ventajas como buena confiabilidad, bajo consumo de energía y velocidad de lectura rápida. Después de reiniciar el sistema, comienza a ejecutarse desde la dirección 0X00000000. El código de inicio del sistema debe almacenarse en esta dirección, por lo que Flash se asigna en el área Bank0 del procesador.

Se utiliza un SDRM L43L16064 con una capacidad de 8 MB de Linksmart como espacio de ejecución, área de datos y área de pila del programa del sistema para lectura y escritura rápidas del sistema. Su método de almacenamiento es 4Bank×1MB×16, adopta una estructura multibanco y de tubería, y tiene actualización automática, bajo consumo de energía y modo de apagado. Su espacio de almacenamiento está asignado en Bank6 de S3C44B0X y el rango de direcciones es: 0XC000000H-0XCFFFFFFH.

3.2.3, pantalla de cristal líquido LCD y módulo de teclado

Para permitir a los usuarios tener una impresión intuitiva y una observación de sentido común de las señales de ECG recopiladas, hemos adoptado el módulo de pantalla LCD monocromática EG1147 FSTN de EPSON para monitorear la hora, la forma de onda, los parámetros de ECG y los menús del sistema. cooperar con las teclas para controlar y configurar el instrumento. Su matriz de puntos de visualización es de 240 × 320, adopta retroiluminación EL y tiene su propio controlador.Al programar el controlador LCD incorporado de S3C44B0X, los datos de imagen ubicados en el búfer de visualización de la memoria se transmiten al controlador del LCD externo Puerto PC Use el puerto PD como la interfaz del controlador LCD, configure el puerto PC para que funcione en el tercer estado funcional y el puerto PD para que funcione en el segundo estado funcional.

3.2.4, diseño del módulo Ethernet

S3C44B0X no tiene un controlador de interfaz de red integrado NIC (controlador de interfaz de red), por lo que hemos ampliado el controlador RTL8019AS de una empresa Realteck para el sistema, que es compatible con NE2000, tiene un buen trasplante de software y un circuito de interfaz simple. Principio de funcionamiento RTL8019AS: el programa del controlador escribe los datos que se enviarán en el chip de acuerdo con el formato especificado e inicia el comando de envío. Por el contrario, cuando el chip recibe señales del canal físico, las convierte directamente en datos en el formato correspondiente según el protocolo Ethernet y envía una interrupción para solicitar a la CPU que lea los datos.

4. Diseño de software del sistema

El diseño del software incluye principalmente el trasplante del sistema operativo integrado uClinux en S3C44B0X, la recopilación y el almacenamiento de datos de ECG, la realización de una GUI integrada basada en S3C44B0X y el desarrollo de controladores de dispositivos de red.

4.1 Trasplante del sistema operativo uClinux embebido en S3C44B0X

uClinux es un sistema operativo gratuito y de código abierto diseñado específicamente para procesadores sin MMU (Memory Management Unit). Es compatible con múltiples tareas y adopta un diseño modular. El trasplante del sistema se puede dividir en dos partes: gestor de arranque y trasplante del kernel.

Esencialmente hablando, el cargador de arranque no pertenece al kernel del sistema y comienza a ejecutarse después de que se enciende la CPU, creando un entorno de inicialización y arrancando el kernel. Esta parte del código está escrita en lenguaje ensamblador, principalmente para completar la inicialización del hardware, inicializar y establecer el mapa de memoria del sistema, y cambiar el valor de la PC al mismo tiempo, para que la CPU comience a ejecutar el núcleo del sistema operativo. sistema de SDRM.

Al trasplantar el kernel, primero descargue el paquete del archivo de código fuente en el entorno RedHat Linux para establecer un entorno de compilación cruzada, y luego ingrese a la carpeta uClinux-dist para configurar el kernel.La configuración del sistema se compone principalmente de tres partes: Makefile, archivo de configuración (config.in) y herramienta de configuración (en el directorio /script). Ejecute el comando make menuconfig, aparecerá el menú de nivel superior, seleccione el sistema de hardware, la versión del kernel y la biblioteca C, aquí elegimos S3C44B0X de Samsung para los proveedores, Linux-2.4-x para la versión del kernel y uClibc para la biblioteca C. Luego modifique el código fuente, correspondiente a los subdirectorios de cada hardware, por ejemplo, modifique o agregue controladores en uClinux-dist/linux-2.4-x/drivers/; guarde la configuración y salga, luego ejecute los comandos make dep y make lib_only para generar la biblioteca C; ejecute make user_only para generar el programa de aplicación; luego ejecute make romfs y make image para generar el sistema de archivos rom, copie el archivo del kernel en uClinux-dist/images; finalmente ejecute make para generar el archivo del kernel que puede ser ejecutado por el sistema integrado, estos tres archivos pueden aparecer en uClinux-dist/images: "rom" es el kernel comprimido, "ram" es el kernel que se ejecuta directamente y romfs.img es el sistema de archivos de uClinux. Los archivos "ram" y "rom" se pueden descargar desde el puerto serie de la PC a la memoria del sistema embebido y ejecutarse directamente a través de la hiperterminal. En este momento, la información de inicio de uClinux también se mostrará en la hiperterminal.

4.2 Implementación de GUI integrada basada en S3C44B0X

El diseño del programa del controlador de pantalla es principalmente el puntero de estructura de PSD (Puntero a dispositivo de pantalla).La estructura a la que apunta el puntero registra todos los atributos relevantes y juzga qué subfunción se selecciona de acuerdo con el atributo de visualización para proporcionar la información relevante. función de visualización. El motor de gráficos llama a PSD para completar funciones de dibujo como rectángulo y círculo, y estas funciones llaman a las funciones de dibujo básicas del controlador de pantalla subyacente para completar la visualización de gráficos.

4.3 Implementación del controlador RTL8019AS bajo uClinux

En uClinux, una interfaz de red se considera una entidad que envía y recibe paquetes de datos, representada por una estructura de datos net_device, y varias operaciones en la interfaz de red se definen en la estructura de datos. El programa se modifica sobre la base del archivo del controlador de red de uClinux, modificando principalmente dos archivos en /drivers/net: ne.c y 8390.c, incluida la mayor parte del trabajo, como la inicialización del chip, la recepción de paquetes, el registro de la red, etc. . El kernel llamará automáticamente a la función ne_probe() durante la inicialización, leerá el registro de identificación RTL8019AS, detectará si el dispositivo existe para determinar si iniciar el controlador, configurará e inicializará el hardware y luego inicializará las variables en la estructura net_device y luego llame a Rtl8019as_init() para realizar la configuración relacionada con el registro de RTL8019AS y, finalmente, inicie y cierre RTL8019AS de acuerdo con el valor de starp.

5. Conclusión

En vista de la señal de ECG extremadamente débil y las características de ser fácilmente perturbada por el mundo exterior, la innovación de este documento es utilizar el amplificador de instrumentación AD620 con baja deriva y relación de rechazo de modo común para la amplificación primaria de la señal, y diseñar el circuito de transmisión de la pierna derecha para mejorar la señal.Capacidad antiinterferencias;la introducción de LCD brinda a las personas una impresión intuitiva y un juicio de sentido común;los datos recopilados se pueden transmitir al centro de datos remoto en tiempo real a través de Ethernet para un análisis y diagnóstico experto; la introducción de uClinux integrado asegura la estabilidad y confiabilidad del sistema La operación, el diseño miniaturizado es más propicio para que el paciente lo lleve. Dado que la incidencia de enfermedades cardiovasculares continúa aumentando año tras año, este monitor de ECG portátil tiene un alto valor de aplicación y buenas perspectivas de mercado.

5. Esquema de diseño del sistema de control principal del ventilador médico basado en tecnología SOPC

Un ventilador es un instrumento que puede reemplazar o ayudar a la función respiratoria de una persona. Es adecuado para la respiración artificial de pacientes con insuficiencia respiratoria o que incluso dejan de respirar. Puede ayudar a los pacientes a corregir la hipoxia y descargar dióxido de carbono, y es una herramienta importante para salvar la vida de algunos pacientes en estado crítico.

Dirección de citación de este artículo: Esquema de diseño del sistema de control principal del ventilador médico basado en tecnología SOPC

La mayoría de los principales sistemas de control de los productos de ventilación existentes se implementan en base a microcomputadoras de un solo chip. Para productos con funciones más fuertes, se requieren microcomputadoras de un solo chip de alta gama, lo que hace que el costo del sistema sea relativamente alto y hay muchos periféricos. módulos de interfaz y estructuras complejas. El uso de la tecnología SOPC (Sistema en chip programable) para diseñar el sistema de control principal puede hacer un uso completo de las potentes funciones del núcleo IP, reducir la cantidad de periféricos y, al mismo tiempo, solo ocupa una pequeña parte de los recursos, lo que mejora enormemente el rendimiento de costes del sistema.

Este documento utiliza la tecnología SOPC para diseñar el sistema de control principal del ventilador de presión positiva continua en las vías respiratorias , utilizando el procesador de núcleo blando Nios II de Altera y algunos núcleos IP generales. El autor personaliza los componentes según la especificación del bus Avalon e integra toda la lógica de control. Integrado en un solo FPGA.

Los ventiladores de presión positiva envían aire a los pulmones al aumentar la presión en las vías respiratorias, y el aumento de la presión en los pulmones expande las cavidades pulmonares. Cuando se pierde la presión, debido a la elasticidad del tejido pulmonar, los pulmones recuperan su forma original y parte del aire intercambiado se exhala del cuerpo. En la actualidad, la mayoría de los ventiladores utilizan este método de aumentar la presión en las vías respiratorias para suministrar aire al paciente.

La presión de aire requerida por el ventilador es proporcionada por un motor de CC, y la señal de control del motor de CC es una señal PWM, y la velocidad del motor se controla de acuerdo con el ciclo de trabajo y el período de la señal PWM. La interfaz externa proporciona botones para aceptar comandos y establecer varios parámetros. La información de solicitud, la información de estado y la información de parámetros se muestran a través de la pantalla LCD de caracteres. Para la conveniencia de probar el sistema, UART se utiliza como interfaz de control de comando para controlar directamente el sistema, y la interfaz se oculta después del producto terminado.

estructura del sistema

El diagrama de bloques del sistema de control principal del ventilador con tecnología SOPC como núcleo se muestra en la Figura 1.

Fig.1 Diagrama de bloques de la estructura del hardware del sistema de ventilación

El núcleo FPGA del sistema de control principal adopta EP1C6T144C8 de la serie Cyclone de Altera Company . La CPU es el procesador de núcleo blando Nios II, que gestiona todo el sistema de forma unificada. La placa de control principal está dentro de la caja de línea plegada. Excepto por la PC para descargar y depurar, el motor de CC y la placa de control principal deben alimentarse por separado. Después de que el motor de CC funciona, el flujo de aire se envía a la máscara y el motor ajusta el tamaño del flujo de aire de acuerdo con la señal del terminal. Se instala un módulo de detección de presión en la máscara, que se devuelve al tablero de control principal a través de la conversión A/D y se usa para realimentar y ajustar el flujo de aire. La máscara es para uso del paciente.

Control de motores de CC

El sistema utiliza la señal PWM para controlar el motor de CC. No hay componente PWM en el núcleo IP estándar proporcionado por SOPC Builder, y debe personalizarse.La señal de salida del componente PWM es una onda cuadrada, y el período y el ciclo de trabajo de la onda cuadrada son ajustables. La estructura lógica de la tarea PWM se muestra en la Fig. 2.

Figura 2 Estructura lógica de tareas PWM

La lógica de tareas del componente PWM es:

●La lógica de tareas PWM consta de un reloj de entrada, una señal de salida, un bit de habilitación, un contador de 32 bits y un comparador de 32 bits;

●El reloj impulsa el contador de 32 bits para establecer el período de la señal de salida;

El comparador se usa para comparar el valor actual del comparador de 32 bits con el valor del ciclo de trabajo para determinar la señal de salida;

●Si el valor actual es menor o igual que el valor del ciclo de trabajo, la señal lógica de salida es 0; de lo contrario, es 1.

Archivo de registro para el componente PWM:

●clock_divde es el número de ciclos de reloj en un ciclo de PWM;

●duty_cycle La salida PWM es el número de ciclos de reloj de bajo nivel;

●habilitar permiso/prohibición de salida PWM. Un flanco ascendente de 0 a 1 habilita el componente PWM.

El archivo de encabezado y el paquete de controladores del registro de definición de PWM son:

altera_avalon_pwm_init(); //Inicialización del módulo PWM, incluida la configuración del período

altera_avalon_pwm_enable(); //habilitar módulo PWM

altera_avalon_p wm_disable(); //Módulo PWM deshabilitado

altera_avalon_ pwm_change_duty _cycle(); //Ajuste del ciclo de trabajo del módulo PWM

Para los motores de CC, el ciclo de trabajo PWM debe alcanzar una cierta cantidad para que el motor funcione. La señal PWM por debajo del umbral (PWM_DUTY_THRESHOLD) no puede impulsar el motor, y esta parte de la energía se convertirá en calor y dañará el motor. Por lo tanto, , al establecer el valor de PWM, se debe tener en cuenta que el valor se establece por encima del umbral, y el valor establecido se juzga en altera_avalon_pwm_change_duty_cycle (). Si el valor es inferior a PWM_DUTY_THRESHOLD, se ajusta a PWM_DUTY_THRESHOLD+1.

Una vez que se completan todos los diseños anteriores, se empaquetan en componentes SOPC en SOPC Builder.

Módulo de salida e indicación

El sistema necesita ingresar configuraciones, controlar y mostrar avisos. Esta parte de la función incluye entrada clave, salida de indicador LED, salida de zumbador, salida LCD, etc.

6. Circuito de control de accionamiento de motor ultrasónico basado en NiosⅡ

El motor ultrasónico es un nuevo tipo de micromotor. Su principio de funcionamiento es hacer que el estator vibre ligeramente en el rango de frecuencia ultrasónica a través del efecto piezoeléctrico inverso del material piezoeléctrico y convertir la vibración en el movimiento giratorio (lineal) del motor. por fricción. Los motores ultrasónicos tienen las ventajas de tamaño pequeño, peso ligero, estructura compacta, respuesta rápida y sin interferencias electromagnéticas. Tienen amplias perspectivas de aplicación en equipos aeroespaciales y militares y otros campos.

En los últimos años, China ha presentado algunas teorías de control en el aspecto del control de motores ultrasónicos y ha construido algunos circuitos de conducción y control reales para la conducción de motores ultrasónicos. En 2010, Master Xue Wenyu estudió el controlador de accionamiento de motor ultrasónico basado en chips DSP, pero el circuito de accionamiento todavía está dominado por circuitos analógicos tradicionales, la precisión no es alta y la frecuencia y la fase no se pueden ajustar en tiempo real. En 2011, Master Sun Lin estudió el controlador de accionamiento de motor ultrasónico basado en DSP/FPGA y utilizó la tecnología DDS para generar ondas sinusoidales digitales.Aunque se mejoró la precisión y el rendimiento en tiempo real, se desperdiciaron muchos recursos lógicos del chip. y no era propicio para el control de la unidad Miniaturización del circuito.

Este artículo utiliza el chip EP3C400240C8 de Altera para diseñar un nuevo controlador de accionamiento de motor ultrasónico con FPGA como núcleo, tecnología SOPC y procesador de núcleo blando Nios II . En la FPGA, se personaliza un procesador Nios II de núcleo blando con la idea de SOPC (sistema en un chip programable) como parte de la operación de control, y el módulo DDS y el módulo de conteo de retroalimentación de rejilla con frecuencia, fase y amplitud ajustables. están escritos en lenguaje Verilog.Un sistema de circuito cerrado tiene buena flexibilidad y capacidad de reconfiguración mientras satisface la precisión del control y el rendimiento en tiempo real, y puede controlar el funcionamiento del motor ultrasónico con muy pocos recursos de hardware y una estructura de sistema altamente integrada, que es conveniente para la miniaturización del circuito de control de accionamiento.

1 Diseño del controlador de accionamiento

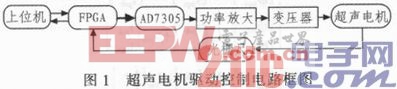

1.1 Circuito de control de accionamiento

El sistema de control de accionamiento de motor ultrasónico propuesto en este documento se compone de un controlador de control y un amplificador de potencia/circuito de refuerzo. La figura 1 es un circuito de control de accionamiento de motor ultrasónico construido con FPGA como núcleo. El mecanismo de accionamiento del motor ultrasónico requiere que el controlador proporcione la misma frecuencia y corriente alterna sinusoidal de igual amplitud con una cierta diferencia de fase entre las dos fases en la banda de frecuencia ultrasónica, y el voltaje está entre decenas de voltios y cientos de voltios. Todas las funciones de este circuito se realizan mediante el software FPGA, que controla y emite corriente alterna sinusoidal, lo que mejora en gran medida la estabilidad y precisión del sistema de control y reduce en gran medida el área de la placa de circuito del sistema de control. varias ondas ultrasónicas al mismo tiempo motor.

Este sistema de control de accionamiento utiliza el módulo DDS programado dentro de la FPGA para generar dos canales de datos de onda sinusoidal con una cierta diferencia de fase, y luego los convierte en una señal de onda sinusoidal a través del chip DA.Después de la amplificación de potencia, el voltaje aumenta en un transformador.

La forma de onda de salida del circuito después de cargar el motor ultrasónico se muestra en la Figura 2, y la forma de onda se vuelve mucho más suave. Cuando la frecuencia del motor ultrasónico se desvía durante la operación, el sistema también puede ajustar la salida del variador correspondiente del cambio de velocidad, y no habrá fenómeno de velocidad inestable del motor.

1.2 Sistema interno FPGA

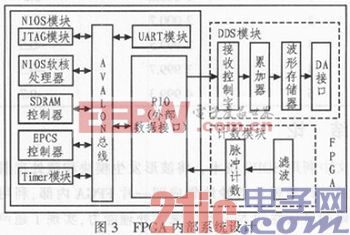

La figura 3 es la estructura interna de FPGA en el circuito de activación de control de motor ultrasónico. El núcleo de su diseño es el núcleo blando Nios II personalizable y el módulo DDS que envía la señal sinusoidal y el módulo de conteo que lee el pulso de retroalimentación del codificador de rejilla.

1.2.1 Construcción del sistema Nios Ⅱ

Nios II es un microprocesador RISC de 32 bits de núcleo blando desarrollado por Altera. Como un núcleo blando escrito en lenguaje de descripción de hardware, Nios II puede formar Nios con otros módulos de interfaz de hardware descritos en lenguaje HDL a través del mecanismo de bus Avalon integrado. El sistema está integrado en los FPGA de la serie Stratix, Cyclone o APEX de Altera para formar un diseño programable de sistema en chip.

En primer lugar, construya un sistema mínimo basado en Nios II. Los componentes de este sistema están todos en el núcleo IP proporcionado por SOPC Builder. Seleccione el procesador Nios II, el controlador EPCS, el controlador SDR AM y el módulo JTAG a su vez. Entre ellos, Nios II realiza la función de MCU, SDRAM y los componentes del controlador EPCS se utilizan para conectar la memoria externa, el módulo JTAG realiza la depuración y descarga del programa. Además, también necesitamos usar el puerto serie para recibir los datos enviados por la computadora host y la interrupción del temporizador, así que agregue un módulo UART y un módulo de temporizador al sistema. Finalmente, el procesador debe controlar el funcionamiento del módulo DDS y recibir la cantidad de pulsos calculados por el módulo de conteo de trama, y se deben agregar algunos puertos de E/S para la transmisión de datos. De esta forma se construye un sistema NIOS dentro de la FPGA.

1.2.2 Módulo DDS

El sintetizador de frecuencia digital directo (Direct Digital Frequency Synthesizer) es una tecnología de síntesis de frecuencia basada en tecnología totalmente digital, que sintetiza directamente la forma de onda requerida a partir del concepto de fase. El principio básico es generar onda sinusoidal, onda coseno, onda triangular, onda triangular, onda cuadrada y otras formas de onda con frecuencia controlable y fase en forma de oscilador de control numérico. La figura 4 muestra la estructura básica de DDS.

En la Fig. 4, fc es la frecuencia de reloj, K es la palabra de control de frecuencia, N es la longitud de palabra del acumulador de fase, D es el ancho de línea de datos de la ROM.

El diseño del DDS en este documento se divide principalmente en tres módulos: el módulo de recepción de la palabra de control, que se utiliza para comunicarse con el sistema NIOS y recibir la palabra de control de la computadora host; el módulo de memoria de forma de onda, que se utiliza para generar la forma de onda requerido por la señal de conducción.Este documento solo necesita generar onda sinusoidal; módulo acumulador de fase, utilizado para generar frecuencia y fase, este artículo es para convertir las palabras de control de fase y frecuencia recibidas en frecuencia y fase reales.

1.2.3 Módulo contador de pulsos

El módulo de conteo de pulsos consta de dos partes: filtrado y conteo, principalmente para leer la información devuelta por el codificador de rejilla, para realizar el posicionamiento preciso y el control de velocidad del motor. El codificador de rejilla utilizado en este artículo tiene una resolución de 0,5 um/conteo y emite 2 señales diferenciales de A+/A-, B+/B-. Para convertir la salida diferencial del codificador en una señal de pulso de un solo extremo, este El artículo selecciona 26LS32AC diferencial Convertir a chip de un solo extremo para realizar la conversión de señal diferencial. Las señales bidireccionales A y B convertidas son un conjunto de señales de pulso ortogonales. Cuando el motor se mueve en diferentes direcciones, la diferencia entre las señales bidireccionales A y B

La relación de fase del motor se invertirá para determinar la dirección en la que está funcionando el motor. Por lo tanto, de acuerdo con esta característica, en FPGA, se programa con lenguaje Vetilog un módulo de conteo que realiza la función del circuito de codificación de pulsos en cuadratura.

Al mismo tiempo, para eliminar aún más la señal de interferencia de pulso estrecho que puede generar la señal de retroalimentación de rejilla, el controlador filtra aún más la señal convertida de un solo extremo. El proceso principal es: al recolectar una determinada señal de estado, use un reloj de muestreo con una frecuencia más alta que la señal de estado para recolectarla repetidamente muchas veces, hasta que los resultados de la recolección múltiple sean completamente consistentes, se considera una salida de señal válida. Luego, la señal filtrada se envía al circuito de pulsos del codificador de cuadratura para identificación de dirección y conteo.

1.3 Modo de control del controlador de accionamiento

Cuando el motor está funcionando, la FPGA recibe los datos de la computadora superior a través del puerto serie y los envía al procesador Nios II.Después del procesamiento del programa, la información, como el modo de funcionamiento del motor (paso a paso, continuo), la distancia recorrida, etc. se obtiene, y el procesador Nios II pasa el control El tiempo de arranque y parada del módulo DDS controla la presencia o ausencia de la señal de accionamiento y luego controla el proceso de movimiento del motor. La información real del desplazamiento y la velocidad del motor durante la operación se puede obtener de la señal de retroalimentación del codificador de rejilla. El módulo contador calcula el valor del número de pulso y lo envía al procesador Nios II. El procesador cambia la amplitud de la señal de salida del DDS a través de un algoritmo de control específico Valor, frecuencia, fase para realizar ajustes adicionales en el estado de funcionamiento del motor. De esta manera, se realiza un sistema de control de bucle cerrado completo mediante un chip FPGA.

2 Análisis experimental

2.1 Investigación sobre la estabilidad de la velocidad del motor ultrasónico

Dado que el motor ultrasónico se encuentra dentro de un determinado rango de frecuencia, su velocidad disminuye con el aumento de la frecuencia, por lo que podemos garantizar la estabilidad de la velocidad del motor ultrasónico controlando la frecuencia de la señal sinusoidal.

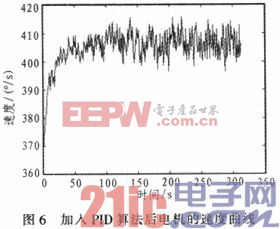

El motor ultrasónico lineal utilizado en este experimento es relativamente estable alrededor de 33,8 kHz, por lo que se selecciona 33,8 kHz como la frecuencia experimental del motor ultrasónico lineal. Primero estudie la estabilidad de velocidad del motor ultrasónico lineal sin agregar ningún algoritmo de control.Los resultados experimentales se muestran en la Figura 5.

En la figura anterior se puede ver que la velocidad del motor ultrasónico no es muy estable cuando se ejecuta directamente sin el algoritmo de control. Si se agregan algunos algoritmos de control al procesador Nios II para controlar la frecuencia cuando el motor está funcionando, la estabilidad de la velocidad mejorará significativamente. Tome el algoritmo PID incremental como ejemplo:

△u(k)=A1e(k)+A2e(k-1)+A3e(k-2)

u(k) es la frecuencia y e(k) es la diferencia entre la velocidad objetivo y la velocidad actual en el tiempo de muestreo K-ésimo. Calcule el cambio de frecuencia a través de la fórmula anterior, envíe una nueva palabra de control de frecuencia al módulo DDS y cambie la frecuencia de la señal de accionamiento para lograr el efecto de controlar la velocidad de funcionamiento del motor. La Figura 6 es la curva de velocidad del motor después de agregar el algoritmo PID.

Puede verse que la fluctuación de velocidad del motor ultrasónico impulsado por el algoritmo de control es mucho menor que la fluctuación del motor ultrasónico lineal sin el algoritmo. Esto resuelve bien el problema de la estabilidad de la velocidad del motor ultrasónico lineal durante el movimiento.

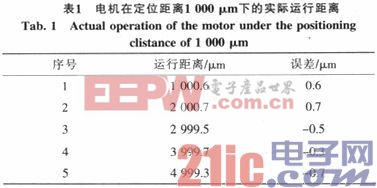

2.2 Prueba de precisión de posicionamiento

Los experimentos de posicionamiento preciso se llevan a cabo en una plataforma de movimiento de motor ultrasónico lineal de un solo eje. Esta plataforma de movimiento de precisión tiene características de salida relativamente estables cuando el ancho de pulso es de 3,5 μs y la distancia de paso es de aproximadamente 100 nm. Use el método "continuo + paso" para pruebas de precisión, muévase continuamente al objetivo predeterminado y luego use micro-pasos para ajustar. El sistema de interferómetro láser XL-80 de la compañía británica REN-ISHAW se utiliza como sistema de medición de este experimento, y los datos de visualización del interferómetro láser se comparan con la distancia de posicionamiento. Los experimentos muestran que la precisión de posicionamiento de la plataforma de movimiento lineal del motor ultrasónico puede alcanzar 1 μm.

3 Conclusión

En este documento, utilizando la tecnología SOPC , el módulo de generación de formas de onda, el módulo del microprocesador y el módulo de conteo de pulsos se integran inteligentemente en un FPGA, y el diseño del circuito de control de la unidad de motor ultrasónico se realiza utilizando la flexibilidad de la lógica programable y la poderosa capacidad de procesamiento. de Nios II. Usando el esquema SOPC para el diseño del sistema, aprovechando al máximo la capacidad de programación de FPGA, todo el proceso de desarrollo se vuelve flexible y conveniente, y el software y el hardware del sistema se pueden actualizar sin cambiar ningún circuito periférico, lo que prolonga el ciclo de vida del sistema. y mejorar en gran medida el rendimiento y la integración del sistema reducen el costo de desarrollo del sistema, que es la ventaja sobre otras soluciones y también se ajusta a la dirección de desarrollo de la ciencia y la tecnología actuales.