En la lección anterior, hablamos sobre algunos principios básicos de la memoria caché. En esta lección, hablaremos sobre la configuración de la memoria caché de H7.

El caché L1 del núcleo Cortex-M7 consta de áreas de memoria de varias líneas. Nuestro H7 está dividido en 16 Kbytes I-Cache y D-Cache

, cada uno de los cuales tiene 32 bytes, y cada línea está equipada con una etiqueta de dirección. El búfer de datos DCache es un grupo de 4 filas, llamado conjunto asociativo de 4 vías. El búfer de instrucciones ICache es un grupo de 2 filas, el conjunto bidireccional guarda las etiquetas de dirección y no necesita marcar una dirección para cada fila

- Calculado con un D-Cache de 16 KBytes, un total de 128 conjuntos (conjuntos), 512 líneas de búfer (líneas), cada línea de búfer 32 bytes

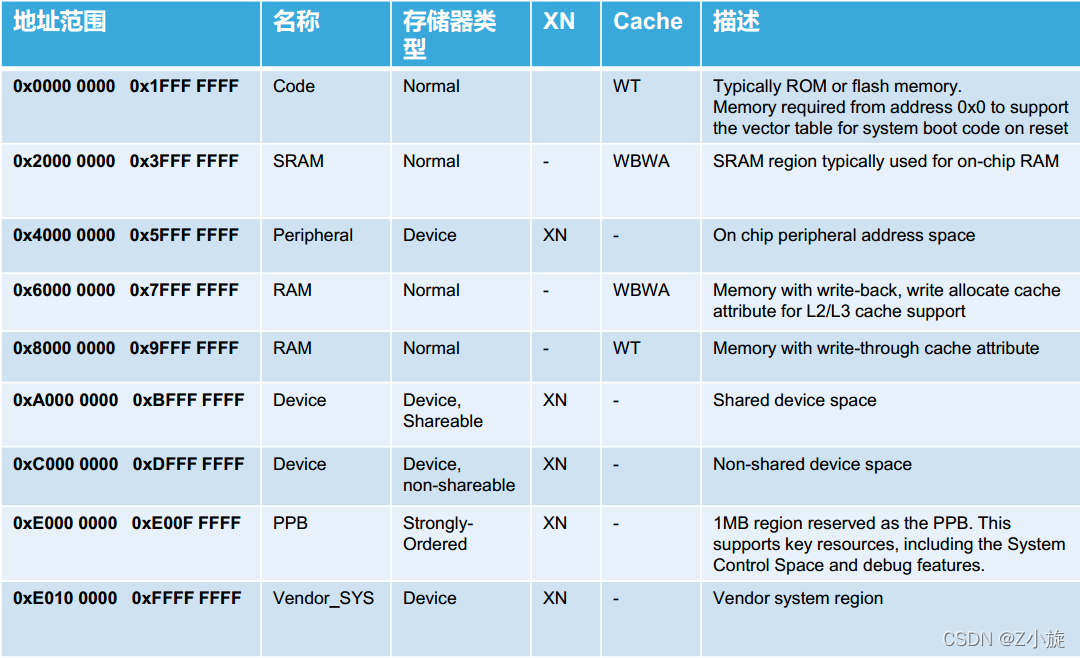

Primero mire el rango de mapeo de direcciones de memoria predeterminado de H7:

Entre ellos, WT significa Write-through (escritura simultánea), WB significa Write-back (reescritura), WA significa Write-allocate (asignación de escritura) y RA (asignación de lectura) no está claramente marcado con WA. XN significa Execute-Never, lo que significa que nunca se permite la ejecución de código si el espacio de direcciones correspondiente es XN.

El tipo de memoria es Normal para usar el caché, y la interfaz TCM no se puede almacenar en caché.

La MPU establece la configuración de caché en H7, por lo general, solo se utilizan los siguientes métodos.

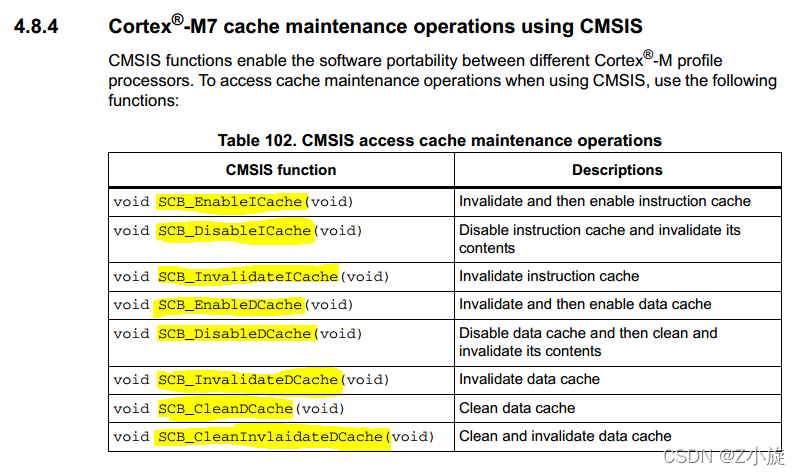

Las funciones relacionadas con las operaciones de caché se declaran en el archivo de encabezado cmsis/include/core_cm7.h, como puede verse por el nombre de la función, incluidas cuatro operaciones de caché: habilitar, deshabilitar, limpiar e invalidar.

Por supuesto, hay tres funciones menos utilizadas:

void SCB_InvalidateDCache_by_Addr(uint32_t *addr, int32_t dsize);

void SCB_CleanDCache_by_Addr(uint32_t *addr, int32_t dsize);

void SCB_CleanInvalidateDCache_by_Addr(uint32_t *addr, int32_t dsize);

Echemos un vistazo a estas funciones.

SCB_EnableICache()

Habilite el comando I-Cache, el sistema se puede inicializar primero después del encendido

SCB_DisableICache()

Deshabilitar instrucción I-Cache.

SCB_InvalidateICache()

Para invalidar el I-cache, la invalidación Inválida es marcar la Línea de Caché como no válida, es decir, eliminar la operación.

SCB_EnableDCache()

Esta función activa D-Cache de datos, que se puede inicializar primero después de encender el sistema.

SCB_DisableDCache()

El D-Cache de datos está prohibido.

SCB_InvalidateDCache()

Para invalidar el D-Cache, la invalidación Inválida es marcar la línea de caché como no válida, es decir, eliminar la operación.

SCB_CleanDCache()

Clean borra todas las líneas de caché, es decir, escribe todas las líneas de caché sucias en la dirección física real correspondiente a la línea de caché

El llamado atributo drity significa que la línea de caché correspondiente se actualiza durante la operación de escritura, pero no a la dirección física real, y la acción de esta limpieza es actualizar el contenido en el caché a la dirección física real.

SCB_CleanInvalidateDCache()

Esta función es una combinación de las dos funciones anteriores SCB_InvalidateDCache y SCB_CleanDCache. Después de escribir los datos sucios en la línea de caché en el área de almacenamiento correspondiente, marque la línea de caché como no válida, lo que indica eliminación. De esta forma, se libera espacio en la memoria caché y se pueden cargar nuevos datos.

SCB_InvalidateDCache_by_Addr()

Invalide su línea de caché correspondiente de acuerdo con la información de la dirección.

SCB_CleanDCache_by_Addr()

Limpie la línea de caché correspondiente de acuerdo con la información de la dirección.

SCB_CleanInvalidateDCache_by_Addr()

Limpie e invalide la línea de caché correspondiente de acuerdo con la información de la dirección.

Eso es todo, la mayoría de las cuales son operaciones en D-Cache. Cuando lo use normalmente, simplemente llame a la función para inicializarlo directamente.

SCB_EnableICache();//使能I-Cache

SCB_EnableDCache();//使能D-Cache

Sin embargo, en STM32H7 - Cache (1) , mencionamos la consistencia de Cache, como errores de consistencia causados por operaciones DMA, etc.

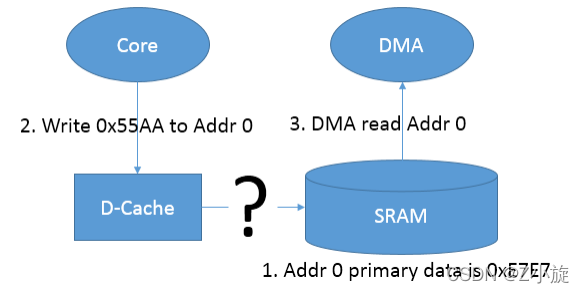

1. La CPU escribe datos en la memoria

Cuando la CPU tiene una instrucción para escribir en la memoria física, la CPU primero actualizará la caché de línea de caché correspondiente (estrategia de reescritura). En ausencia de limpieza, los datos en la memoria física real correspondiente no se actualizarán. , si hay otros hosts (como DMA) accediendo a esta memoria en este momento, habrá un problema (porque la memoria física real no se ha actualizado, lo que es inconsistente con el caché D), que es la llamada consistencia de caché problema

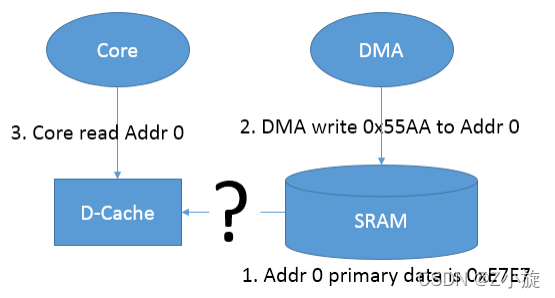

2. La CPU lee datos de la memoria

El segundo caso es que DMA actualiza cierto segmento de la memoria física (DMA y caché no tienen canales directos), y cuando la CPU lee esta memoria nuevamente, la línea de caché de la dirección correspondiente se ha almacenado en caché, lo que hace que la CPU haga lo que se lee son los datos en la línea de caché, no los datos en la memoria física real actualizada por DMA.

Para evitar este problema y garantizar la consistencia de los datos, hemos establecido la función obligatoria de escritura simultánea de D Cache.

Escritura simultánea forzada: cada vez que la CPU opera los datos en la memoria caché, también se actualizarán en la SRAM. No es necesario enviar una operación de limpieza para garantizar que los datos en la memoria caché D y la SRAM sean consistentes.

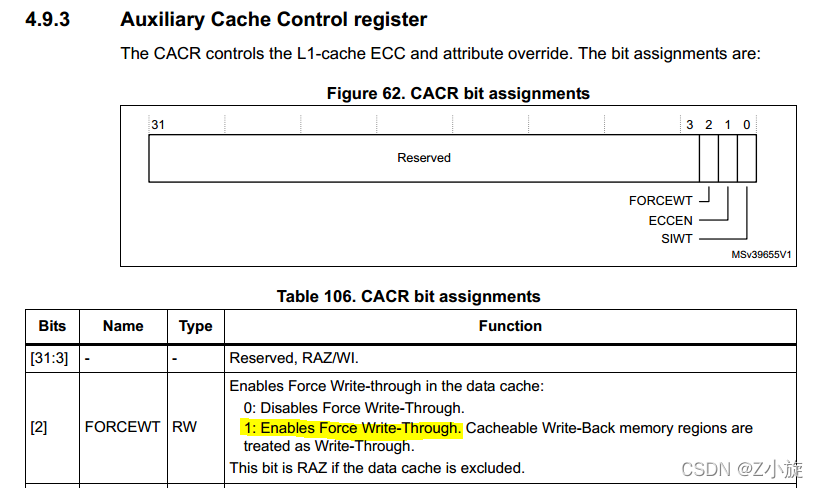

Debe configurar el primer bit del registro SCB->CACR en 1 para habilitar la escritura simultánea forzada

SCB->CACR|=1<<2; //强制D-Cache透写

Luego obtenemos el proceso de inicialización de Cache:

//使能CPU的L1-Cache

void Cache_Enable(void)

{

SCB_EnableICache();//使能I-Cache

SCB_EnableDCache();//使能D-Cache

SCB->CACR|=1<<2; //强制D-Cache透写,如不开启,实际使用中可能遇到各种问题

}

La ventaja de esto es que se puede garantizar la consistencia de los datos en D Cache y SRAM, pero la desventaja es que se perderá cierto rendimiento (los datos deben volver a escribirse cada vez). Modo de escritura directa de caché