1. Conocimientos básicos de la interfaz de comunicación

Formas de comunicación entre dispositivos

1. En general, los métodos de comunicación entre dispositivos se pueden dividir en comunicación en paralelo y comunicación en serie . Su diferencia es:

Comunicación en serie : los datos se transmiten en orden de bits. Ventajas: ocupa menos recursos de pines, desventajas: velocidad relativamente lenta.

Comunicación en paralelo : todos los bits de datos se transmiten al mismo tiempo. Ventajas: velocidad rápida, desventajas: ocupa muchos recursos de pines.

La comunicación en serie generalmente transmite datos en un formato de trama, es decir, una trama a la vez.Cada trama contiene una señal de inicio, información de datos, información de parada y posiblemente información de verificación.

2. Clasificación de la comunicación en serie

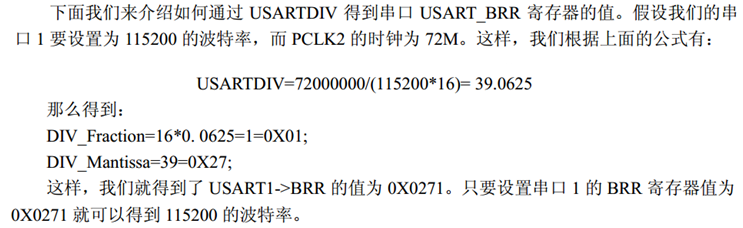

(1) Según la dirección de transmisión de datos, se divide en:

Símplex : la transmisión de datos solo admite la transmisión de datos en una dirección;

semidúplex : permite la transmisión de datos en dos direcciones. Sin embargo, en un momento determinado, los datos solo pueden transmitirse en una dirección. En realidad, es una comunicación simplex que cambia de dirección, no requiere extremos de envío y recepción independientes, y los dos se pueden combinar para usar un puerto.

Dúplex completo : permite que los datos se transmitan en ambas direcciones al mismo tiempo. Por lo tanto, la comunicación full-duplex es una combinación de dos métodos de comunicación simplex, que requieren receptores y transmisores independientes.

(2) Según el método de comunicación, se divide en:

Comunicación síncrona : con transmisión de señal de sincronización de reloj. Por ejemplo: SPI, interfaz de comunicación IIC.

Comunicación asíncrona : sin señal de sincronización de reloj. Por ejemplo: UART (transmisor receptor asíncrono universal), bus único.

En la comunicación síncrona, se utiliza una línea de señal para transmitir señales por encima del dispositivo transceptor, y las dos partes coordinan y sincronizan los datos bajo el impulso de la señal del reloj. Por ejemplo, en la comunicación, normalmente ambas partes estipularán uniformemente que la línea de datos se muestrea en el flanco ascendente o descendente de la señal de reloj.

En la comunicación asíncrona, la señal de reloj no se usa para la sincronización de datos. Ellos insertan directamente algunos bits de señal para la sincronización en la señal de datos, o empaquetan los datos del sujeto y transmiten los datos en el formato de una trama de datos. En la comunicación, también es necesario que ambas partes acuerden la velocidad de transmisión de datos (es decir, la velocidad en baudios), etc., para sincronizar mejor. Las velocidades en baudios más utilizadas son 4800bps, 9600bps, 115200bps, etc.

En la comunicación síncrona, la mayor parte del contenido transmitido por la señal de datos son datos válidos, mientras que la comunicación asíncrona contendrá varios identificadores de la trama de datos, por lo que la eficiencia de la comunicación síncrona es alta, pero el error permitido de los relojes de ambos lados del síncrono La comunicación es pequeña Un pequeño error de reloj puede provocar desorden de datos y el error permitido de los relojes en ambos lados de la comunicación asíncrona es relativamente grande.

Interfaz de comunicación serie común:

2. Transceptor universal síncrono / asíncrono (USART)

1. El transceptor asíncrono síncrono universal es un dispositivo de comunicación en serie que puede intercambiar datos de dúplex completo con dispositivos externos de manera flexible. A diferencia del USART, también hay un UART, que corta la función de comunicación síncrona sobre la base del USART, y solo tiene comunicación asincrónica. La simple distinción entre síncrono y asíncrono es observar la necesidad de una salida de reloj externo durante la comunicación.La comunicación en serie que usamos normalmente es básicamente UART.

USART admite la comunicación unidireccional síncrona y la comunicación de un solo cable semidúplex; también admite la red de interconexión local LIN, el protocolo de tarjeta inteligente (SmartCard) y la especificación lrDA (Asociación de datos infrarrojos) SIR ENDEC.

USART admite el uso de DMA, que puede realizar una comunicación de datos de alta velocidad.

2. STM32 UART presenta

comunicación asíncrona dúplex completo

, sistema generador de tasa de baudios fraccionada, que proporciona una tasa de baudios precisa . Envío y recepción de velocidad en baudios programable compartida, hasta 4,5 Mbits / s; longitud de palabra de

datos programable (8 o 9 bits); bit de parada configurable (admite 1 o 2 bits de parada); configurable El uso de comunicación DMA multibúfer; transmisor independiente y bits de habilitación del receptor; indicadores de detección: ① búfer de recepción ② búfer de envío vacío ③ indicador de fin de transmisión; múltiples fuentes de interrupción con indicadores, interrupción de disparo; otros: control de inspección de calibración , cuatro señales de detección de error

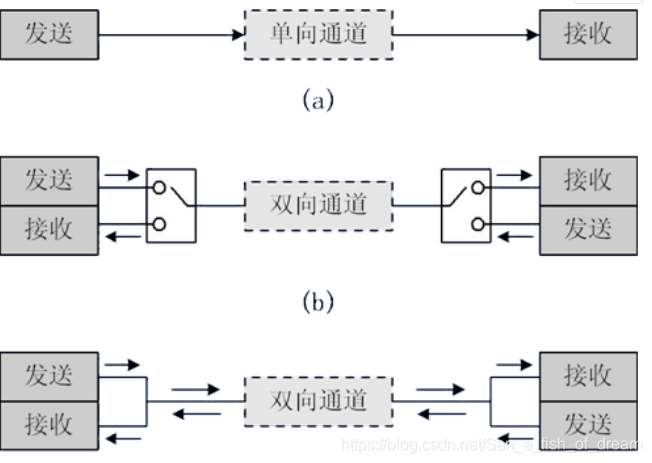

3. Método de conexión del pin UART

- RXD: pin de entrada de datos, recepción de datos;

- TXD: Pin de transmisión de datos, transmisión de datos.

Para la conexión entre los dos chips, el GND de los dos chips comparte la misma tierra y el TXD y el RXD están interconectados. La conexión cruzada aquí significa que el RxD del chip 1 está conectado al TXD del chip 2 y el RXD del chip 2 está conectado al TXD del chip 1. De esta forma, la comunicación de nivel TTL se puede realizar entre los dos chips .

4. El proceso detallado de la comunicación en serie USART

Diagrama de bloques UART (USART)

Este diagrama de bloques se divide en tres partes: superior, media e inferior.

En la parte superior del diagrama de bloques, los datos ingresan al registro de desplazamiento de recepción desde RX, luego ingresan al registro de datos de recepción y finalmente son leídos por la CPU o DMA; los datos se transfieren desde la CPU o DMA, ingresan al registro de datos de transmisión , y luego ingresa al cambio de transmisión. El registro finalmente se envía a través de TX.

Sin embargo, la transmisión y recepción de UART necesitan velocidad en baudios para controlar, ¿cómo se controla la velocidad en baudios?

Esto lo lleva a la parte inferior del diagrama de bloques Hay una flecha entrante tanto en el registro de desplazamiento de recepción como en el registro de desplazamiento de envío, que están conectados respectivamente al control del receptor y al control del transmisor. Los dos conectados son el reloj del receptor y el reloj del transmisor. En otras palabras, aunque la comunicación asíncrona no tiene una señal de sincronización de reloj, proporciona una señal de reloj para el control dentro del puerto serie. ¿Cuál es el control del reloj del receptor y del reloj del transmisor?

Se puede ver que el reloj del receptor y el reloj del transmisor están conectados a la misma unidad de control, lo que significa que comparten un generador de velocidad en baudios.

Cuando se trata de relojes, debe comprender: el reloj UART1 está montado en el bus APB2, por lo que la fuente de reloj es PCLK2 (alta velocidad); mientras que USART2 ~ 5 están montados en APB1, por lo que la fuente de reloj es PCLK1 .

En resumen, los periféricos en serie se dividen en parte de transferencia y almacenamiento de datos , parte de control del transceptor y parte de control de velocidad en baudios .

Parte de almacenamiento y transferencia de datos : (1) Cuando es necesario enviar datos, después de que el kernel o periférico DMA escribe los datos de la memoria en el registro de datos de envío TDR, los datos se cargarán automáticamente en el registro de desplazamiento de envío (este proceso genera TDR tiempo vacío TXE) Finalmente, se envía uno a uno a través de la línea del puerto serie TX (el evento de transmisión de datos completa TC se genera después de todas las transmisiones). El evento generado afectará el valor del registro de estado.

(2) Al recibir datos, es un proceso inverso. Los datos se ingresan desde la línea del puerto serie RX al registro de desplazamiento de datos de recepción, y luego se transfieren automáticamente al registro de datos de recepción RDR, y finalmente se leen en la memoria con un kernel comando o DMA.

Parte de control transceptor : controle el envío y la recepción reescribiendo los parámetros de control de tres registros de control USART (CR1, CR2, CR3) y un registro de estado (SR), como bit de paridad, bit de parada, etc., incluida la interrupción del control USART.

Parte de control de velocidad en baudios : la velocidad en baudios se puede cambiar controlando el reloj, y la velocidad en baudios es el número de símbolos binarios transmitidos por segundo, es decir, representa la velocidad de transmisión de datos. Configurar la velocidad en baudios es modificar el parámetro USARTDIV (el valor de división de frecuencia del reloj del puerto serie) en el registro de velocidad en baudios USART_BRR.

5. Cálculo de la velocidad en baudios

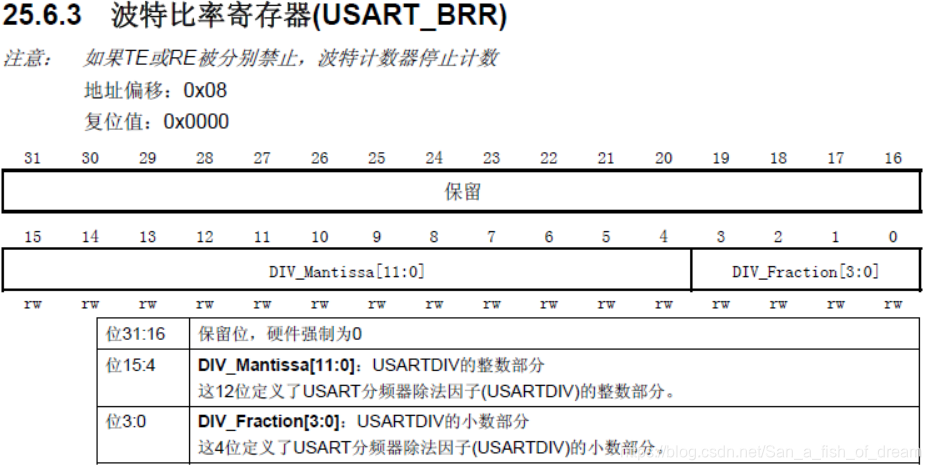

Hablando de velocidad en baudios, primero debe comprender el registro de velocidad en baudios

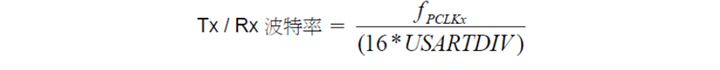

La fórmula para cambiar la velocidad en baudios modificando el valor de USARTDIV es la siguiente:

En la fórmula anterior, f PCLKx es la frecuencia de reloj del puerto serie. Siempre que obtengamos el valor de USARTDIV, podemos calcular la velocidad en baudios.

USARTDIV incluye dos partes en la definición del registro de velocidad en baudios: DIV_Mantissa [15: 4] (parte entera) y DIV_Fraction [3: 0] (parte decimal).

La fórmula de cálculo es: USARTDIV = DIV_Mantis + (DIV_Fraction / 16)

Nota : Cuando utilice la función de biblioteca al configurar el puerto serie, no necesita calcular el valor del registro, simplemente escríbalo directamente al configurar la velocidad en baudios.

6, funciones de biblioteca relacionadas con la operación del puerto serie

- 1 función de inicialización

void USART_Init(USART_TypeDef* USARTx, USART_InitTypeDef* USART_InitStruct);Función: se utiliza para la inicialización de la velocidad en baudios del puerto serie, la longitud de la palabra de datos, la paridad, el control de flujo de hardware y la habilitación del transceptor.

- 2 habilitar funciones

void USART_Cmd(USART_TypeDef* USARTx, FunctionalState NewState);

void USART_ITConfig(USART_TypeDef* USARTx, uint16_t USART_IT, FunctionalState NewState);

Función: El primero habilita el puerto serial y el segundo habilita las interrupciones relacionadas del puerto serial.

- 2 funciones de envío y recepción de datos

void USART_SendData(USART_TypeDef* USARTx, uint16_t Data);

uint16_t USART_ReceiveData(USART_TypeDef* USARTx);Función: El primero envía datos al puerto serie y el segundo recibe datos del puerto serie.

- 4 funciones de bit de estado

FlagStatus USART_GetFlagStatus(USART_TypeDef* USARTx, uint16_t USART_FLAG);

void USART_ClearFlag(USART_TypeDef* USARTx, uint16_t USART_FLAG);

ITStatus USART_GetITStatus(USART_TypeDef* USARTx, uint16_t USART_IT);

void USART_ClearITPendingBit(USART_TypeDef* USARTx, uint16_t USART_IT);

Función: Los dos primeros obtienen (o borran) el bit de bandera de estado y los dos últimos obtienen (o borran) el bit de bandera de estado de interrupción.

7. Pasos generales para el funcionamiento del puerto serie

(1) Activar reloj

Función de llamada: RCC_APBxPeriphClockCmd (),

Incluyendo la habilitación del reloj GPIO , la habilitación del reloj del puerto serie , si el pin está multiplexado, también habilite el reloj AFIO .

Ser perfeccionado

(2) Configurar pines GPIO

Función de llamada: GPIO_Init ()

Multiplexación de pines periféricos USART

Cuando se usa USART, GPIO a veces necesita multiplexación de pines (reasignación), entonces, ¿cómo juzgar si se requiere reasignación? Consulte el contenido relacionado de la configuración de multiplexación de pines (se agregará)

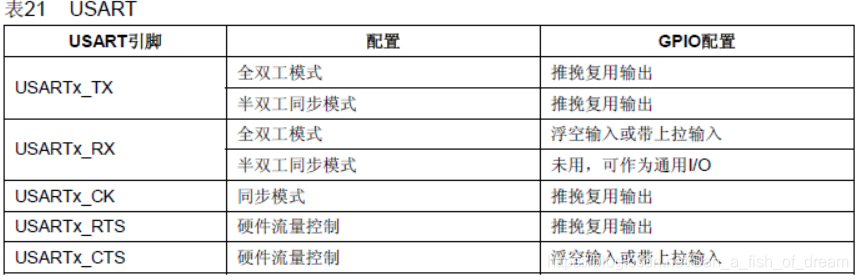

La siguiente figura describe la configuración de pines de USART:

En el libro de texto, los parámetros de inicialización del pin multiplexado son: el pin TX es una salida push-pull multiplexada y la velocidad de conmutación es 50MHZ; el pin RX es una entrada flotante y la velocidad de conmutación no está configurada:

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9; //TX引脚为PA9

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //复用推挽输出

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(USART1,&GPIO_InitStructure);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10; //RX引脚为P10

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING; //浮空输入

GPIO_Init(USART1,&GPIO_InitStructure);

(3) Configure la prioridad de interrupción y habilite la interrupción (este paso solo es necesario si necesita activar la interrupción)

Función de llamada: NVIC_Init (); USART_ITConfig ();

Ser perfeccionado

Nota : Si el dispositivo relevante necesita usar la función de interrupción, la prioridad de interrupción debe configurarse antes de que se habilite el dispositivo y la interrupción del dispositivo debe estar habilitada.

(4) Inicialice los parámetros del puerto serie y habilite el dispositivo serie

Función de llamada: USART_Cmd ();

Ser perfeccionado

(5) Función de manejo de interrupciones de escritura

Función de llamada: USARTx_IRQHandler ();

Transmisión y recepción de datos en serie. Función de llamada: USART_SendData (); USART_ReceiveData ();

Obtener el estado de transmisión del puerto serie. Función de llamada: USART_GetFlagStatus (); USART_ClearITPendingBit ();

Ser perfeccionado

Al escribir una función de servicio de interrupción, a menudo se obtienen los datos del bit de estado relevante para determinar si se genera una interrupción. Por lo tanto, es necesario tener una cierta comprensión del registro de estado.

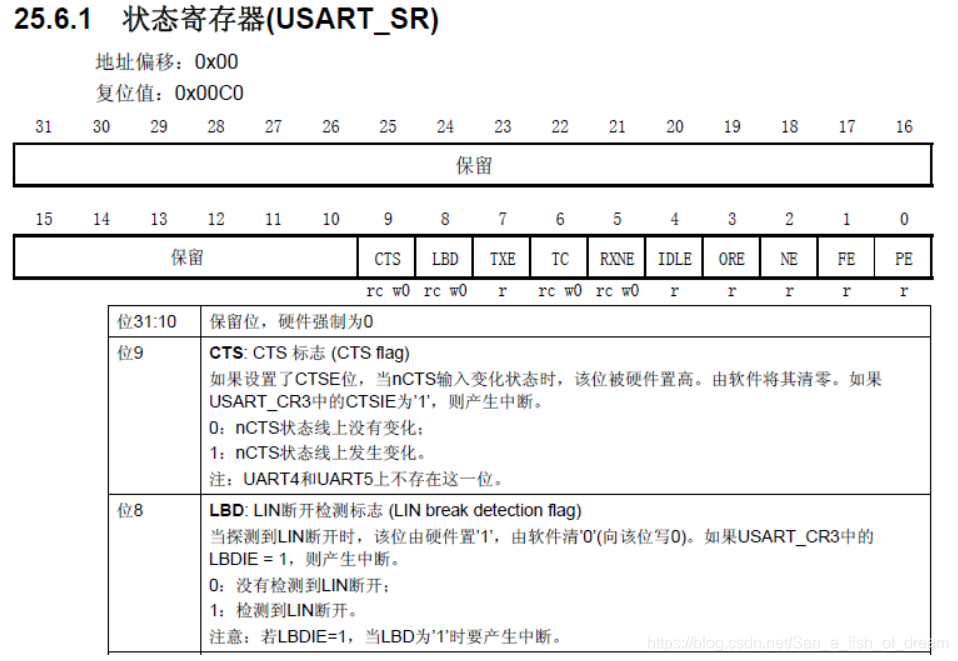

Registro de estado (USART_SR)

El registro de estado es adecuado para detectar el estado del puerto serie en este momento. Los estados que puede detectar son: enviar bit de registro vacío, enviar bit completo, leer bit de registro de datos no vacío, detectar bit inactivo de la línea principal, error de sobrecarga, etc.

Aquí nos centramos principalmente en dos bits: RXNE y TC (los dígitos 5 y 6).

RXNE (el registro de datos de lectura no está vacío) : cuando este bit se establece en 1, significa que se han recibido datos y se pueden leer (es decir, los datos del registro de desplazamiento RDR se transfieren al registro USART_DR). Lo que debe hacer en este momento es leer USART_DR lo antes posible para borrar este bit, o puede escribir 0 en este bit para borrarlo directamente.

TC (transmisión completa) : cuando este bit se establece en 1, significa que se han transmitido los datos en USART_DR. Si se establece una interrupción con este bit, se generará una interrupción. También hay dos formas de borrar este bit: leer USART_SR y escribir USART_DR; escribir 0 directamente en este bit.