USI0 recibir datos asincrónica

Al recibir una estructura de datos externa, UART incluye un aparato de reloj y recuperación de datos. lógica de recuperación de reloj síncrono para el reloj de tasa de bits generada internamente y estructuras de datos asíncronos introducidas de pin RXD0 continua.

De acuerdo con la introducción de muestras lógica de recuperación y filtrado de paso bajo, lo que puede eliminar la interferencia pies RXD0

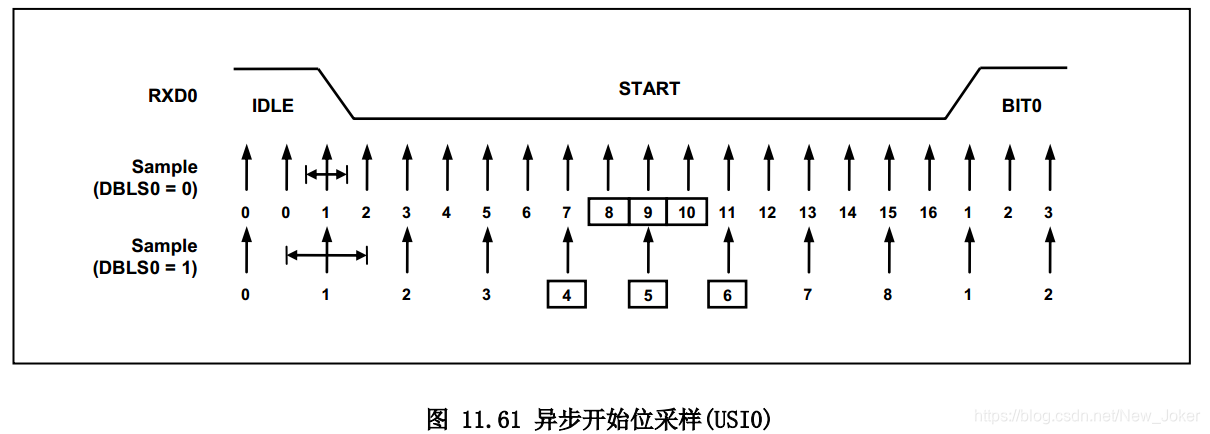

A continuación se ilustra un procedimiento de la trama entrante bit de inicio muestreado. tasa de muestreo de 16 veces la velocidad de transmisión cuando el modo normal. Cuando el modo de doble velocidad (DBLS0 = 1) 8 veces, y la flecha horizontal indica la variación de sincronización debido al muestreo asíncrono, nota que el modo de doble velocidad mayor parte del tiempo se muestran.

Cuando la recepción de habilitación (RXE = 1), los intentos lógicos de extracción de reloj para encontrar un cambio a través de mayor a menor en RXD0, que es una condición del bit de inicio. Cuando se detecta un cambio en el alto a bajo RXD0, el muestreo modo de lógica normal de recuperación de reloj es 8,9 y 10 para detectar si un bit de inicio válida. Si la muestra a una pluralidad de tanto un nivel lógico bajo, se considera para ser una señal de arranque válida, mientras que el reloj interno generado en la sincronización de los datos entrantes.

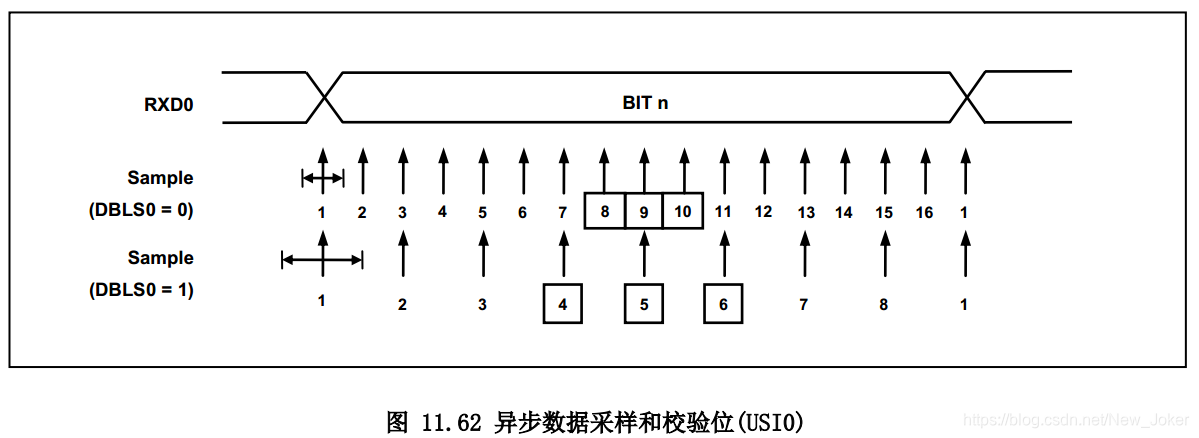

Como se describió anteriormente, cuando se recibe el bit de inicio y la sincronización de reloj, la transferencia de datos comienza. Proceso de adquisición de datos y el proceso de adquisición del reloj son similares. Cuando el bit de datos en modo normal para cada cobertura lógico muestra introducida 16 veces, ocho veces el modo de velocidad de doble muestreo. 8,9,10 modo normal cuando el valor de datos muestreados determinado. Si la muestra a la pluralidad de dos de bajo nivel, el bit que está recibiendo un '0' lógico si más de dos muestras a un nivel alto, se considera que es un '1' lógico. proceso que cubre de datos se ha repetido hasta e incluyendo una parada completa la recepción de bits de datos se ha completado. Valor secuencia de bits decisión almacenado en el registro de desplazamiento. Tenga en cuenta que sólo el primer receptor es un bit de parada. Después de recibir el primer bit de parada interna, el receptor entra en un estado de espera inactivo durante un bit de inicio.

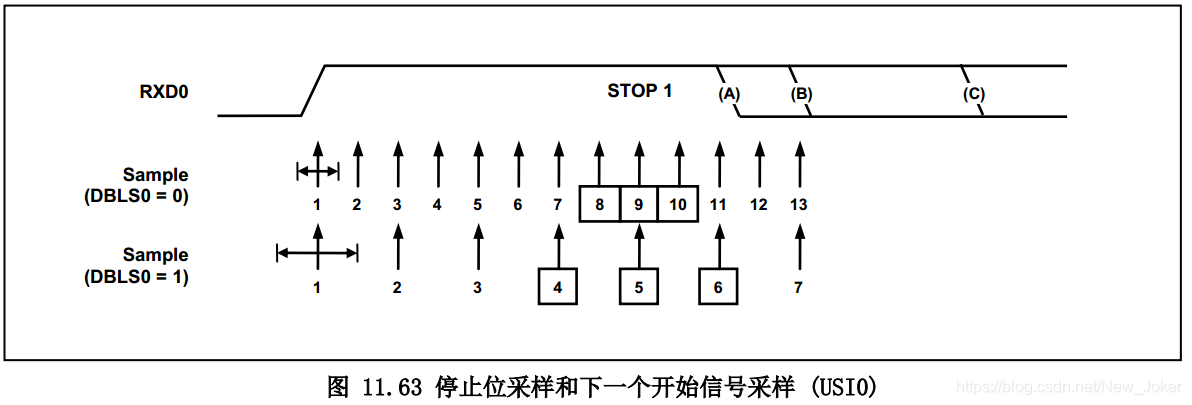

Detectar el bit de parada y el proceso reloj, similar al proceso de adquisición de datos. Es decir, se detecta si la muestra a más de dos o tres valores intermedios es alta, se considera bit de parada, de lo contrario, el indicador de bits FE. Después de determinar el primer bit de parada válido, el receptor entra en un modo inactivo de espera para el siguiente bit de inicio.