1. Project Hierarchy tree diagram

Preface

The recent project requires extracting all the registers in the project for post-processing. The process of extracting the project registers is recorded here.

1. Project Hierarchy tree diagram

First of all, you need to understand that it is wrong to extract the reg signal as a register directly from the RTL code. Because there are various instantiations in the code, the number of extracted registers is incorrect.

In order to correctly extract the actual synthesized registers, we need to obtain the Hierarchy level after engineering synthesis. This step can be exported in Verdi after VCS synthesis.

Right-click one of the modules and click Export Hierarchy to export.

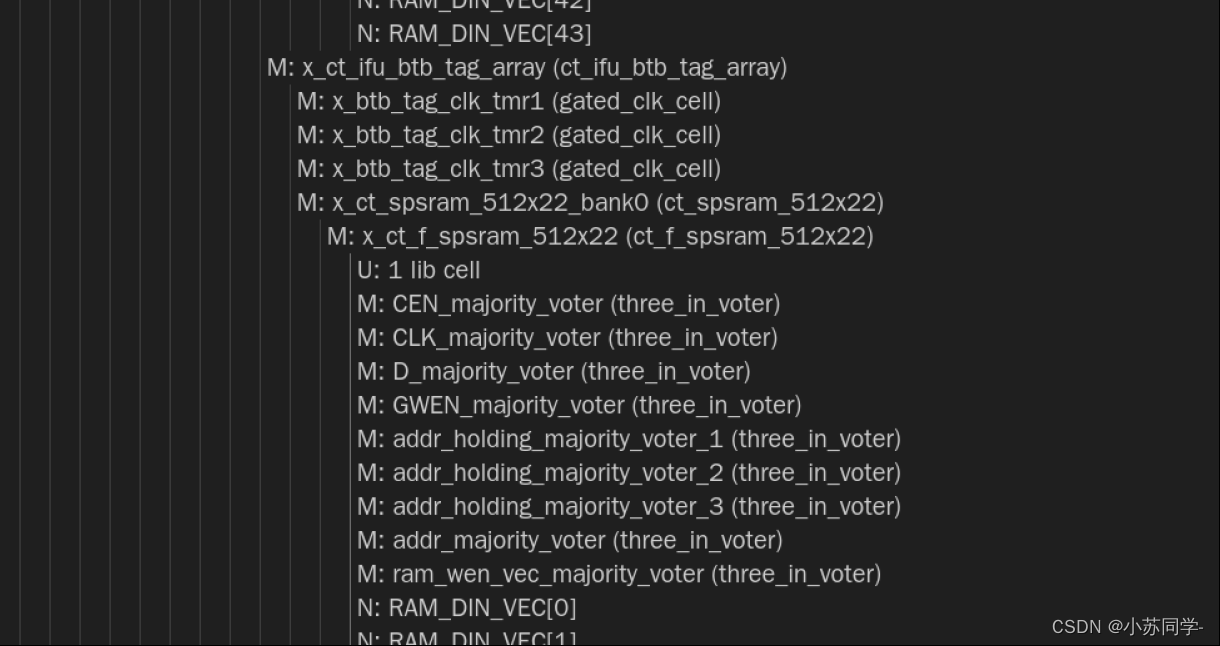

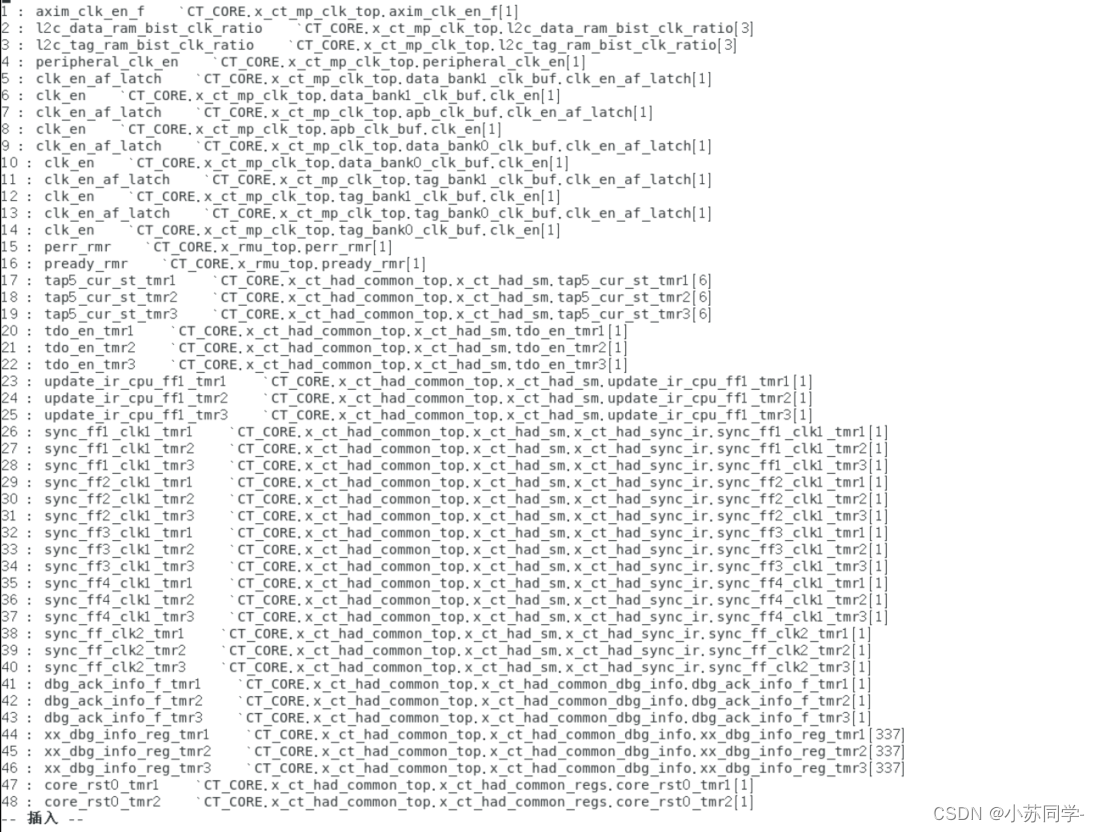

You can see that the generated Hierarchy diagram is as follows:

2. Reconstruction Project

1. Reconstruct the Hierarchy tree diagram

It is still difficult to extract the above dendrogram using a script, so we need to rebuild the dendrogram.

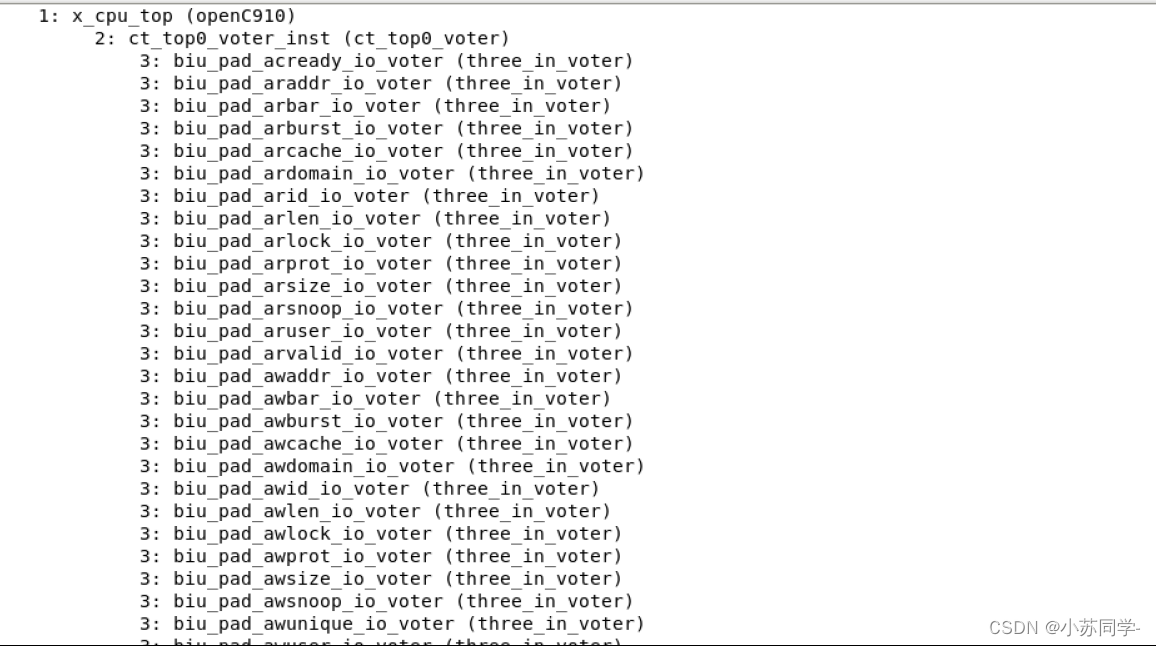

The specific principle is to use a script to replace M or N with 1-9 according to the hierarchical structure.

python3 replace.pyConvert as shown below:

2. Restructure the folder

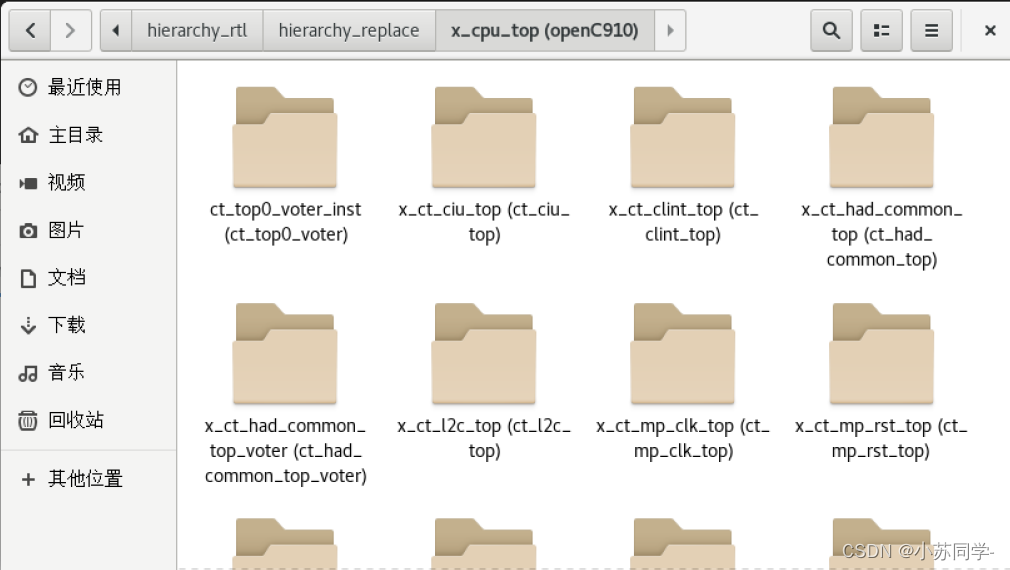

Based on the reconstructed tree diagram, a folder structure with Hierarchy is generated.

python3 mkdir.pyAs shown in the figure below, you can see that the file name consists of the instantiation name and the source module name:

3.mv RTL code

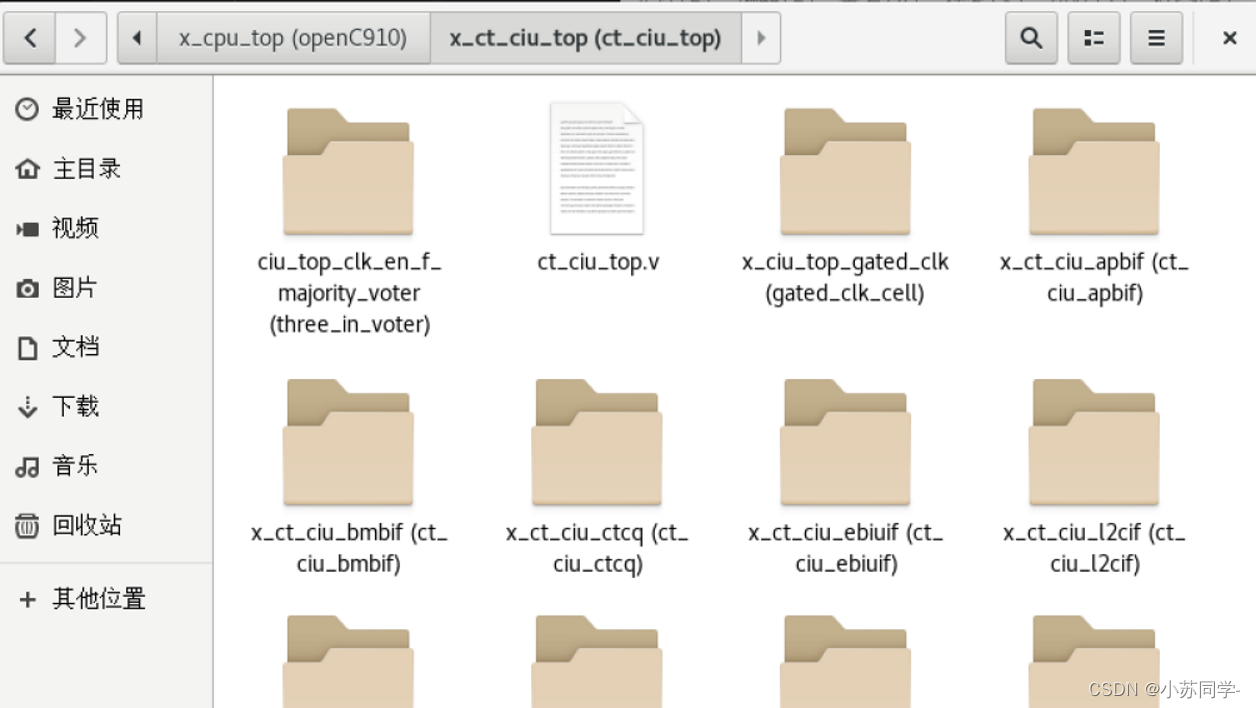

Extract the RTL code in the project, match the module name and the name in brackets, and put the corresponding RTL code into the specified folder.

python3 mv_rtl2folder.pyAs you can see, the script puts the corresponding RTL code into the folder corresponding to its Module.

3. Extract register

Extract the register according to your own needs. My purpose is to use it as a signal at the top level and count the number of registers, so it is generated as follows:

It should be noted here that register names may be repeated. In order to solve the repeatability problem, a self-check module is added to the script, which will detect repeated signals and add count at the end of the sequence, thus solving the repeatability problem.