For the register, if the initial value is not explicitly specified, Vivado will set the appropriate initial value according to its type (FDCE/FDRE/FDPE/FDRE). Some engineers like to use the reset signal to power-on reset all registers so that they reach the desired initial state before processing the data. But this will have a disadvantage that the fan-out of the reset signal is large, which consumes a lot of wiring resources and even causes wiring congestion. So can the register output the expected value without resetting after power-on? The answer is yes.

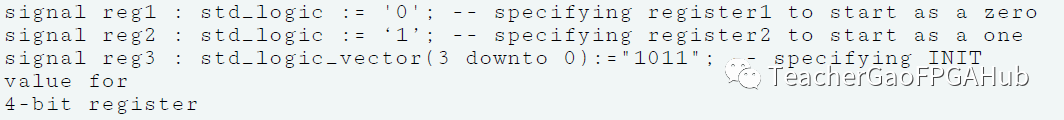

Xilinx also recommends that for synchronization components, it is best to set their initial values. Here we take the most commonly used registers as an example. If you are using VHDL, you can use the following method to set the initial value of the register, as shown in the figure below.

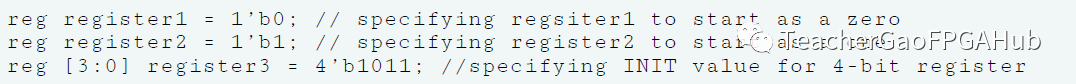

If you are using Verilog, you can use the following method to set the initial value of the register, as shown in the figure below.

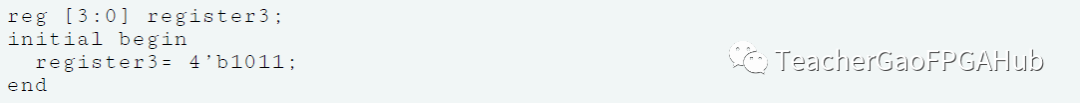

In addition, for Verilog, the initial value can also be set through initial, as shown in the figure below.

The advantage of adopting this method is that the synthesis tool is supported, so that these initial values will be written into the configuration file when the bit file is generated, and it will take effect after power-on, avoiding excessive fan-out caused by resetting; at the same time in simulation Time, it can also match the actual business.

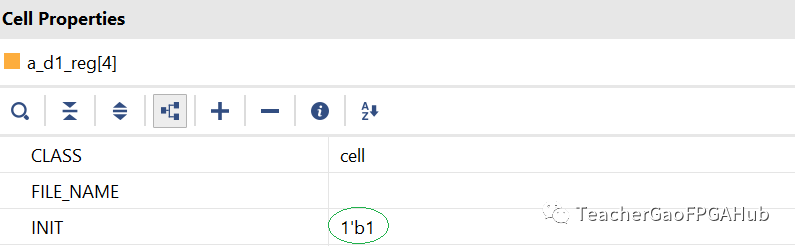

In order to verify whether this method is effective, you only need to open the synthesized .dcp, find the corresponding register, and check the value of the property INIT in its Property window, as shown in the figure below.