The team undertakes embedded linux software and hardware development, machine vision image processing, network streaming and other projects

WeChat ID: hgz1173136060

1 - 1 : the I2C bus knowledge

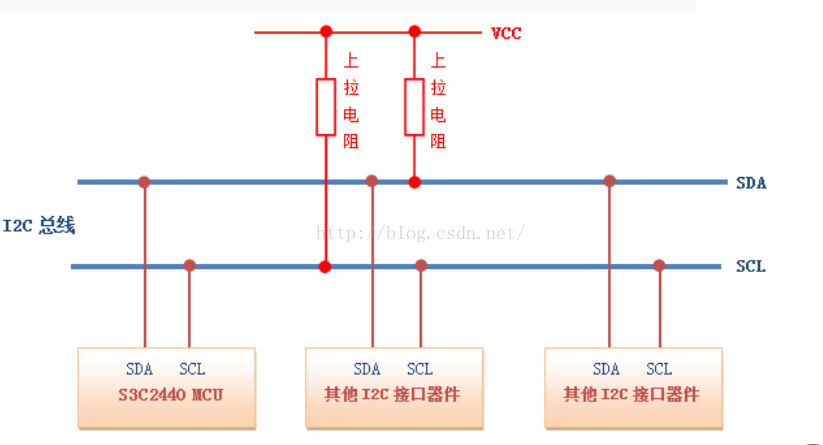

. 1 - . 1 - . 1 : the I2C bus physical topology

The I2C bus is very simple in physical connection. It is composed of two-wire serial buses , SDA ( serial data line ) and SCL ( serial clock line ) and pull-up resistors . The communication principle is to generate the signals required by the I2C bus protocol for data transfer by controlling the high and low timing of the SCL and SDA lines . When the bus is idle , the pull-up resistor keeps both the SDA and SCL lines high . The output terminal of each device connected to the bus must be an open drain output or open collector output structure (OC gate )

. 1 - . 1 - 2 : the I2C bus characteristics

Each device on the I2C bus can be used as a master device or a slave device. The master can control data transmission and clock frequency, and there can only be one master at any time . And each device will correspond to a unique address ( can be known from the data manual of the I2C device ) , the master and slave devices use this address to determine which device to communicate with. In normal applications, we bring the CPU with I2C The bus interface module acts as the master device, and all other devices connected to the bus as slave devices. The number of devices that can be connected to the I2C bus is limited by the maximum capacitance of the bus of 400pF . If the device of the same model is connected, it is also limited by the device address bit. I2C bus data transfer rates up to in standard mode 100kbit / S , up to the fast mode 400kbit / S , up to high-speed mode 3.4Mbit / S . Generally , the adjustment of the transmission rate is realized through the programmable clock of the I2C bus interface, and it is also related to the resistance of the connected pull-up resistor. The two-way data transmission between the master device and the slave device on the I2C bus takes bytes (8 bits ) as the unit. Half duplex

. 1 - . 1 - . 3 : the I2C bus protocol

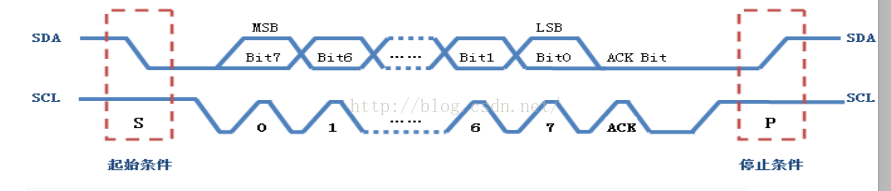

The I2C protocol stipulates that the transmission of data on the bus must take a start signal as the start condition and an end signal as the stop condition of the transmission. The start and end signals are always generated by the master device.

Idle: SCL high level, SDA high level

Start condition: SCL high level, SDA falling edge

Stop condition: SCL high level, SDA rising edge

Busy Status: ongoing data transmission from the master device alone accounted bus, other devices can not access

Data is valid: During the high level of SCL , SDA remains stable and data is valid. The change of SDA can only occur during the low level of SCL

ACK signal: During data transmission, the receiving device generates an ACK signal every time it receives a byte of data , and sends a specific low-level pulse to the sending device to indicate that the data has been received.

as the picture shows:

Data transmission : byte as a unit, one pulse, one data bit, transmission direction: sequential transmission from high byte to low byte After one byte is transmitted, the slave device sends a low level response bit

After understanding the start condition and stop condition, let's take a look at how the data transmission is carried out in this process. As we mentioned earlier, data transmission is in bytes . When the master device generates each clock pulse on the SCL line , it will transmit a data bit on the SDA line . When a byte is transmitted in the order of data bits from high to low , the slave device will pull the SDA line low. , And send back an acknowledge bit to the master device , at this time it is considered that a byte is truly transmitted. Of course, not all byte transmissions must have an acknowledge bit. For example, when the slave device can no longer receive the data sent by the master device, the slave device will return a negative acknowledge bit. The process of data transmission is shown in the figure :

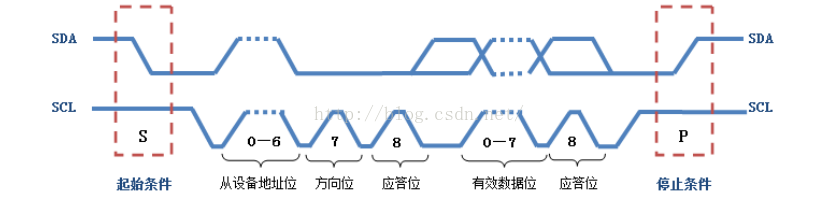

Device address: the upper 7 bits of the device address, the lowest bit is the read/write bit. 0 means that the master device writes data to the slave device, 1 means that the master device reads data from the slave device. As we mentioned earlier, each device on the I2C bus corresponds to a unique address. The data transfer between the master and slave devices is It is based on the address, that is, the master device must specify the address of the slave device before transmitting valid data. The process of specifying the address is the same as the process of data transmission above, except that the address of most slave devices is 7 bits. , And then the protocol stipulates to add a least significant bit to the address to indicate the direction of the next data transmission, 0 means the master device writes data to the slave device, 1 means the master device reads data to the slave device. as the picture shows:

. 1 - . 1 - . 4 : the I2C bus operation

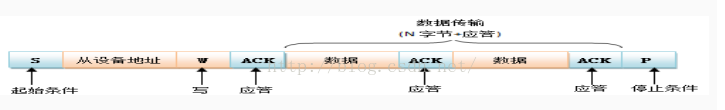

The operation of the I2C bus is actually the read and write operation between the master and slave devices. It can be roughly divided into the following three operating situations: First, the master device writes data to the slave device . The data transmission format is as follows:

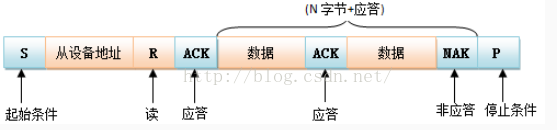

Second, the master device reads data from the slave device . The data transmission format is as follows:

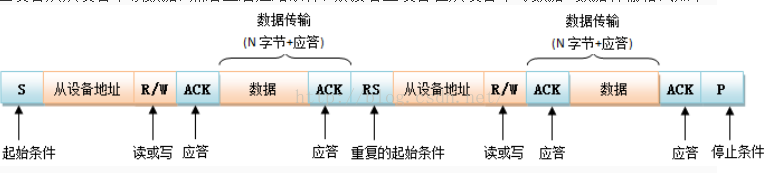

Third, the master device writes data to the slave device, and then restarts the initial condition, and then reads data from the slave device; or the master device reads data from the slave device, then restarts the initial condition, and then the master device sends Write data from the device. The data transmission format is as follows:

The third operation is in a single master system, where the repeated start condition mechanism is more efficient than stopping the transmission with STOP and then opening the bus again.