-

ARM处理器工作状态及工作模式

-

ARM处理器的寄存组织

-

ARM处理器的异常

1.1处理器的工作状态

处理器的三种状态:

ARM状态:所有指令均为32位宽度

Thumb状态:指令为16位,代码密度更大,占用内存小

调试状态:处理器停机调试时

除Cortex-M系列处理器外,所有ARM处理器复位后开始执行代码是总是ARM状态

Cortex-M处理器只有Thumb-2指令集,所以没有ARM状态

ARM与Thumb间的转换:

1)BX指令

ARM状态 -> Thumb状态:将操作数寄存器最低位设置为1

2)BX指令

Thumb状态 -> ARM状态:将操作数寄存器最低位设置为0

1.2处理器的工作模式

| 工作模式 | 功能说明及CPSR[M4:M0] |

|---|---|

| 用户模式User | 程序正常执行工作状态 10000 |

| 快速中断模式FIQ | 处理高速中断,用于高速数据传输或通道处理 10001 |

| 外部中断模式IRQ | 普通中断处理 10010 |

| 管理模式SVC | 操作系统的保护模式,处理软中断SWI 10011 |

| 中止模式ABT | 处理存储器故障,实现虚拟存储器和存储器保护 10111 |

| 未定义指令模式UND | 处理未定义的指令陷阱,用于支持硬件协处理器仿真 11011 |

| 系统模式SYS | 运行特权级的操作系统任务 11111 |

2.1ARM状态下寄存器组织

ARM处理器共有37个寄存器,包括31个通用寄存器(含PC)和6个状态寄存器

1)通用寄存器(均为32位)

R0-R7:不分组寄存器

R8-R12:共两组 10个寄存器,标有fiq的代表FIQ专用,与其他模式地址重叠但内容不冲突

R13-R14:除用户模式和系统模式分别为SP(堆栈指针)和LR(程序链接寄存器)

2)状态寄存器

CPSR和SPSR

状态码格式:

30 29 28 27 26 …8 7 6 5 4 3 2 1 0

N Z C V Q … … . I F T M4 M3 M2 M1 M0

CPSR分为4个域:

标志域F(31:24)

状态域S(23:16)

扩展域X(15:8)

控制域C(7:0)

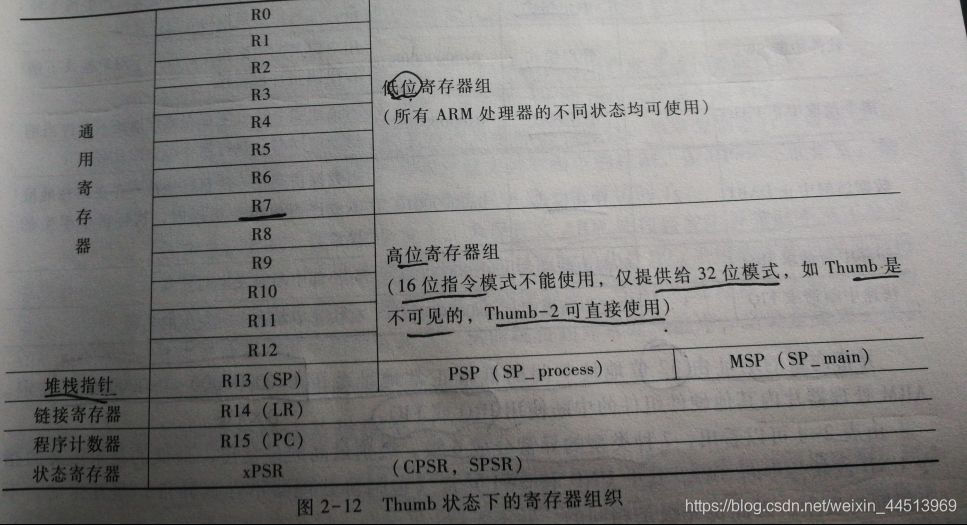

Thumb状态下的寄存器组织

高位寄存器R8-R12在Thumb状态下不可见

2.3带MMU的ARM处理器中的控制寄存器

控制寄存器CP15:控制C0-C15共16个系统控制寄存器

3.1ARM 的异常

程序正常执行的过程中,每执行一条ARM指令PC值加4,每执行一条Thumb指令PC值加2

1)ARM异常种类,向量及优先级

- 复位RESET:管理模式,0x00000000

- 数据访问中止DABT:中止模式,0x00000010

- 快速中断请求FIQ:快速中断模式,0x0000001C

- 外部中断请求IRQ:外部中断模式,0x00000018

- 指令预取中止PABT:中止模式,0x0000000C

- 软件中断SWI:管理模式,0x00000008;未定义的指令UND:未定义指令中止模式,0x00000004

2)ARM异常中断响应过程

- 将CPSR的值保存到将要执行的异常中断对应的各自SPSR中

- 设置当前状态寄存器CPSR的相应位

设置CPSR中M4-M0进入相应工作模式

- 将引起异常指令的下一条地址(断点地址)保存到新的异常工作模式LR(R14),

- 给程序计数器PC强制赋值,转入向量地址

3)从异常处理程序返回

复位发生后,系统自动从0x00000000开始重新执行程序,故复位异常处理程序执行完无需返回

- 恢复原来被保护的用户寄存器

- 将CPSR_mode寄存器值复制到CPSR中

- 根据异常类型将PC值恢复为断点地址

- 清除CPSR中的中断禁止标志I,F,开放外部中断IRQ和快速中断FIQ

程序状态字和断点地址的恢复必须同时进行

为使ARM处理器发生异常时不至于处于未知状态,首先要进行异常向量的初始化处理