虽然写这个博客主要目的是为了给我自己做一个思路记忆录,但是如果你恰好点了进来,那么先对你说一声欢迎。我并不是什么大触,只是一个菜菜的学生,如果您发现了什么错误或者您对于某些地方有更好的意见,非常欢迎您的斧正!

目录

第一章重点回顾:

MOV AX,2000H; 将16位数据2000H传送到AX寄存器

MOV AL,20H; 将8位数据20H传送到AL寄存器

MOV AX,BX; 将BX寄存器的16位数据传送到AX寄存器

MOV AL,[2000H]; 将2000H单元的内容传送到AL寄存器

需要注意的是:

(1)两个存储单元之间不能直接传送数据,即:MOV指令只允许一个操作数在存储器中。MOV [SI],[2000H];这是错误的

(2)MOV指令中立即数不能直接传送给段寄存器(CS、DS、SS、ES)和IP;段寄存器之间不能直接传送。MOV IP,2000 H ;这是错误的

(3)CS和IP不能作为目的操作数。MOV CS,AX ;这是错误的

(4)MOV指令中立即数不能作目标操作数。MOV 2000H,[SI] ;这是错误的

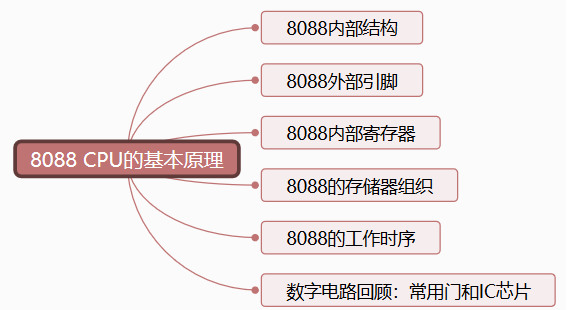

第一节 8088 CPU的基本原理

8086/8088 CPU的特点

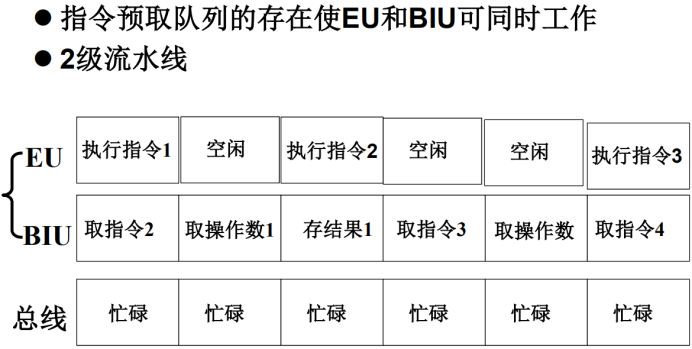

①采用并行流水线工作方式

②支持多处理器系统

③片内无浮点运算部件,浮点运算由数学协处理器8087支持

④对内存空间实行分段管理

|

|

|

8086 |

8088 |

| 相同点 |

寄存器 |

16位 |

|

|

|

地址线 |

20根,1MB内存 |

|

| 差异 |

数据总线 |

16根 |

8根 |

|

|

指令队列 |

6字节 |

4字节 |

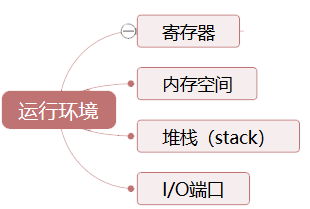

第二节 8088的运行(执行)环境

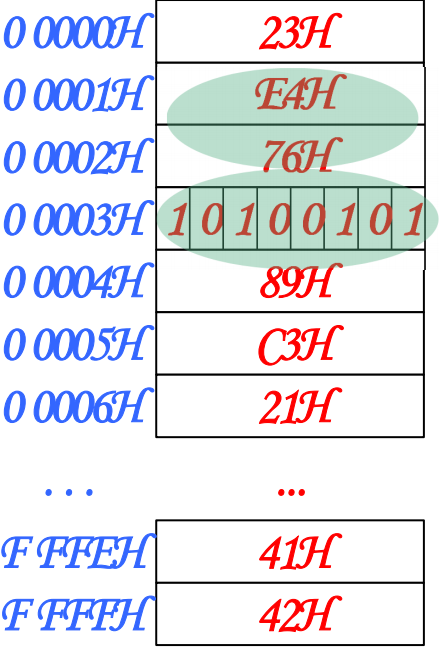

数据存放规律

①字节数据

一单元存放一个数:E4H存放在00001H单元

②字数据:2单元

2单元:“低对低,高对高”

字的地址:2个单元中的低地址

例:76E4H存放在00001H中

③机器指令(机器码):多个字节

按字节顺序地址递增存放

如:MOV BX,AX;89C3H ,4H单元

④字符串:多个字节

按字节顺序地址递增存放,同机器指令

例题:00002H存放的字节/字指令为多少?

字节:E476H

字:76H

堆栈

调用发生后,主程序在CPU中的运行环境被破坏

调用返回时,必须恢复主程序之前的运行环境

在子程序调用和中断服务时存储参数和现场数据。

堆栈的伸展方向:栈底的地址大,栈顶的地址小。

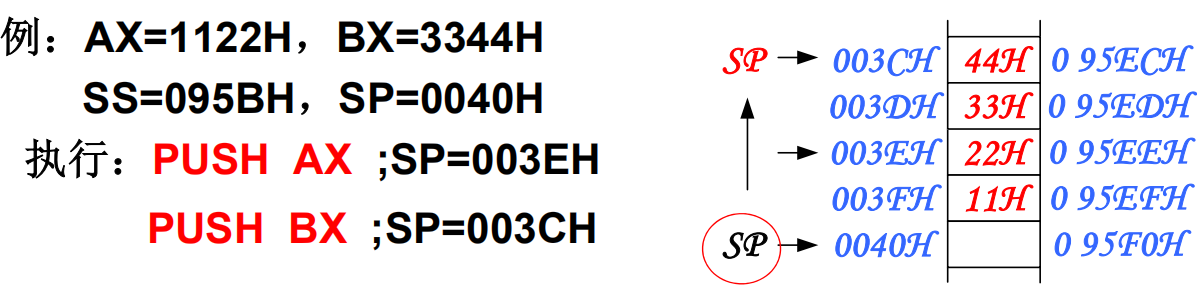

栈的操作(PC):

入栈:将一个数存入栈顶,并改变SP(变小)

PUSH SRC;SRC代表寄存器或存储单元地址

功能:将寄存器或存储单元的一个字压入堆栈

操作:“先减后入”:SP-1,字高位->[SP]

SP-1,字低位->[SP]

结果:SP-2,数据高对高,低对低存放。

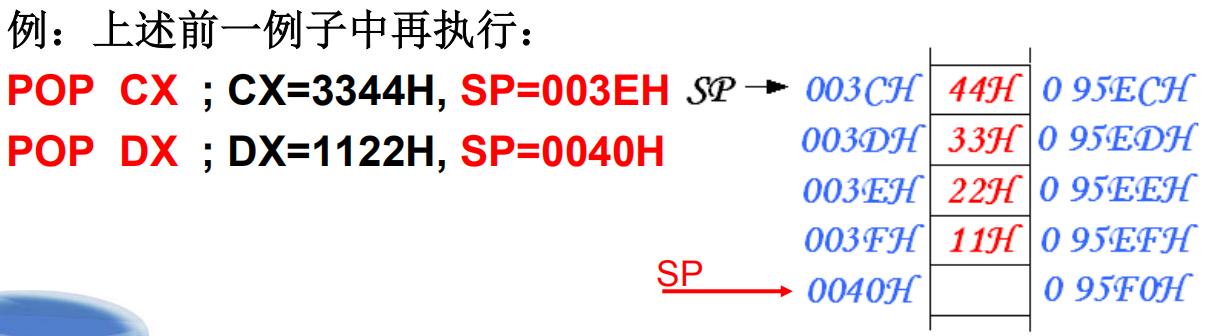

出栈:从栈顶读出一个数据,并改变SP(变大)

POP DST;DST代表寄存器或存储单元地址

功能:将栈顶的一个字传送到寄存器或存储单元地址中

操作:“先出后加”:[SP]->字低位,SP+1->SP

[SP]->字高位,SP+1->SP

结果:SP+2,数据低对低,高对高存放

Flag寄存器出/入栈

命令格式:

PUSH F;F入栈,SP-2 -> SP

POP F;F出栈,SP+2 -> SP

功能:保护和恢复状态标志寄存器Flag

注意:

①栈操作均以字为单位,如PUSH AL,POP DH 均错。

②PUSH与POP成对,避免堆栈溢出或程序出错。

③堆栈实为内存区,还可按数据区的方法对其操作。

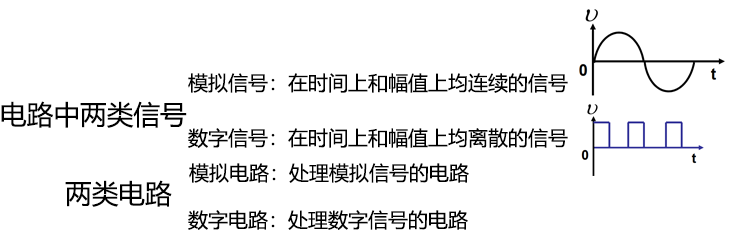

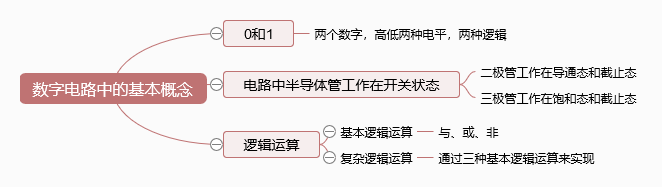

第3节 数字电路、常用门和IC芯片

复合逻辑运算:基本逻辑运算的复合

复合逻辑门:实现复合逻辑运算的电路

与非门 或非门 异或门 同或门

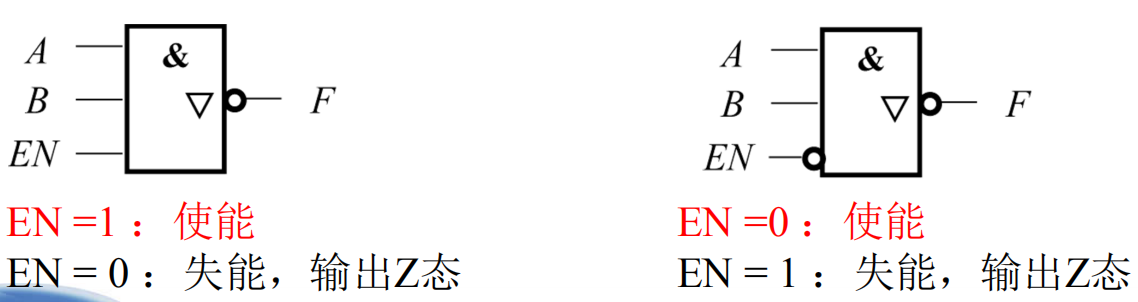

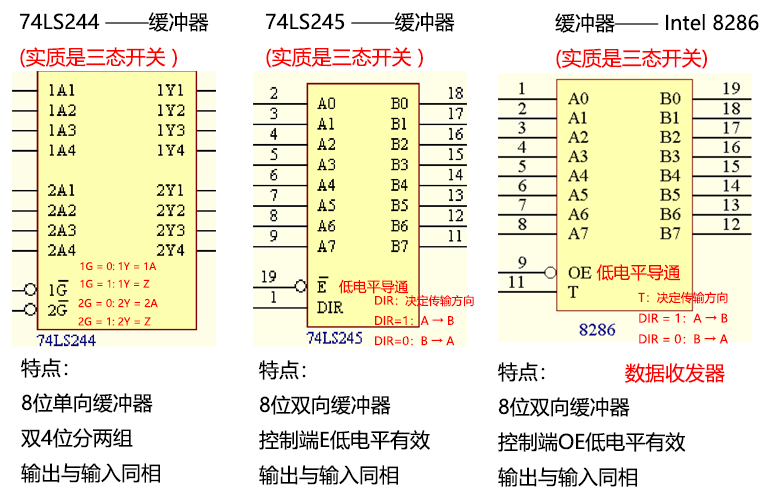

三态门(TS门,有▽符号):0、1、Z(高阻状态或禁止态)

在普通门增加一个使能端(EN)

EN有效:门按原逻辑工作,输出0或1

EN无效:门输出Z(高阻态)

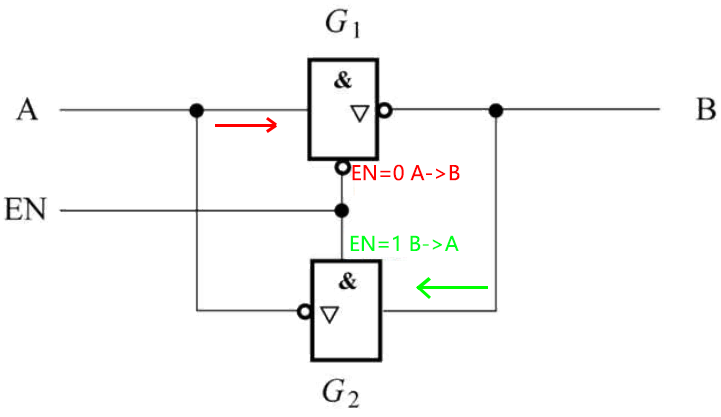

三态门的典型应用:

数据传输方向控制

总线存取控制

模拟开关

总线存取控制:多个设备在数据总线上,必须控制存取权限,任何时候只能让最多1个设备逻辑连接(占用)总线。

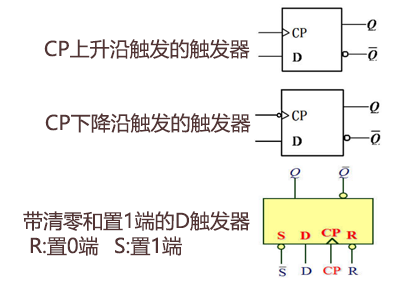

| 触发器 |

D触发器 |

| 功能和特点 |

能存储一位二进制信息的单元电路 |

|

|

用于信号保持 |

|

|

用于导通开关 |

|

|

特点:0-1双稳态电路 |

| 触发器与门的联系 |

联系:触发器是在门电路的基础上引入反馈构成的 |

|

|

门是组合电路,触发器是时序电路 |

| 触发器的种类 |

基本RS触发器 |

|

|

同步RS触发器 |

|

|

主从型JK触发器 |

|

|

维持阻塞型D触发器 |

|

|

T和T’触发器 |

工作方式

CP上升沿 锁存D(阻塞D),上升沿后Q端保持不变。

触发器在CP脉冲的上升沿产生状态变化:Q=D,而在上升沿后,D端信号变化对触发器输出状态没有影响。触发器的次态取决于CP脉冲上升沿时的D信号。

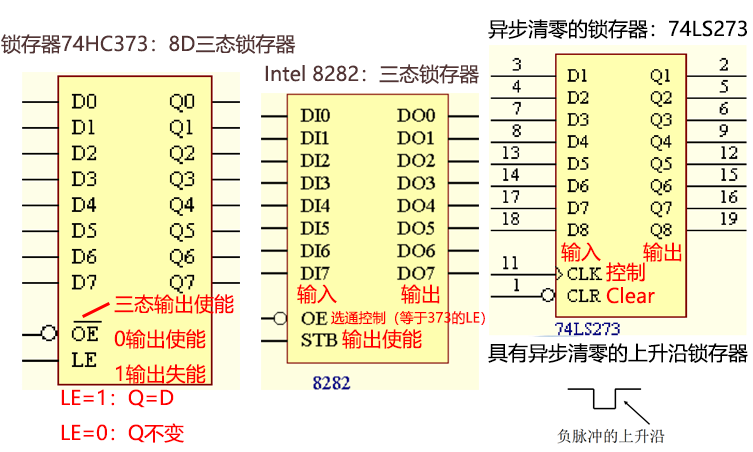

锁存器

锁存器和触发器有类似的功能:

①具有0和1两个稳状,能自行保持

②能存储一位二进制码

区别:锁存器对电平敏感,触发器对边沿敏感。

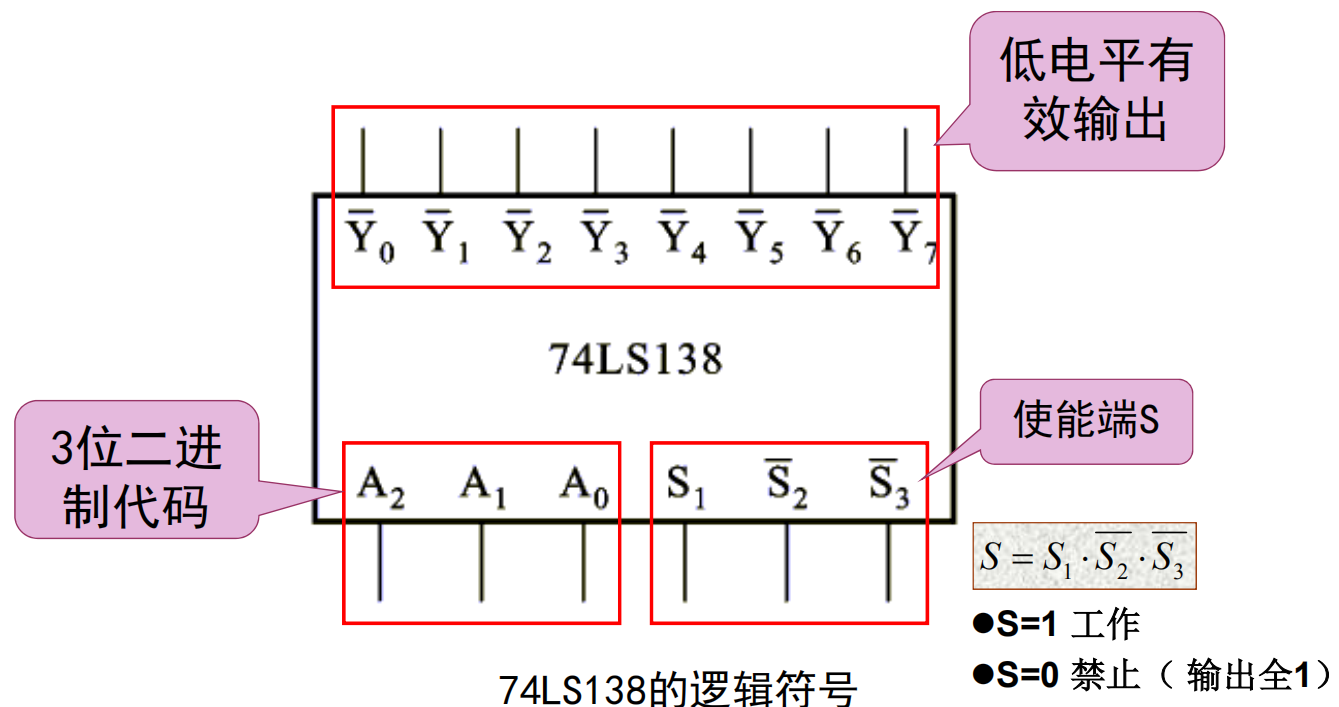

基本芯片——译码器

功能:将某个二进制数据的含义“翻译”出来,指示唯一的某1个事件有效。

结构:n位输入脚,2^n个输出脚(每脚对应1个事件)

特点:每次译码,仅唯一的1个输出引脚为有效电平

3-8译码器

结构:3个输入引脚,8个输出引脚

功能:输入3位二进制代码A2A1A0(000~111),在唯一的某个输出引脚上出现有效电平(低)

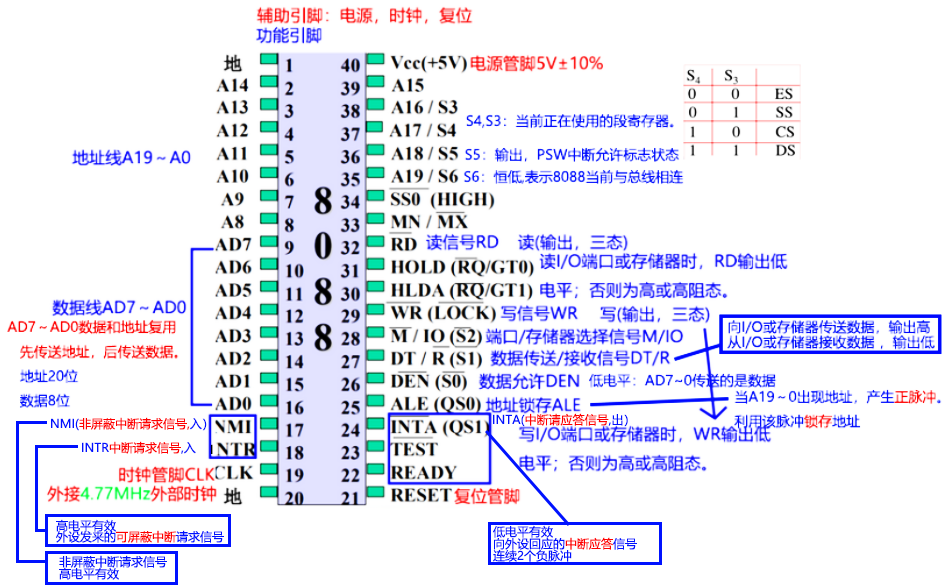

第4节 8088微处理的外部结构

(废话:感觉学微机这门课真的很云里雾里,唉。)

8088的电气特性

电源:5V±10%的条件下能够工作

输入特性:

低电平:0.8V(0)

高电平:2.0V(1)

输出特性:

低电平:0.45V(0)

高电平:2.4V(1)

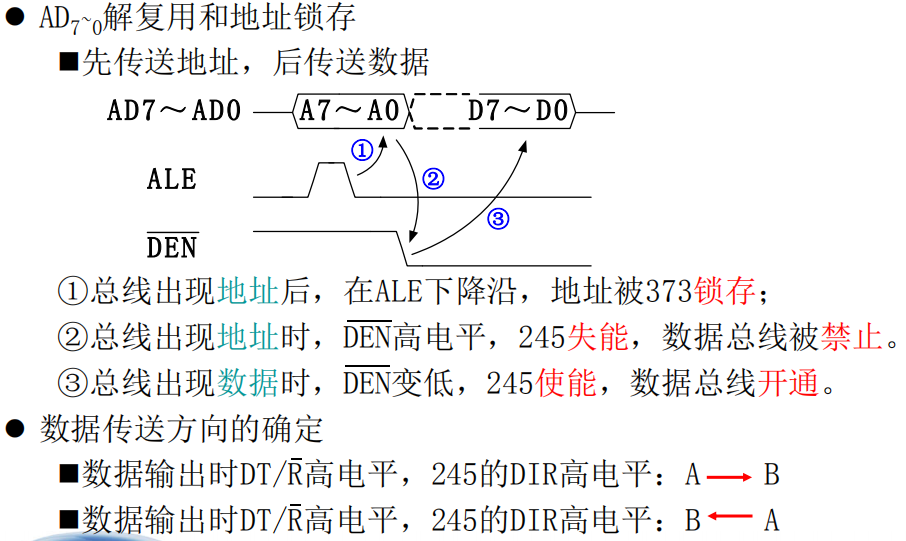

8088系统总线的形成

主要解决:

实现地址总线(AB),数据总线(DB)和控制总线(CB)

地址与数据的分离

地址锁存

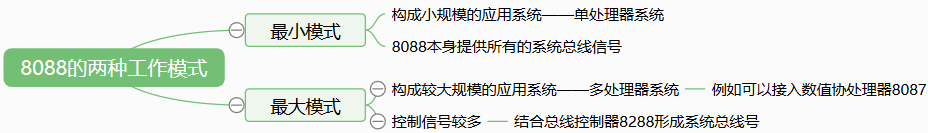

这两种模式利用MN/MX(33号)引脚区别:

·MN/MX接高电平为最小模式

·MN/MX接低电平为最大模式

第5节 8088处理器时序和总线周期

时序(概念):信号随时间和事件变化的顺序或规律

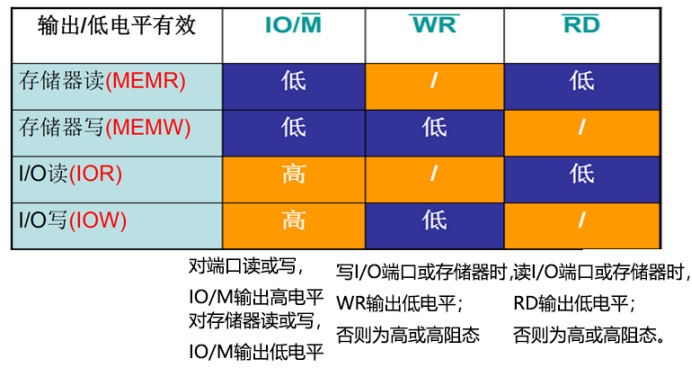

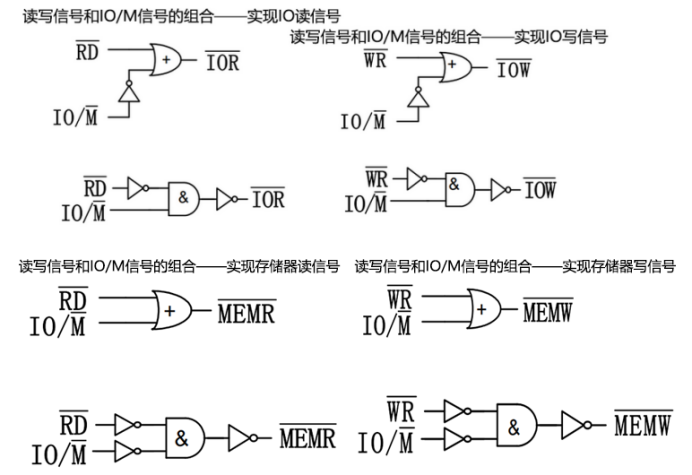

可用时序描述CPU通过总线对外实施的各种操作(总线操作):

存储器读操作 I/O读操作

存储器写操作 I/O写操作

中断响应操作 总线请求及响应操作

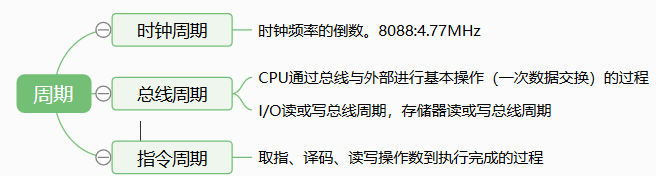

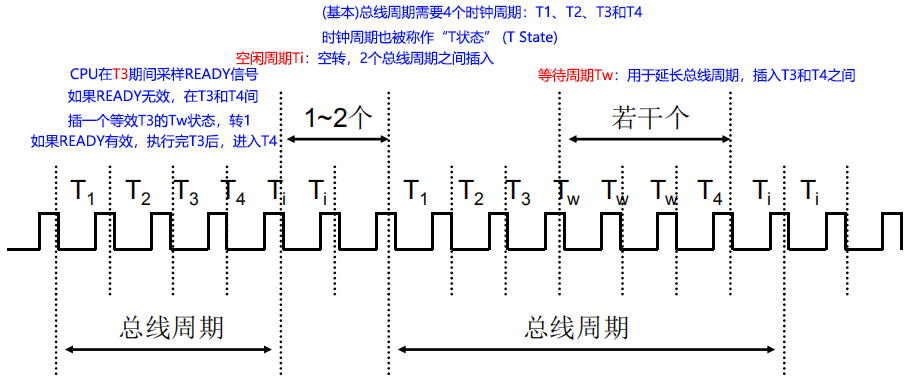

指令周期 > 总线周期 > 时钟周期

总线周期(即总线操作)产生的例子

指令取指阶段:存储器读总线周期(读取指令代码)

源操作数是存储单元的指令:存储器读总线周期

目的操作数是存储单元的指令:存储器写总线周期

执行IN指令:I/O读总线周期

执行OUT指令:I/O写总线周期

CPU响应可屏蔽中断:中断响应总线周期

空闲总线周期

CPU不执行任何存储单元或I/O操作,则执行空闲周Ti(Idle)

基本的总线周期:

存储器读 存储器写 I/O端口读 I/O端口写 中断响应

第6节 IA-32发展历史

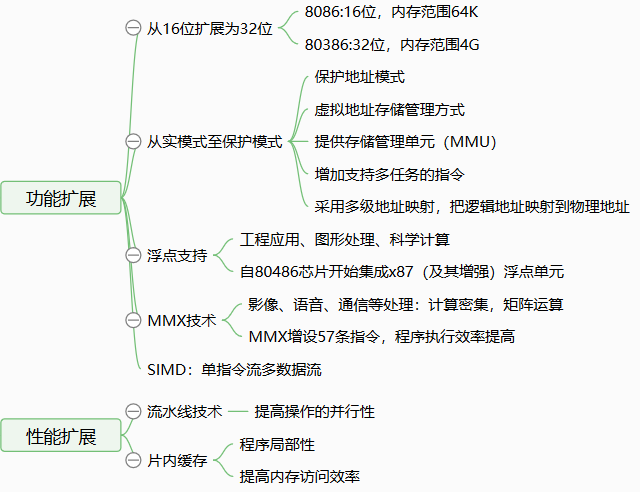

IA-32微处理器是8086/8088的延伸