多数表决器指一个决策里面大多数人同意即“1”,事件就为“1”,类似于以前的举手表决,只是现在利用电子手段来实现,主要是用来表达参与者是赞成还是发对,可以很快的计算出投票结果。

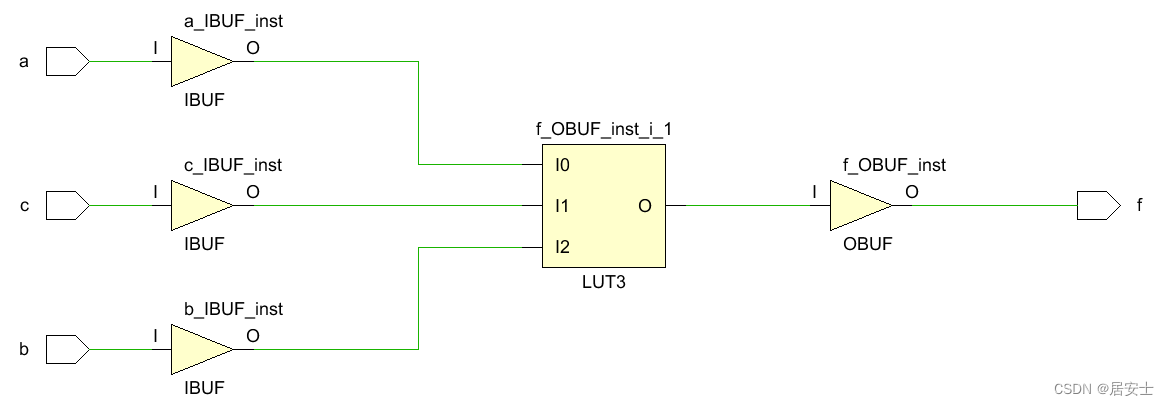

假如有3个输入abc,输出为f,真值表如下:

![]()

用卡诺图去化简(卡诺图讲解可参考一分钟掌握卡诺图化简法_居安士的博客-CSDN博客)

最后我们得到结果是 f=ab+bc+ac

开始写代码:

module most(

input a,

input b,

input c,

output f

);

assign f=a&b|a&c|b&c;

endmodule测试代码:

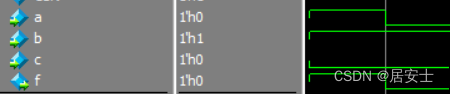

一开始a=1,b=1,c=0

后面叫a=0,b=1,c=0

module TB_most(

);

reg a;

reg b;

reg c;

wire f;

most inst_most(

.a(a),

.b(b),

.c(c),

.f(f)

);

initial begin

a=1;

b=1;

c=0;

#20;

a=0;

b=1;

c=0;

end

endmodule

根据测试结果 一开始f=1,之后f=0

多数表决器完成!

在这个的基础上,可以增加更多的人数的多数表决器