wx Gong Zhonghao: Chuangxiang Dialogue

Dialogue Send: Music Circuit

Obtenha o relatório completo em papel sem marca d'água (incluindo diagrama de circuito) gratuitamente

Diretório de artigos

1. Requisitos da tarefa de design

1. Tópico de design do curso

Projete um circuito de execução musical que possa reproduzir automaticamente a música escrita. É necessário tocar a música pelo alto-falante da caixa experimental e usar o diodo emissor de luz para exibir a batida da música.

(Funções adicionais: Este projeto adiciona muitas funções adicionais com base na realização de todas as funções exigidas pelo tópico. Todas as funções serão esclarecidas na "Visão Geral do Projeto de Engenharia", que é aqui declarada.)

2. Análise de design

(1) Princípio básico do circuito de reprodução de hardware de música

O princípio de som do circuito de hardware, a faixa de frequência do som é de cerca de dezenas a vários milhares de Hz, se o programa puder ser usado para controlar um determinado pino do FPGA chip para emitir uma onda retangular de uma certa frequência, conectado ao alto-falante pode emitir o som da frequência correspondente. Cada nota da música corresponde a uma determinada frequência, se você quiser que o FPGA emita notas diferentes, basta controlar a frequência da nota correspondente. A música é toda composta por uma série de notas, portanto emita a frequência correspondente a essas notas sucessivamente de acordo com a partitura da música, bastando enviar o tom de cada nota continuamente no alto-falante. Para tocar uma música com precisão, não basta apenas deixar o alto-falante tocar, mas também controlar com precisão o ritmo da música, ou seja, a frequência e a duração de cada nota da música são as duas chaves ao desempenho contínuo da música.

(2) Aquisição da Frequência de Notas

Múltiplos sinais de diferentes frequências podem ser obtidos dividindo-se uma certa frequência de referência. Uma vez que a frequência de cada nota é principalmente não inteira e o coeficiente de divisão de frequência não pode ser um decimal, o coeficiente de divisão de frequência obtido pelo computador deve ser arredondado para um número inteiro. Se a frequência de referência for muito baixa, o coeficiente de divisão de frequência é muito pequeno e o erro de arredondamento será grande. Se a frequência de referência for muito alta, embora o erro relativo da frequência possa ser reduzido, a estrutura de divisão de frequência ficará maior. Na verdade, esses dois fatores devem ser considerados de forma abrangente e uma frequência de referência apropriada deve ser selecionada com a premissa de minimizar o erro. Selecione a frequência de referência de 1MHz neste projeto. O divisor de frequência digital adota um contador binário de 12 bits. Para pausas na música, desde que o coeficiente de divisão de frequência seja definido como 0, ou seja, o valor inicial = 4095, o alto-falante não soará neste momento.

De acordo com o coeficiente de divisão de frequência, o valor inicial obtido pelo divisor de frequência de controle numérico pode ser calculado. (Palavras não podem mais descrever o princípio, e o programa pode explicar este problema. Para a explicação do valor inicial, consulte o programa fornecido abaixo.) A

fórmula de cálculo do valor inicial é a seguinte: Como o divisor de frequência digital projetado usa 12MHZ como fonte de clock e um sinal de estouro de pulso com uma frequência de 1MHZ é dado por uma divisão de 12 frequências e, em seguida, o sinal de estouro de 1MHZ é contado com um código binário de 12 bits com um número predefinido e uma frequência que muda com o número predefinido é dado. Sinal de pulso. Como o sinal de pulso não tem a capacidade de acionar a campainha, a frequência desse sinal de pulso é dividida por 2 para acionar a campainha, portanto, a relação entre a frequência do sinal de saída final e o número predefinido é a seguinte:

(3) Controle do ritmo da música

A batida mínima da música em geral é 1/4 de batida. Se o tempo de 1 batida for definido como 1 segundo, ele só precisa emitir a duração de 1/4 de batida de 4 Hz ( 0,25 segundos) Para outro tempo ocupado Para uma batida mais longa (deve ser um múltiplo inteiro de 1/4 da batida), você só precisa emitir a nota pelo número correspondente de vezes.

O sinal do relógio de contagem é usado como sinal de controle para a saída da velocidade das notas. Quando o relógio está rápido, a velocidade da batida de saída é rápida e a velocidade de reprodução também é rápida. Quando o relógio está lento, a velocidade da batida de saída é lenta , e a velocidade de reprodução é naturalmente reduzida. É necessário adicionar um programa de duas frequências, portanto, o sinal de clock do contador deve ser 2 vezes de 4Hz, ou seja, 8Hz.

(4) Geração de partitura

Este projeto armazena os dados da nota na partitura no LPM-ROM. Se um som permanecer na lógica por 4 batidas do relógio, ou seja, 1 segundo, a nota será armazenada no LPM- Todos os quatro endereços consecutivos na ROM são armazenados. Quando chega um clock de 4 Hz, um dado de nota é emitido do LPM-ROM de acordo.

(5) Módulo de seleção

O módulo de seleção usará um sinal de controle de 4 dígitos para controlar a seletividade dos dados do módulo de partitura.É relativamente simples de descrever em linguagem vhdl e não será descrito em detalhes aqui.

(6) Decodificador e outros módulos

O decodificador e outros módulos foram feitos em experimentos anteriores, e o princípio é relativamente simples e fácil de entender, então não vou entrar em detalhes aqui.

3. Visão geral do projeto de engenharia

Quando chega um pulso de clock de 4 Hz, o módulo gerador de partitura musical emite dados de nota para o módulo de coeficiente de divisão de frequência, e o módulo de coeficiente de divisão de frequência emite o valor inicial necessário para o coeficiente de divisão de frequência correspondente à nota, e o valor inicial é enviado para o módulo divisor de frequência digital. Quando o pulso do relógio de 12MHz chegar, o divisor de frequência de controle numérico emitirá a frequência correspondente (ou seja, a frequência correspondente à nota) para o alto-falante de acordo com a divisão de frequência coeficiente, e o alto-falante pode emitir a nota correspondente. O som vem. O pulso de relógio contínuo de 8 Hz envia os dados de nota armazenados no gerador de pontuação para o módulo de coeficiente de divisão de frequência um por um e, em seguida, passa pelo módulo de divisão de frequência de controle numérico, e, finalmente, o locutor envia os dados de nota um por um.A voz correspondente vem. A música também tocou suavemente. Ao mesmo tempo, o tubo digital LED exibirá a partitura correspondente junto com a música, e as luzes LED de 3 dígitos piscarão correspondentemente com a frequência de alta, média e baixa. Quando a melodia é tocada uma vez, o gerador de melodia pode começar automaticamente desde o início para tocar em loop. Neste momento, use o interruptor DIP para selecionar a música a ser tocada, e o interruptor DIP dará ao seletor um sinal de seleção para selecione a música correspondente. O módulo de tradução de dados reproduz as músicas correspondentes. Quatro músicas são selecionadas neste projeto e codificadas na forma de código Gray. Apenas um bit do interruptor DIP é alterado a cada vez, o que é mais conveniente para a seleção . (Consulte Download para o restante dos detalhes completos)

2. Diagrama geral do quadro

O projeto é composto por módulos, sendo quatro ROMs para módulos de armazenamento de partituras, conforme mostra a figura.

1. A função do divisor de frequência é dividir o clock de 50MHz fornecido no chip em clocks de 12MHz e 8Hz, que são usados pelo contador e driver de divisão de frequência (divisor de frequência NC) respectivamente.

2. O contador completa a função de contagem e a base 183 (a tabela de crisântemo de música mais longa tem 183 caracteres) adiciona um a cada borda do relógio.

3. Os quatro módulos de música registram as partituras de 4 músicas, respectivamente. Leia os dados no endereço correspondente de acordo com o número contado pelo contador do módulo anterior e passe para o próximo módulo.

4. O seletor completa a função de seleção de músicas.

5. O módulo de tradução de dados traduz os dados do endereço na música rom selecionada pelo seletor nos dados de controle necessários para a divisão de frequência do driver de frequência (divisor de frequência de controle numérico), os dados de 3 luzes LED (alta, média e baixo), e o decodificador os dados necessários.

6. O driver de divisão de frequência também é um divisor de frequência controlado numericamente, que completa a função de divisão de frequência e aciona a campainha.

7. O decodificador exibe os dados de pontuação no tubo digital de LED.

3. Selecione o dispositivo

Veja o download para detalhes

4. Módulos funcionais

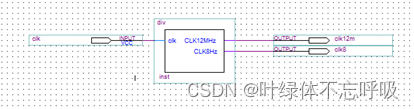

1. O divisor de frequência (div)

divide o clock de 50MHz fornecido no chip em clocks de 12MHz e 8Hz, que são usados pelo contador e driver de divisão de frequência (divisor de frequência NC) respectivamente.

(1) Gráficos do módulo:

(2) O programa é o seguinte:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY div IS

PORT(

clk :IN STD_LOGIC;

CLK12MHz,CLK8Hz: OUT std_logic);

END div;

ARCHITECTURE one of div is

begin

nana:process(clk)

variable cnt:integer range 0 to 2;

variable tmp:std_logic;

begin

if(clk'event and clk='1')then

if cnt>=1 then

cnt:=0;

tmp:=not tmp;

else

cnt:=cnt+1;

end if;

end if;

CLK12MHz<=tmp;

end process nana;

nbnb:process(clk)

variable cnt:integer range 0 to 3125000;

variable tmp:std_logic;

begin

if(clk'event and clk='1')then

if cnt>=3124999 then

cnt:=0;

tmp:=not tmp;

else

cnt:=cnt+1;

end if;

end if;

CLK8Hz<=tmp;

end process nbnb;

end one;

(3) Forma de onda de simulação:

(4) Análise de forma de onda de simulação

Pode ser visto na forma de onda que ckl é um sinal de clock de entrada de 50MHz, ckl12 é um sinal de clock de saída de 12MHz e clk8 é um sinal de clock de 8Hz. papel, todas as formas de onda não são impressas.

Após análise, a função deste módulo está completamente correta.

2. Contador (notetabs)

(consulte o download para obter detalhes)

3. Selecione o módulo (escolha)

(consulte o download para obter detalhes)

4. Módulo de tradução de dados (tontaba)

Traduza os dados do endereço na song rom selecionada pelo seletor em dados de controle necessários para a divisão de frequência do driver de frequência (divisor de frequência de controle numérico), os dados de 3 luzes de LED (agudos, médios e graves) e os dados exigidos pelo decodificador.

(1) Imagem do módulo:

(2) O programa é o seguinte:

library ieee;

use ieee.std_logic_1164.all;

entity tonetaba is

port(index:in std_logic_vector (4 downto 0);

code:out std_logic_vector(3 downto 0);

high0:out std_logic_vector(2 downto 0);

tone:out std_logic_vector(11 downto 0))

;

end;

architecture one of tonetaba is

begin

search:process(index)

begin

case index is

when"00000"=>tone<="111111111111";code<="0000";high0<="000";--0/4095

when"00001"=>tone<="011100011111";code<="0001";high0<="001";--L1/1823

when"00010"=>tone<="100000001111";code<="0010";high0<="001";--L2/2063

when"00011"=>tone<="100011110010";code<="0011";high0<="001";--L3/2291

when"00100"=>tone<="100101010101";code<="0100";high0<="001";--L4/2390

when"00101"=>tone<="101000010000";code<="0101";high0<="001";--L5/2576

when"00110"=>tone<="101010111000";code<="0110";high0<="001";--L6/2745

when"00111"=>tone<="101101001011";code<="0111";high0<="001";--L7/2891

when"01000"=>tone<="101110001111";code<="0001";high0<="010";--M1/2960

when"01001"=>tone<="110000001001";code<="0010";high0<="010";--M2/3082

when"01010"=>tone<="110001111001";code<="0011";high0<="010";--M3/3193

when"01011"=>tone<="110010101100";code<="0100";high0<="010";--M4/3244

when"01100"=>tone<="110100001001";code<="0101";high0<="010";--M5/3337

when"01101"=>tone<="110101011100";code<="0110";high0<="010";--M6/3420

when"01110"=>tone<="110110100101";code<="0111";high0<="010";--M7/3494

when"01111"=>tone<="110111000111";code<="0001";high0<="100";--H1/3528

when"10000"=>tone<="111000000101";code<="0010";high0<="100";--H2/3589

when"10001"=>tone<="111000111100";code<="0011";high0<="100";--H3/3645

when"10010"=>tone<="111001010110";code<="0100";high0<="100";--H4/3670

when"10011"=>tone<="111010000100";code<="0101";high0<="100";--H5/3717

when"10100"=>tone<="111010101101";code<="0110";high0<="100";--H6/3758

when"10101"=>tone<="111011010010";code<="0111";high0<="100";--H7/3795

when others=>null;

end case;

end process;

end;

(3) Forma de onda de simulação:

(4) Análise de forma de onda de simulação

由波形可看出,当输入信号index为00110时high0显示1,code显示6(即 中音6),预置初值为101010111000,查询上文所列的表,可发现功能完全正确。

第二个波形图,输入信号00010,输出为中音2,再查预置初值,同样可发现完全正确。因此该模块功能完全正确。

5. Módulo decodificador (excluído)

(consulte o download para obter detalhes)

6. Módulo divisor de frequência digital (alto-falante)

(consulte o download para obter detalhes)

7. ROM de dados de partitura musical (quatro módulos)

(consulte o download para obter detalhes)

8. Seleção de linhas de endereço:

Além dos módulos mencionados acima, a seleção de linhas de endereço também precisa ser adicionada. Diferentes funções da caixa inferior experimental foram selecionadas. Este experimento usa tubos digitais de LED, portanto, a atribuição de linha de endereço vga é vga0 =0, vga1=1, vga2=0, vga3=0. Como mostrado abaixo:

9. A solução da função de seleção de posição do tubo digital led:

este projeto só precisa exibir um dígito, para que um tubo digital possa ser selecionado. Como o tubo digital na caixa de experimento é um tubo digital de ânodo comum, é apenas necessário selecionar um tubo digital O tubo pode ser atribuído a um nível baixo, conforme mostrado na figura: (selecionei 2, 4, 6 e 8 quatro tubos digitais para exibir juntos)

5. Diagrama de Circuito de Projeto Geral

1. Diagrama esquemático do circuito do projeto de nível superior

2. Os resultados da simulação do projeto de nível superior

Como o sinal de clock de entrada geral do projeto é de 50MHz, que deve passar por vários divisores de frequência e o coeficiente de divisão de frequência é enorme, é impossível ter sucesso na simulação geral (é fará com que o tempo de simulação seja muito longo e falhe). Em relação a esta questão, perguntei especificamente ao Sr. Li Bing. O professor me disse para remover alguns módulos durante a simulação e simular apenas uma parte das funções. Os módulos removidos podem ser simulados separadamente para provar a correção de todo o projeto. I pensei sobre este plano por um longo tempo. Verificou-se que esta simulação pode remover o módulo de divisão de frequência div primeiro e, em seguida, alterar o programa speakera (como a simulação do módulo speakera) para simulação ou remover os módulos div e speakera ao mesmo tempo para simulação. No entanto, esses dois métodos também são divididos em várias partes para simulação, mas não há simulação de todo o projeto; portanto, essa simulação é essencialmente o mesmo que simular separadamente cada módulo para verificar a correção de sua função.

Desde que a função de cada módulo seja completamente correta, pode-se concluir que a função geral do projeto pode ser realizada. A função de cada módulo foi comprovada como completamente correta acima, portanto, a função de todo projeto também está completamente correto. Após a análise, a função de simulação de design de nível superior está completamente correta.

3. O diagrama de atribuição de pinos do arquivo de nível superior do circuito é o seguinte

4. Conectando e baixando

Este programa é implementado no circuito de hardware. O CLK é conectado à entrada do oscilador de cristal de 50MHz; os indicadores de seleção de música são conectados respectivamente a IO9, I010, IO11, IO12 e, em seguida, conectados às luzes LED; Em seguida, conecte ao LED, conecte SPKOUT a IO13 e, em seguida, conecte ao alto-falante.

6. Conclusão

O desempenho da música é amplamente utilizado em dispositivos de atendimento automático, toques de celular, telefones de grupo e equipamentos de instrumentação inteligente. Existem muitos métodos de implementação, entre os quais, hardware puro é usado para completar a performance musical. Com a melhoria da integração FPGA, o preço cai, as ferramentas de design EDA são atualizadas e as funções estão se tornando cada vez mais populares, tornando o aplicativo deste esquema cada vez mais popular. Os projetistas de lógica digital de hoje estão sob pressão para projetar dezenas de milhares de portas com tempo de comercialização cada vez menor, enquanto os projetistas não podem sacrificar a eficiência do silício para manter a singularidade estrutural. Não é uma questão simples usar as ferramentas de software EDA atuais para lidar com esses problemas. O FPGA é pré-carregado com muitos dispositivos LPM de unidade de biblioteca parametrizada construída. Ao introduzir as ferramentas de software EDA[1] que suportam o LPM, os projetistas podem projetar produtos estruturalmente independentes e usar chips de silício com muita eficiência.

O design e a implementação deste circuito de desempenho de hardware de música baseado em FPGA não apenas adota o método de design hierárquico e modular VHDL, mas também adota a ideia de design de divisão de frequência de controle numérico e LPM-ROM personalizado, que otimiza melhor o design do circuito digital de desempenho musical Com base nisso, a música pode ser alterada à vontade sem alterar a estrutura de arquivo de nível superior, o que efetivamente reduz o ciclo de desenvolvimento do produto, reduz o número de chips projetados, reduz o consumo de energia e melhora a flexibilidade, confiabilidade e escalabilidade.