目次

ザイリンクス Zynq-7000 シリーズ FPGA マルチ チャネル ビデオ処理: 画像スケーリング + ビデオ スプライシング表示、エンジニアリング ソース コードとテクニカル サポートを提供

1 はじめに

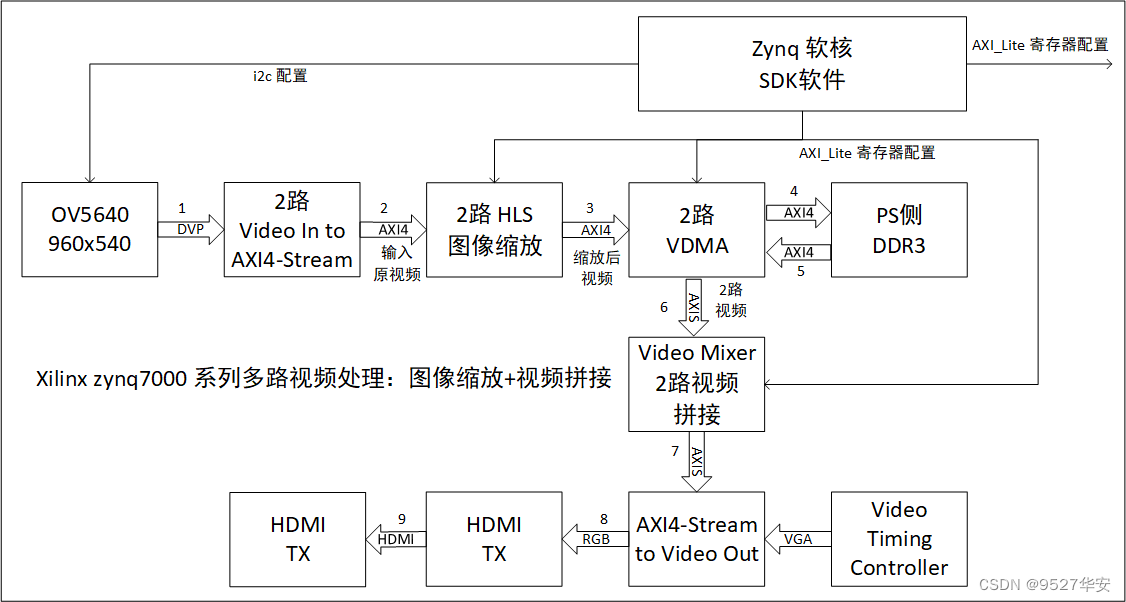

画像のスケーリングやビデオの結合を試したことがなくても、FPGA を使ったことがあると言うのは恥ずかしいことですが、これは CSDN の上司の言葉であり、私はそれを強く信じています。 。 。この記事では、Xilinx Zynq7000 シリーズ FPGA Zynq7020 を使用して、HLS イメージ スケーリング + ビデオ スプライシングを実装します。入力ビデオ ソースは OV5640 カメラ モジュールを使用します。Zynq ソフト コアのオンチップ i2c コントローラーは、OV5640 を 1280x720@30Hz 解像度に設定するために呼び出されます。次に、双方向カスタマイズは、IP キャプチャ OV5640 カメラ ビデオ DVP から RGB888 と呼ばれます。ここでの 2 つの入力は同じ OV5640 からのものです。つまり、1 つは 2 つの入力をシミュレートするために使用されます。次に、2 つのザイリンクス公式ビデオ入力から AXI4-ストリーム IP コアは、RGB ビデオ ストリームを AXI4-Stream ビデオ ストリームに変換するために呼び出されます。2 つのカスタム HLS イメージ スケーリング IP コアを追加して、入力ビデオに対して任意のサイズのイメージ スケーリング操作を実行します。この操作は、Zynq ソフト コア SDK ソフトウェアを通じて設定されます。その本質は、AXI_Lite を通じてレジスタをコンフィギュレーションし、ザイリンクスの公式 VDMA IP を使用してビデオ上で PS 側 DDR3 ビデオ キャッシュ操作を実行し、Zynq を呼び出して VDMA を 2 フレーム フレーム バッファとしてコンフィギュレーションすることです。 AXI_Lite を介してレジスタ コンフィギュレーションを実行し、次に 2 つのザイリンクスの公式ビデオ ミキサー IP を呼び出して 2 つのフレームをバッファリングします。キャッシュされたビデオはビデオ スプライシング操作に使用され、Zynq は 2 つのビデオの異なる表示位置を設定するために呼び出されます。 AXI_Lite を通じてレジスタをコンフィギュレーションし、2 つのザイリンクス公式ビデオ タイミング コントローラー IP と AXI4-Stream to Video Out IP を呼び出して、AXI4-Stream ビデオ ストリームを RGB ビデオ ストリームに変換し、カスタム HDMI 送信 IP を追加します。 RGB ビデオを TMDS 差分ビデオに変換し、表示のためにモニターに送信します。

vivado2019.1 バージョンのエンジニアリング ソース コードとテクニカル サポートのセットを提供します。SDK の構成を通じて、3 つの異なるスケーリングおよびスプライシング ソリューションのセットを作成できます。詳細は次のとおりです。

方案1:输入ov5640,分辨率1280x720;输出分辨率960x1080,在输出屏幕左右两边拼接输出;

方案2:输入ov5640,分辨率1280x720;输出分辨率1920x540,在输出屏幕上下两边拼接输出;

方案3:输入ov5640,分辨率1280x720;输出分辨率960x540,在输出屏幕左上角和右下角两边拼接输出;

ソリューションの詳細な出力デモンストレーションについては、後述の「オンボード デバッグの検証とデモンストレーション」の章を参照してください。3 つのソリューションを切り替えるまたは変更するには、SDK ソフトウェア コードを変更するだけでよく、FPGA ロジックを変更する必要はありません。プロジェクト;

このブログでは、Xilinx Zynq-7000 シリーズ FPGA マルチ チャネル ビデオ処理: 画像スケーリング + ビデオ スプライシング ディスプレイ デザイン スキームについて詳しく説明します。エンジニアリング コードはボード上で包括的にコンパイルおよびデバッグでき、プロジェクトに直接移植できます。学校の学生や大学院生のプロジェクト開発に適しており、現場のエンジニアの学習と向上にも適しており、医療、軍事、その他の産業の高速インターフェースや画像処理分野で使用でき、プロジェクト全体で使用できます。は IP コンフィギュレーション用の Zynq ソフト コアを呼び出し、Zynq コンフィギュレーションは SDK 内の C 言語ソフトウェア コードの形式で実行されるため、プロジェクト全体には FPGA ロジック デザインと SDK ソフトウェア デザインの 2 つの部分が含まれます。埋め込み C 言語であり、初心者や初心者には適していません。

完全な実行可能なエンジニアリング ソース コードとテクニカル サポートを提供します。

エンジニアリング ソース コードとテクニカル サポートの入手方法は記事の最後に記載されています。しばらくお待ちください。終わり;

免責事項

このプロジェクトとそのソース コードには、私が書いた部分と、インターネット上のパブリック チャネル (CSDN、ザイリンクス公式 Web サイト、アルテラ公式 Web サイトなどを含む) から入手した部分の両方が含まれています。気分を害される場合は、プライベート メッセージを送信して批判してください。本プロジェクトおよびそのソースコードは、読者またはファンの個人的な学習・研究に限定しており、商業目的での使用を禁止します 読者またはファン自身による商業利用により法的問題が生じた場合、当ブログとブロガー様とは一切関係がございませんので、ご利用の際はご注意ください。 。 。

2. 関連ソリューションの推奨

FPGA画像処理ソリューション

現在、私のホームページには FPGA 画像処理の列があります。新しい列には、画像のスケーリング、画像認識、画像のスプライシング、画像の融合、画像の曇り除去、画像のオーバーレイなど、現在使用している FPGA 画像処理ソリューションが含まれています。回転、画像強調、画像文字オーバーレイなど。以下は列アドレスです:

クリックして直接移動

FPGA画像スケーリングソリューション

現在、私のホームページには FPGA イメージ スケーリングの列があります。新しい列には、現在所有している FPGA イメージ スケーリング ソリューションが含まれています。実装方法から、HSL に基づいたイメージ スケーリングと純粋な Verilog コードに基づいたイメージがあります。ズーム;アプリケーションの観点からは、シングルチャンネル ビデオ画像のスケーリング、マルチチャンネル ビデオ画像のスケーリング、マルチチャンネル ビデオ画像のスケーリングとスプライシングに分けることができ、入力ビデオの分類からは、OV5640 カメラ ビデオ スケーリングに分けることができます。 SDI ビデオ スケーリング、MIPI ビデオ スケーリングなど。以下は列アドレスです:

クリックして直接移動

推奨される FPGA ビデオ スプライシングおよびオーバーレイ フュージョン ソリューション

私のホームページには現在、FPGA ビデオ スプライシング、オーバーレイ、およびフュージョンに関する列があります。新しい列には、現在私が所有している FPGA ビデオ スプライシング、オーバーレイ、およびフュージョン ソリューションが含まれています。実装方法から、ビデオ スプライシング ベースがあります。 HSL と純粋な Verilog に基づくビデオ スプライシング コードによって実装されたビデオ スプライシング; アプリケーションの観点からは、シングル チャネル、2 チャネル、3 チャネル、4 チャネル、8 チャネル、16 チャネル ビデオに分けることができますスプライシング; ビデオ スケーリング + スプライシング; ビデオ フュージョン オーバーレイ; 入力ビデオ分類から、OV5640 カメラ ビデオ スプライシング、SDI ビデオ スプライシング、CameraLink ビデオ スプライシングなどに分類できます。以下は列アドレスです:< a i=1>クリックして直接移動

3. 設計思想の詳細説明

画像のスケーリングやビデオの結合を試したことがなくても、FPGA を使ったことがあると言うのは恥ずかしいことですが、これは CSDN の上司の言葉であり、私はそれを強く信じています。 。 。この記事では、Xilinx Zynq7000 シリーズ FPGA Zynq7020 を使用して、HLS イメージ スケーリング + ビデオ スプライシングを実装します。入力ビデオ ソースは OV5640 カメラ モジュールを使用します。Zynq ソフト コアのオンチップ i2c コントローラーは、OV5640 を 1280x720@30Hz 解像度に設定するために呼び出されます。次に、双方向カスタマイズは、IP キャプチャ OV5640 カメラ ビデオ DVP から RGB888 と呼ばれます。ここでの 2 つの入力は同じ OV5640 からのものです。つまり、1 つは 2 つの入力をシミュレートするために使用されます。次に、2 つのザイリンクス公式ビデオ入力から AXI4-ストリーム IP コアは、RGB ビデオ ストリームを AXI4-Stream ビデオ ストリームに変換するために呼び出されます。2 つのカスタム HLS イメージ スケーリング IP コアを追加して、入力ビデオに対して任意のサイズのイメージ スケーリング操作を実行します。この操作は、Zynq ソフト コア SDK ソフトウェアを通じて設定されます。その本質は、AXI_Lite を通じてレジスタをコンフィギュレーションし、ザイリンクスの公式 VDMA IP を使用してビデオ上で PS 側 DDR3 ビデオ キャッシュ操作を実行し、Zynq を呼び出して VDMA を 2 フレーム フレーム バッファとしてコンフィギュレーションすることです。 AXI_Lite を介してレジスタ コンフィギュレーションを実行し、次に 2 つのザイリンクスの公式ビデオ ミキサー IP を呼び出して 2 つのフレームをバッファリングします。キャッシュされたビデオはビデオ スプライシング操作に使用され、Zynq は 2 つのビデオの異なる表示位置を設定するために呼び出されます。 AXI_Lite を通じてレジスタをコンフィギュレーションし、2 つのザイリンクス公式ビデオ タイミング コントローラー IP と AXI4-Stream to Video Out IP を呼び出して、AXI4-Stream ビデオ ストリームを RGB ビデオ ストリームに変換し、カスタム HDMI 送信 IP を追加します。 RGB ビデオを TMDS 差分ビデオに変換し、表示のためにモニターに送信します。

vivado2019.1 バージョンのエンジニアリング ソース コードとテクニカル サポートのセットを提供します。SDK の構成を通じて、3 つの異なるスケーリングおよびスプライシング ソリューションのセットを作成できます。詳細は次のとおりです。

方案1:输入ov5640,分辨率1280x720;输出分辨率960x1080,在输出屏幕左右两边拼接输出;

方案2:输入ov5640,分辨率1280x720;输出分辨率1920x540,在输出屏幕上下两边拼接输出;

方案3:输入ov5640,分辨率1280x720;输出分辨率960x540,在输出屏幕左上角和右下角两边拼接输出;

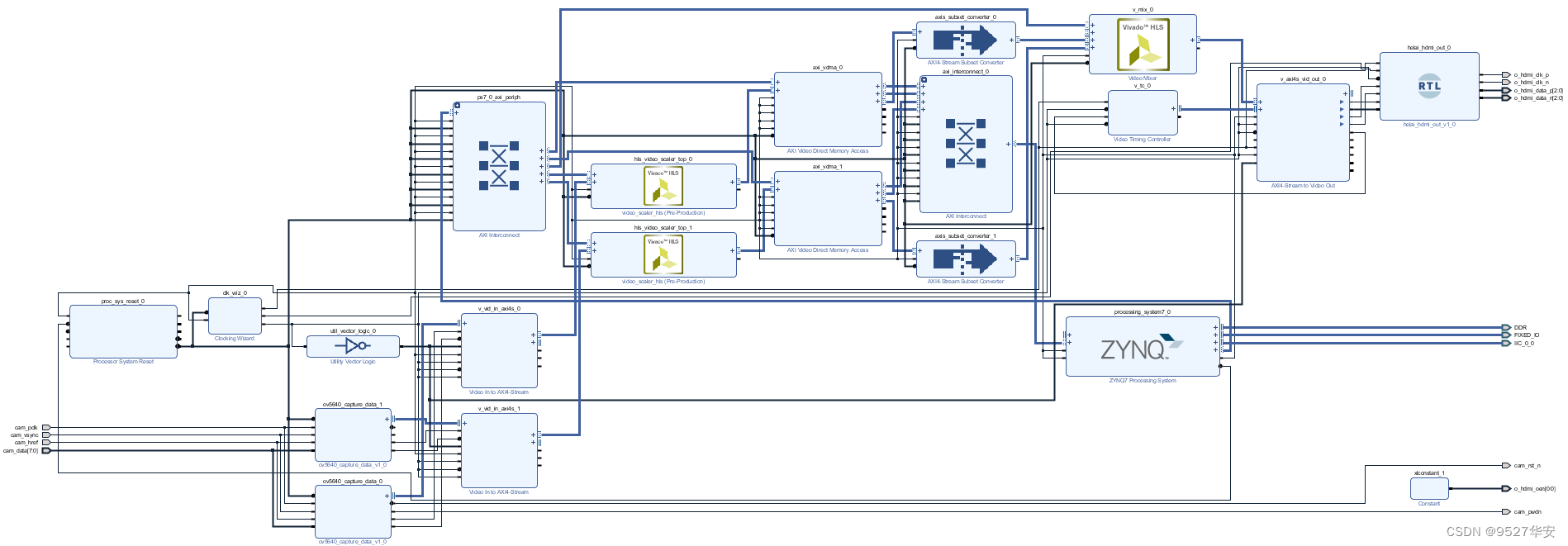

ソリューションの詳細な出力デモンストレーションについては、後述の「オンボード デバッグ、検証、デモンストレーション」の章を参照してください。3 つのソリューションを切り替えるか変更するには、SDK ソフトウェア コードを変更するだけで済みます。 FPGA ロジック プロジェクト、vivado プロジェクトのソース コード設計のブロック図は次のとおりです :

ブロック図の説明: 矢印はデータ フローの方向を表し、矢印内のテキストはデータ形式を表し、矢印の外側の数字は、データ フローの方向のステップを表します。

HLS 画像スケーリングの概要

プロジェクトで使用される IP は一般的に使用される IP であるため、ここでは HLS 画像スケーリング IP に焦点を当てます。

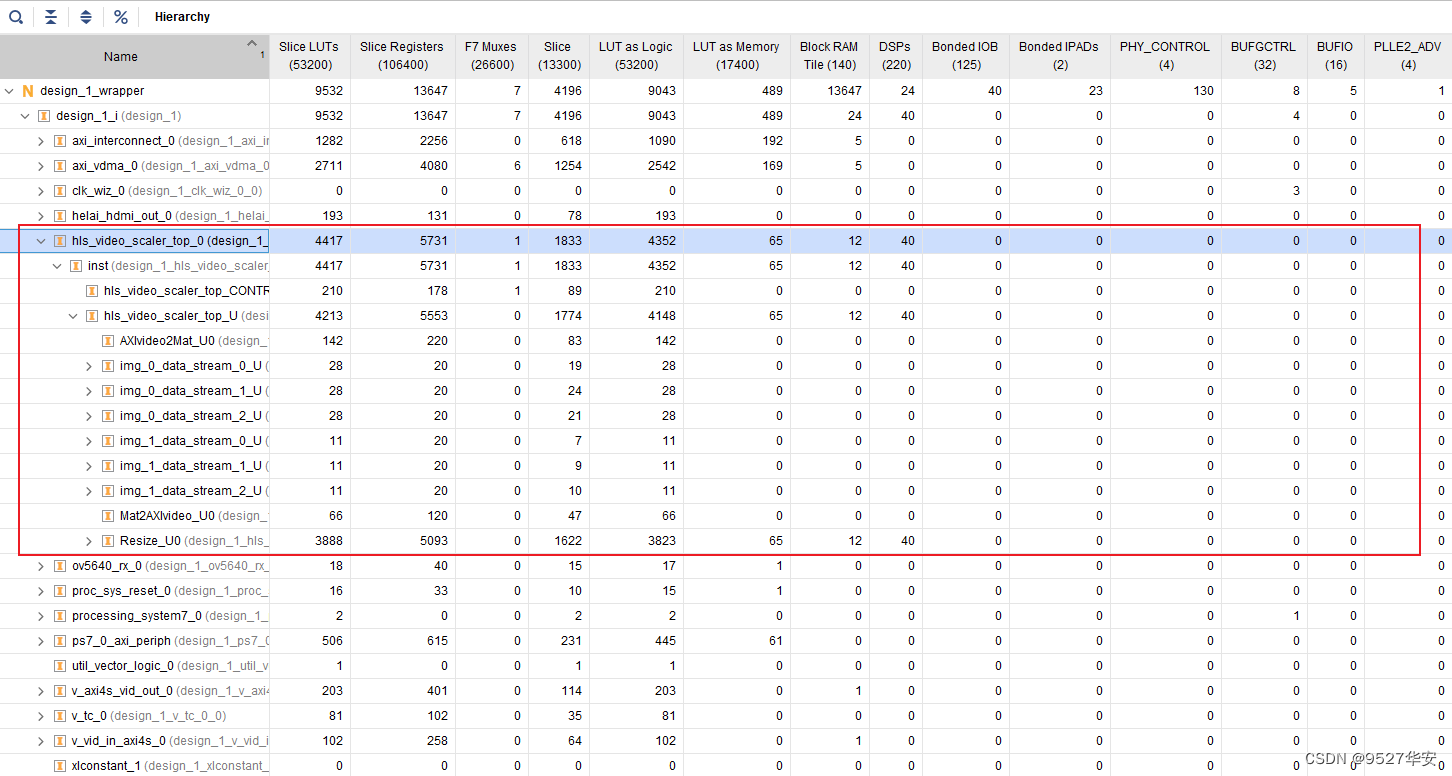

サポートされる最大解像度: 1920x1080@60Hz。ただし、HLS ソース コード解像度を大きくするには、FPGA ロジック リソースが十分に大きくなければならないことが前提となります。

入力ビデオ フォーマット: AXI4-Stream;

出力ビデオフォーマット: AXI4-Stream; < /span> モジュールが占有する FPGA ロジック リソースは次のとおりです。 < /span> FPGA リソースを慎重に評価してください。 自由に変更できる HLS プロジェクト ソース コードを提供します。HLS バージョンは 2019.1 です。 ライブラリ関数を呼び出すことで簡単に使用できる、カスタマイズされた構成 API を提供します。詳細については、SDK コードを参照してください。

には SDK ソフトウェア コンフィギュレーションが必要ですが、これは基本的に AXI_Lite によるレジスタ コンフィギュレーションです。現在はザイリンクス Zynq7000 シリーズ FPGA にのみ適用可能ですが、HLS プロジェクトのデバイス タイプは適応するように変更できます。 Artix7、Kintex7 などの他のデバイスへ;

ビデオ ミキサーの概要

プロジェクトで使用されている IP はすべて一般的に使用されている IP であるため、ここではビデオ ミキサー IP に焦点を当てます。

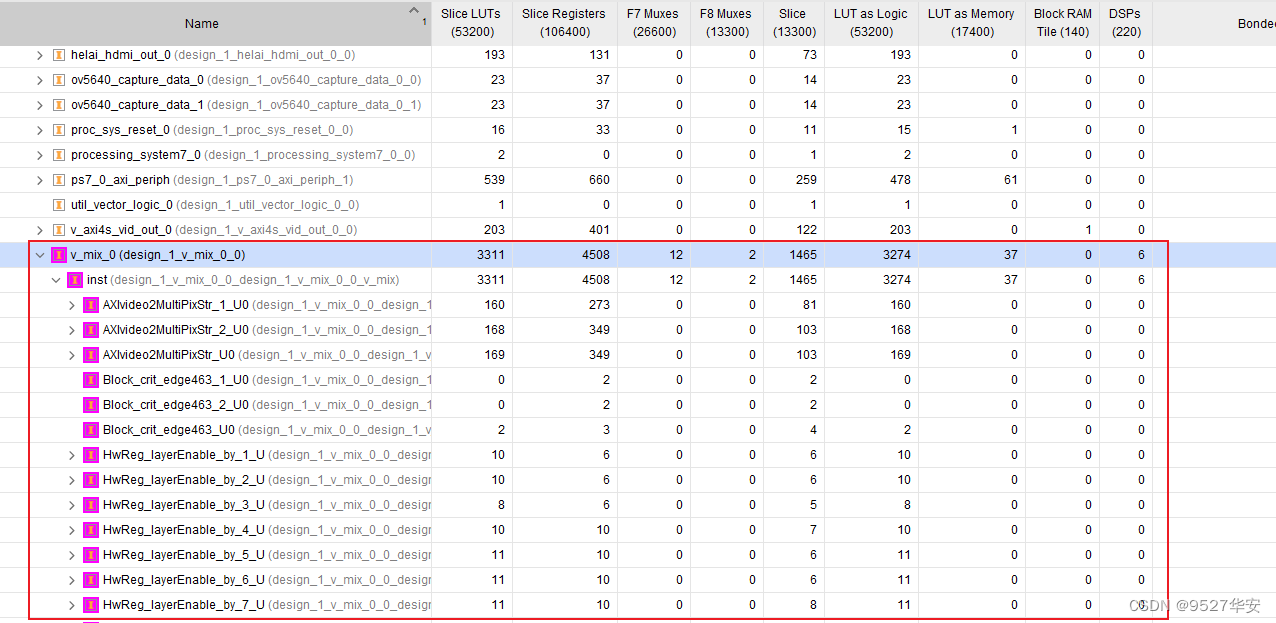

最大解像度 8K をサポートしており、ビデオを最大解像度まで処理できます。 〜 8K; ビデオ ミキサー ロジック リソースは次のとおりです。FPGA リソースを慎重に評価してください。 モジュールが占める FPGA ロジック リソースは小さくなります。HLS ビデオ スプライシングと比較して自分で作成した場合、公式ビデオ ミキサー リソースの占有率は約 30% 小さくなり、より効率的になります。 ライブラリ関数を呼び出すことで、カスタム構成 API が提供されます。詳細については、SDK コードを参照してください。 には SDK ソフトウェア コンフィギュレーションが必要ですが、これは基本的に AXI_Lite によるレジスタ コンフィギュレーションです; 出力ビデオ フォーマット: AXI4-Stream; 入力ビデオ フォーマット: AXI4 -Stream;

最大 16 レイヤーのビデオ スプライシングとオーバーレイをサポートします。つまり、最大 16 チャネルのビデオをスプライスできます。

4. vivado プロジェクトの紹介

PL側FPGAロジック設計

開発ボード FPGA モデル: Xilinx–Zynq7020–xc7z020clg400-2;

開発環境: Vivado2019.1;

入力: OV5640 カメラ、解像度 1280x720p ;

出力: HDMI、1080P 解像度での効果的なスプライシング ビデオ エリア表示;

エンジニアリングの役割: Xilinx Zynq-7000 シリーズ FPGA マルチチャネル ビデオ処理: 画像ズーム +ビデオ スプライシング表示;

プロジェクト BD は次のとおりです:

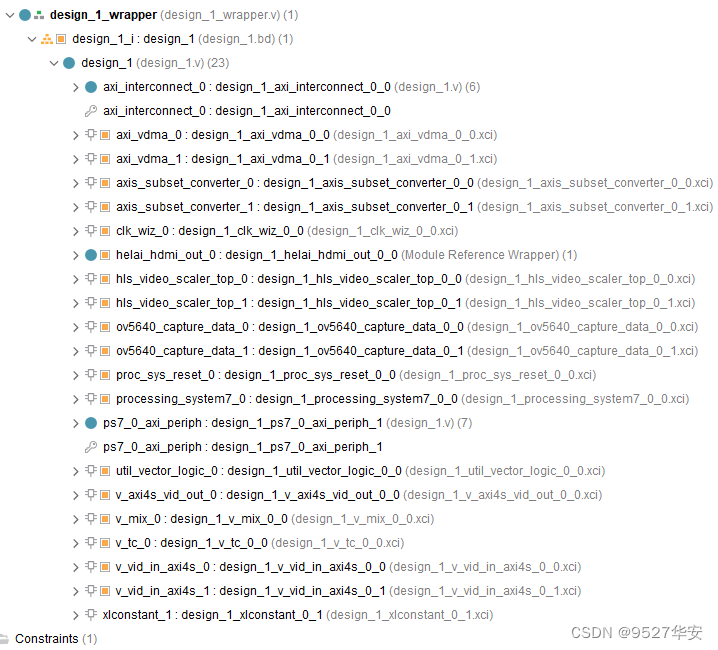

プロジェクト コード構造は次のとおりです:

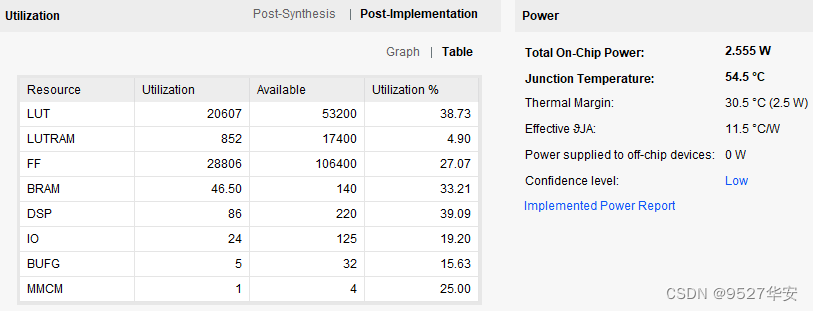

リソースの消費量とプロジェクトの消費電力は次のとおりです。

PS側SDKソフトウェア設計

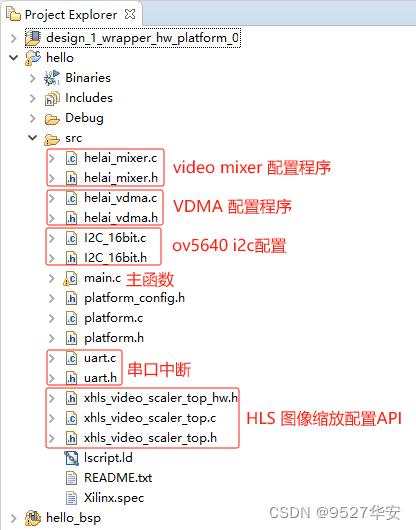

PS 側の SDK ソフトウェア エンジニアリング コード構造は次のとおりです。

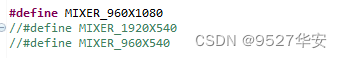

メイン関数は、次の 3 つのマクロ定義を通じて 3 つの異なる画像スケーリングおよびスプライシング ソリューションを設計します。コードは次のとおりです。< /span>

3 つの異なる画像スケーリングおよびスプライシング ソリューションの詳細は次のとおりです。

方案1:输入ov5640,分辨率1280x720;输出分辨率960x1080,在输出屏幕左右两边拼接输出;

方案2:输入ov5640,分辨率1280x720;输出分辨率1920x540,在输出屏幕上下两边拼接输出;

方案3:输入ov5640,分辨率1280x720;输出分辨率960x540,在输出屏幕左上角和右下角两边拼接输出;

前のマクロ定義に従って、main 関数は対応する画像のスケーリング操作を実行し、関連情報を出力します。コードは次のとおりです。

5. プロジェクト移植指示

Vivado バージョンの不一致の処理

1: vivado バージョンがこのプロジェクトの vivado バージョンと一致している場合は、プロジェクトを直接開きます。

2: vivado バージョンがこのプロジェクトの vivado バージョンよりも低い場合プロジェクトの後に、[ファイル] –> [名前を付けて保存] をクリックして開く必要があります。ただし、この方法は安全ではありません。最も安全な方法は、vivado バージョンをこのプロジェクトの vivado バージョンまたはそれ以降のバージョンにアップグレードすることです。

3 : vivado バージョンがこのプロジェクトの vivado バージョンよりも高い場合、解決策は次のとおりです。

プロジェクトを開いた後、IP がロックされていることがわかります。次のように:

現時点では IP をアップグレードする必要があります。次のようにしてください:

FPGAモデルの不一致の処理

使用している FPGA モデルが私のものと一致しない場合は、FPGA モデルを変更する必要があります。操作は次のとおりです:

FPGA モデルを変更した後は、IP もアップグレードする必要があります。 . IP をアップグレードする方法は前に説明しました。 ;

その他の注意事項

1: 各ボードの DDR は必ずしも完全に同じであるとは限らないため、MIG IP は独自の回路図に従って構成する必要があります。ここで元のプロジェクトの MIG を直接削除して、再度追加することもできます。 IP を取得して再構成します。

2: 独自の回路図に従ってピン制約を変更します。xdc ファイル内で変更するだけです。

3: 純粋な FPGA を移植します。 Zynq への追加は、プロジェクトの zynq ソフト コアの追加で実行する必要があります。

6. ボードのデバッグ、検証、デモ

準備

Zynq7000 シリーズ開発ボード;

OV5640 カメラ;

HDMI ディスプレイまたは LCD ディスプレイ。使用した LCD ディスプレイの解像度は 4.3 インチ 800x480 です。

静的プレゼンテーションを出力する

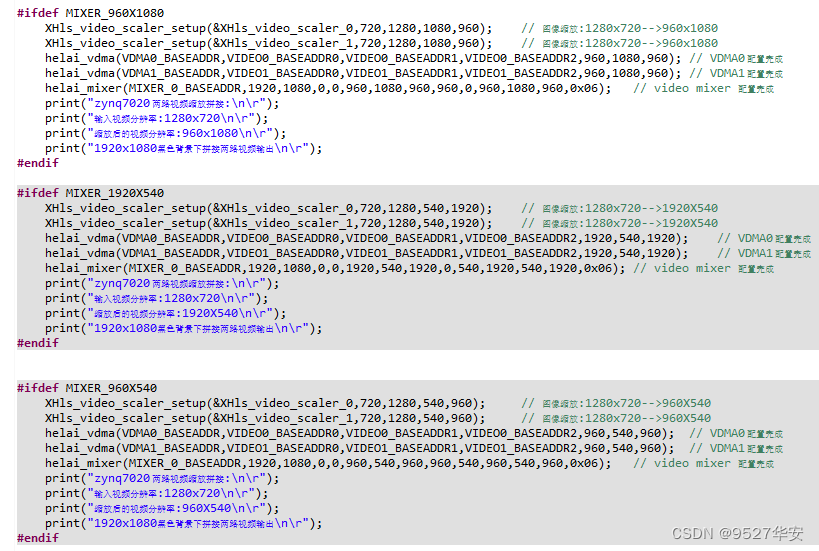

ov5640 入力解像度は 1280x720、HDMI 出力解像度は 960x1080;

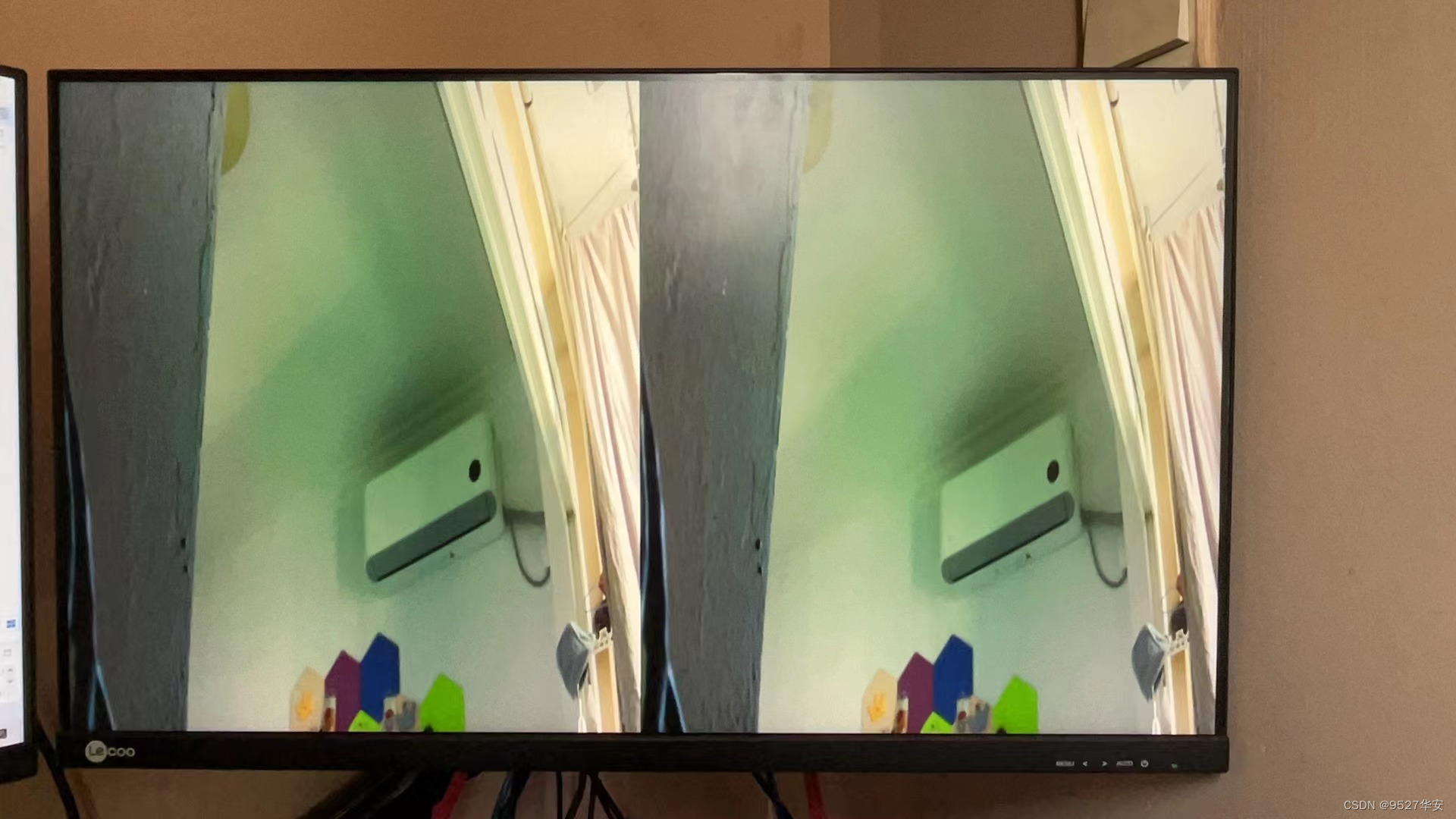

ov5640 入力解像度は 1280x720、HDMI 出力解像度は 1920x540;

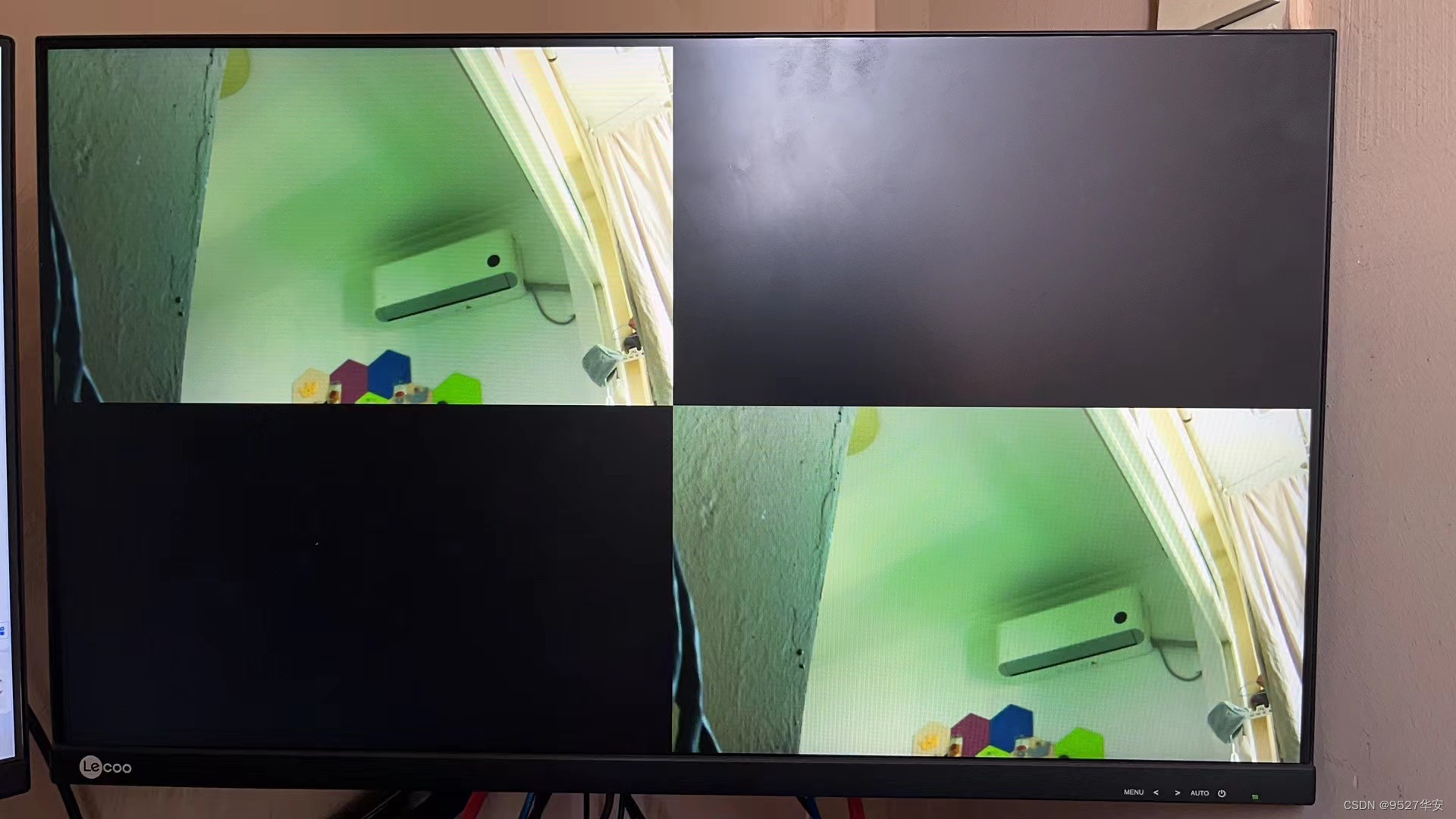

ov5640 入力解像度レート 1280x720、HDMI 出力解像度 960x540;

出力動的デモ

短いビデオが録画され、出力された動的デモンストレーションは次のとおりです。

ズームステッチ

7. メリット: プロジェクトのソースコードを入手

利点: エンジニアリング コードの取得

コードが大きすぎるため、電子メールで送信できません。特定のネットワーク ディスク リンクを介して送信されます。

データの入手方法:非公開、または記事末尾のV名刺。

ネットワーク ディスク情報は次のとおりです。