connaissance du matériel informatique] architecture CPU et jeu d'instructions

https: // blog.csdn.net/antony1776/article/details/83743856

Quatre architectures CPU: ARM, X86, MIPS, PowerPC

ARM faible puissance, LAN, sans fil 3G, les terminaux mobiles, téléphones, dispositif de communication de réseau câblé est largement utilisé,

les MIPS: CISCO grand nombre d'entreprises sont dans les routeurs haut de gamme,

le PowerPC: une large gamme de processeurs de communication de contrôle industriel et applications, Huawei, l'équipement de ZTE,

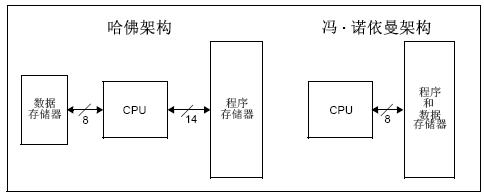

les architectures de processeur central:

Von Neumann: une mémoire d'instructions de programme et des structures de mémoire de données fusionnées; la

structure haversien: stockés séparément;

Jeu d'instructions:

RISC: Avec moins d' instructions, le cycle d'exécution instruction unique, plus grand code objet, ARM, MIPS, PowerPC

CISC: instruction complexe, un long cycle d'instruction, le code multi-objets, le X86,

Les raisons de l'ARM de faible puissance quand il vient à la tête est hors d'usage moins en mesure de X86. En d'autres termes, l'utilisateur lors de l'utilisation de l'ordinateur, son fonctionnement est aléatoire, imprévisible, l'instruction causant ne peut pas prédire. Afin d'améliorer la puissance de traitement de X86 dans ce cas, pour renforcer l'exécution de l'instruction de la commande améliore également la capacité multi-threading d'un seul noyau. L'inconvénient est que pas sous-module processeur très efficace de fermeture et de restauration, car une fois désactivé, la reprise est très lente. Pour maintenir des performances élevées, vous devez faire la plupart du module reste ouvert, et l'horloge reste commutation à grande vitesse. Conséquence directe de la forte consommation d'énergie. L'optimisation d'instructions RISC ARM de résistance afin de déterminer effectué, et compter la place sur un monocytes multifile effectuées à plusieurs noyaux, reste fermée aussi facilement sous-module et les signaux d'horloge, de toute évidence plus de puissance.

Mémoire: ROM (lecture seule), Flash (NOR, NAND), RAM (Random Access Memory)

RAM: RAM statique (SRAM), dynamique la mémoire vive (DRAM),

une mémoire DRAM stocke une charge sous la forme de données stockées dans le condensateur, le condensateur causera la perte de charge due à une fuite, doit périodiquement être rafraîchi,

la SRAM: une longue période d'approvisionnement demeurera valeur;

bus série:

l'USB:

interfaces Ethernet:

Par le MAC (commande d'accès au support Ethernet) et PHY (émetteur-récepteur d'interface physique), respectivement dans la couche de liaison de données et la couche physique;

interagissent la CPU directement avec le MAC, les interfaces matérielles Ethernet sont configurés, unité centrale de traitement> MAC ----> PHY -----> transformateur d' isolement Ethernet ----> RJ45 connecteurs;

analyse schématique:

Conseil de lecture principe figure obtenu diverses ressources matérielles mémoires, périphériques utilisés, y compris la mémoire et la puce périphérique puce de commande de sélection utilisé, les interruptions et les ressources DMA,

schématique matérielle des éléments: le symbole, le réseau, Description,

analyse temporelle du matériel: tâches de débogage carte de circuit, la méthode d'analyse de synchronisation maître aurait plus nécessaire, les

instruments utilisés: multimètres, oscilloscopes,

inscrivez -vous :

Fait partie du processeur central est limité moyens de stockage à grande vitesse capacité de stockage, ils peuvent être utilisés pour stocker temporairement des instructions, des données et l' adresse. 32 CPU

-8086 registres: les registres à usage général, pointeur d'instruction, des registres de drapeau, les registres de segment.

Comment ça marche:

Lorsque les données cpu traitées dans la mémoire, les données tend à entrer dans le premier registre interne, puis effectuer le traitement.

techniques d'exécution de la commande: provoquant le fonctionnement du processeur à pleine capacité et le circuit interne augmentation correspondante de la vitesse de la CPU pour exécuter le programme.

Utilisation: 1, les registres de données internes effectuer arithmétique et logique, 2, stockée dans le registre d'adresse peut être utilisé pour pointer vers un emplacement dans la mémoire, l' adressage, 3) lire et des données d'écriture à l'équipement périphérique.

----------------

Avertissement: Cet article est l'article original blogueurs RPSC "Mexico Zhizuo", et suivre CC BY-SA 4.0 accord du droit d'auteur, reproduit, s'il vous plaît joindre le lien source d' origine et cette déclaration.

Lien original: https: //blog.csdn.net/antony1776/java/article/details/83743856