Zustandsmaschine – Erkennung überlappender Sequenzen

`timescale 1ns/1ns

module sequence_test2(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

//*************code***********//

parameter S0=0, S1=1, S2=2, S3=3, S4=4;

reg [2:0] state, nstate;

always@(posedge clk or negedge rst) begin

if(~rst)

state <= S0;

else

state <= nstate;

end

always@(*) begin

if(~rst)

nstate <= S0;

else

case(state)

S0 : nstate <= data? S1: S0;

S1 : nstate <= data? S1: S2;

S2 : nstate <= data? S3: S0;

S3 : nstate <= data? S4: S2;

S4 : nstate <= data? S1: S2;

default: nstate <= S0;

endcase

end

always@(posedge clk or negedge rst) begin

if(~rst)

flag <= 0;

else

flag <= state==S4;

end

//*************code***********//

endmodule

Zustandsmaschine – nicht überlappende Sequenzerkennung

Erkennen Sie eine Sequenz nur einmal. Das ist die Realität. Sie müssen keine anderen Dinge berücksichtigen. Passen Sie sie einfach an. Machen Sie sich keine Sorgen über Nichtübereinstimmungen.

`timescale 1ns/1ns

module sequence_test1(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

parameter idle=0,s1=1,s2=2,s3=3,s4=4,s5=5;

reg[2:0]cs;

reg[2:0]ns;

always@(posedge clk,negedge rst)begin

if(!rst)begin

cs<=idle;

end

else begin

cs<=ns;

end

end

always@(*)begin

case(cs)

idle:ns=(data==1)?s1:idle;

s1:ns=(data==0)?s2:idle;

s2:ns=(data==1)?s3:idle;

s3:ns=(data==1)?s4:idle;

s4:ns=(data==1)?s5:idle;

default:ns=idle;

endcase

end

always@(posedge clk,negedge rst)begin

if(!rst)begin

flag<=0;

end

else begin

flag<=ns==s5;

end

end

endmoduleNicht überlappende Sequenzerkennung

Zustandsmaschine

Es ist bequemer, eine Zustandsmaschine zu verwenden. Zur Sequenzerkennung wird die Methode entsprechend den Merkmalen ausgewählt. Die einfachste ist der MOORE-Typ. Es hängt davon ab, ob sie langsam ist oder nicht. Ändern Sie CS und NS direkt während der Ausgabebeurteilung. Wenn Sie möchten, dass es langsamer ist, verwenden Sie CS. Wenn nicht, verwenden Sie CS. Nur NS

Die MOORE- und MEALY-Typen von nS weisen die gleiche Synchronisation auf

Wenn keine Überlappung vorliegt, kehrt es direkt in den Ausgangszustand zurück, wenn keine Übereinstimmung vorliegt, und es ist kein Kmp-Abgleich erforderlich.

Schieberegister

Auf Basis des Schieberegisters wird ein CNT-Limit hinzugefügt‘

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

reg[2:0]cnt;

reg[5:0]ram;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)

cnt<=0;

else

cnt<=cnt==5?0:cnt+1;

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)

ram<=0;

else

ram<={ram[4:0],data};

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

match<=0;

not_match<=0;

end

else begin

match<=(cnt==5)&&({ram[4:0],data}==6'b011100);

not_match<=(cnt==5)&&({ram[4:0],data}!=6'b011100);

end

end

endmoduleSequenzerkennung mit Fremdkörpern

Schieberegister

Verwenden Sie zwei Signale, um zu bestimmen, ob die linke und rechte Seite die Anforderungen erfüllen. Wenn beide erfüllt sind, wird 1 ausgegeben

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output match

);

reg[8:0]temp;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

temp<=9'b0;

end

else begin

temp<={temp[7:0],a};

end

end

reg ma;

reg mb;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

ma<='b0;

end

else begin

if(temp[8:6]==3'b011)

ma<=1'b1;

else

ma<=1'b0;

end

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

mb<='b0;

end

else begin

if(temp[2:0]==3'b110)

mb<=1'b1;

else

mb<=1'b0;

end

end

assign match=ma&mb;

endmoduleSequenzerkennung für kontinuierliche Eingabesequenz

Schieberegister

Dieses Schieberegister bestimmt direkt, was im Register gespeichert ist, dh den aktuellen Zustand des Registers, es handelt sich also um eine MOORE-Zustandsmaschine.

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg[7:0]atemp;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

atemp<=8'b0;

end

else

atemp<={atemp[6:0],a};

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

match=1'b0;

end

else begin

if(atemp==8'b0111_0001)

match=1'b1;

else

match='b0;

end

end

endmoduleZustandsmaschine

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

parameter idle=0,s1=1,s2=2,s3=3,s4=4,s5=5,s6=6,s7=7,s8=8;

reg[3:0]cs;

reg[3:0]ns;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)

cs<=idle;

else

cs<=ns;

end

always@(*)begin

case(cs)

idle:begin

ns=(a==0)?s1:idle;

end

s1:begin

ns=(a==1)?s2:s1;

end

s2:begin

ns=(a==1)?s3:s1;

end

s3:begin

ns=(a==1)?s4:s1;

end

s4:begin

ns=(a==0)?s5:idle;

end

s5:begin

ns=(a==0)?s6:s2;

end

s6:begin

ns=(a==0)?s7:s2;

end

s7:begin

ns=(a==1)?s8:s1;

end

s8:begin

ns=(a==1)?s3:s1;

end

default:ns=idle;

endcase

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)

match<=0;

else

match<=(cs==s8)?1:0;

end

endmoduleWas die MOORE-Maschine beurteilt, ist der aktuelle Zustand, also machen Sie eine langsame Aufnahme.

Wenn die MOORE-Maschine den nächsten Zustand bestimmt, wird dieser wie die MEALY-Maschine synchron ausgegeben.

Sequenzerkennung für Diskontinuitäten der Eingabesequenz

Schieberegister (Ausgabe im gleichen Zyklus, Typ MEALY)

Bei der Ausgangsbeurteilung wird es durch den aktuellen Zustand und das Eingangssignal bestimmt.

Es ist zu verschieben, wenn es gültig ist, und dann ist auch zu beachten, dass, da das Signal im gleichen Takt ausgegeben werden soll, da die Verschiebung im nächsten Bit aktualisiert wird, der in diesem Zyklus aktualisierte RAM im nächsten Zyklus ausgeführt wird . Beurteilung, daher kommt es zu einer Verzögerung, daher muss die Ausgabebeurteilung mit dem aktuellen Status, also dem MEALY-Typ, kombiniert werden

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

reg[3:0]ram;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

ram=4'b0;

end

else if(data_valid)begin

ram<={ram[2:0],data};

end

else begin

ram<=ram;

end

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

match<=0;

end

else begin

match<=(ram[2:0]==3'b011)&&data&&data_valid;

end

end

endmoduleZustandsmaschine (Typ MOORE)

Der MOORE-Typ bezieht sich nur auf den aktuellen Status. Daher wird bei der Ausgabe des Urteils ns== verwendet, also der Wert, dem der sekundäre Status entspricht.

Und wenn es MEALY ist, ist es der aktuelle Zustand plus Eingabe

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

parameter idle=0,s0=1,s1=2,s2=3,s3=4;

reg[2:0]cs;

reg[2:0]ns;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

cs<=idle;

end

else begin

cs<=ns;

end

end

always@(*)begin

case(cs)

idle:begin

if(data_valid)

ns=(data==1)?idle:s0;

else

ns=idle;

end

s0:begin

if(data_valid)

ns=(data==1)?s1:s0;

else

ns=s0;

end

s1:begin

if(data_valid)

ns=(data==1)?s2:s0;

else

ns=s1;

end

s2:begin

if(data_valid)

ns=(data==0)?s3:idle;

else

ns=s2;

end

s3:begin

if(data_valid)

ns=(data==0)?s0:idle;

end

endcase

end

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

match<=0;

end

else begin

match<=(ns==s3)?1:0;

end

end

endmoduleZustandsmaschine

Es ist zu beachten, dass die MOORE-Maschine, die den nächsten Zustand bestimmt, weniger als einen Schlag hat und diejenige, die tatsächlich den aktuellen Zustand beurteilt, einen Schlag hat.

Die Moore-Maschine hat einen Zustand mehr als die Mealy-Maschine. Dieser Zustand stellt den Anfangszustand dar.

Der Ausgang der Moore-Maschine wird durch den aktuellen Zustand bestimmt, und der Ausgang der Mealy-Maschine wird durch den aktuellen Zustand und das Eingangssignal bestimmt.

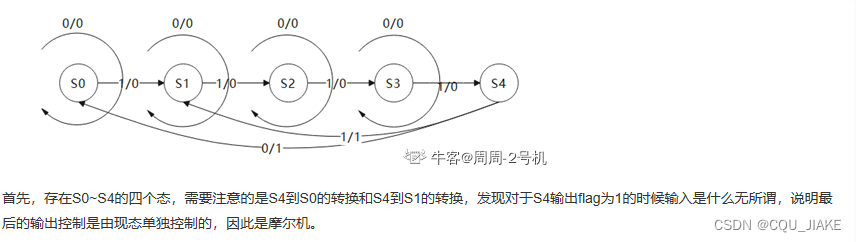

Die endgültige Ausgabesteuerung wird ausschließlich durch den aktuellen Zustand gesteuert, es handelt sich also um eine Moore- Maschine.

Blau stellt den Ausgang dar. Die Moore-Maschine hat schließlich den Zustand S4 hinzugefügt. Aus der Sicht des Zustandsübergangs wird der Ausgangsschlag einen Schlag später sein, aber da es sich um einen kombinatorischen Logikausgang handelt, ist er eigentlich nicht einen Schlag später.

(Dies bedeutet, dass die MOORE-Maschine und die MEALY-Maschine, die den nächsten Zustand beurteilen, die gleiche Ausgabe haben, das heißt, sie geben im gleichen Zyklus aus, und nur die MOORE-Maschine, die den aktuellen Zustand wirklich beurteilt, ist einen Zyklus langsamer.)

Der Unterschied zwischen Moore-Maschine und Miller-Maschine : Der Hauptunterschied besteht darin , ob die Ausgabe der Zustandsmaschine mit dem aktuellen Zustand zusammenhängt . Das Folgende ist ein zweistufiger Ausdruck, um den Unterschied zwischen den beiden zu beschreiben.

Es ist zu beachten, dass bei Verwendung der dreistufigen Beschreibungsmethode der Unterschied zwischen beiden hauptsächlich darin liegt, ob die Beurteilung in der dritten Stufe auf dem aktuellen Zustand oder dem sekundären Zustand basiert.

Die Moore-Zustandsmaschine hat einen Zustand weniger als die Miller-Zustandsmaschine, und die Moore-Zustandsmaschine ist einen Zyklus langsamer; die Miller-Zustandsmaschine verwendet die aktuelle Eingabe und den aktuellen Zustand zur gemeinsamen Beurteilung, während die Moore-Zustandsmaschine keinen Strom benötigt Eingang.

Wenn es sich um eine Moore-Maschine handelt, kann sie in der Ausgabe nur als Sekundärzustand beurteilt werden, das heißt, was der Sekundärzustand ist;

Wenn Sie eine Mahlzeitmaschine wünschen, muss die Ausgabe als Kombination aus dem aktuellen Status und dem Eingangssignal beurteilt werden.

Dies ist eine Mealy-Maschine, da bei der Ausgabe das Ausgangssignal durch den aktuellen Zustand und den Eingang zusammen gesteuert wird.

zweistufig

Die sogenannte zweistufige Formel ist eigentlich eine Schreibweise speziell für die MOORE-Maschine, da die Ausgabe der MOORE-Maschine nur vom aktuellen Zustand abhängt und es dann nur darum geht, den aktuellen Zustand zu beurteilen und dann zu urteilen Was ist der nächste Zustand? Die Ausgabe erfolgt einen Zyklus später und die zweite Stufe. Die Formel besteht darin, den letzten Abschnitt der Ausgabe wegzulassen und ihn in den Zustandsübergang zu integrieren.

Da es sich um eine MOORE-Maschine handelt, wird der Sekundärzustand in der Ausgabe bestimmt. Es ist besser, die Ausgabe direkt im Zustandsübergang zu bestimmen, wenn der Sekundärzustand bestimmt wird.

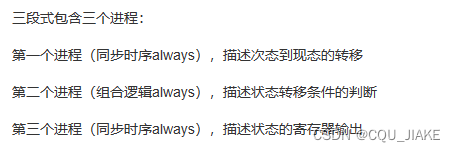

dreistufig

Vom nächsten Zustand zum aktuellen Zustand verwenden Sie posedge,

Verwenden Sie während des Zustandsübergangs immer@(*)

Verwenden Sie beim Exportieren auch posedge

Im ersten und zweiten Prozess wird <= in beiden Prozessen und = im zweiten Prozess verwendet, da sie alle zeitlich synchron sind.

`timescale 1ns/1ns

module fsm1(

input wire clk ,

input wire rst ,

input wire data ,

output reg flag

);

parameter S0 = 'd0, S1 = 'd1, S2 = 'd2, S3 = 'd3 ;

reg [2:0] current_state;

reg [2:0] next_state;

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)begin

current_state <= S0;

end

else begin

current_state <= next_state;

end

end

always@(*)begin

case(current_state)

S0:begin

next_state = data ? S1 : S0;

end

S1:begin

next_state = data ? S2 : S1;

end

S2:begin

next_state = data ? S3 : S2;

end

S3:begin

next_state = data ? S0 : S3;

end

default:begin next_state = S0; end

endcase

end

always@(posedge clk or negedge rst)begin

if(rst == 1'b0)begin

flag <= 1'b0;

end

else begin

if(current_state == S3)begin

if (data) flag <= 1'b1;

else flag <= 1'b0;

end

else begin

flag <= 1'b0;

end

end

end

endmoduleDas ist eine Essensmaschine,