Los recursos como BRAM y LUT de FPGA son limitados. En el proceso de desarrollo de FPGA, a menudo se puede encontrar que los recursos BRAM o LUT no son suficientes.

En general, se recomienda que el consumo de recursos BRAM y LUT no exceda el 80%. Por supuesto, los chips FPGA de gama alta también se pueden reducir al 90%. Si se excede este límite, pueden ocurrir graves violaciones de sincronización, lo que resulta en una placa anormal. operación.

Hoy, compartiré la estrategia de optimización del uso de recursos BRAM, tomando como ejemplo el Block Memory Generator de Vivado.

1. Distribuya BRAM o URAM en lugar de BRAM

La profundidad y el ancho del almacenamiento son pequeños y el recurso LUT o URAM es rico, por lo que en su lugar se puede utilizar "Distribuir BRAM" o "URAM".

Aquí debe prestar atención al modelo de chip FPGA utilizado y si tiene recursos URAM.

-

(*ram_style = "block" *) significa usar Block RAM para implementar

-

(*ram_style = "reg" *) significa usar registros para implementar

-

(*ram_style = "distribuido" *) significa implementación de RAM distribuida

-

(*ram_style = "uram" *) significa usar uram para implementar

Aquí se dan ejemplos de código:

// FPGA 双口 RAM

module dual_port_ram(

input clk,

input [7:0] data_in,

input [5:0] wr_addr,

input wr_en,

input [5:0] rd_addr,

output reg [7:0] data_out

);

// 声明双口 RAM 存储器

(* ram_style = "block" *)reg [7:0] ram[63:0];

// 时钟上升沿写入

always @(posedge clk) begin

if (wr_en)

ram[wr_addr] <= data_in;

end

// 读取;

always @(posedge clk) begin

data_out <= ram[rd_addr];

end

endmodule2. La ROM de doble puerto reemplaza la ROM de un solo puerto

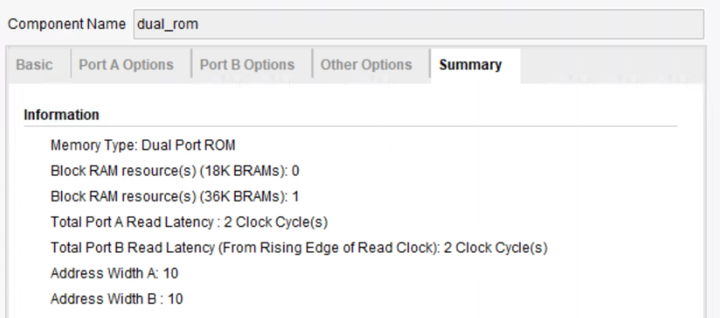

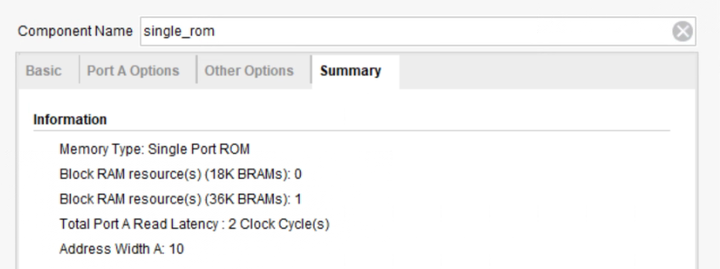

Si hay más de dos ROM o RAM en el proyecto que usan los mismos datos, puede usar el modo de puerto dual en lugar del de puerto único. El consumo de recursos es el mismo, por lo que puede guardar una o más IP de ROM.

Aquí hay una comparación del consumo de recursos en los modos de puerto único y puerto dual de "el ancho de datos es 32, la profundidad de almacenamiento es 1024".

3. Configuraciones razonables de ancho y profundidad de datos

Para optimizar el consumo de recursos FPGA BRAM, es más crítico optimizar el diseño del tamaño de la caché del proyecto FPGA, calcular el ancho de bits y la profundidad máxima de los datos de la caché teórica y seleccionar los parámetros apropiados.

Este artículo se actualizará periódicamente, las palabras clave no son fáciles, haga clic en ⭐️ Me gusta, recopile ⭐️ y escóndalo, no se pierda.

Este artículo fue creado originalmente por FPGA Hurricane, si tienes alguna pregunta, puedes comunicarte conmigo en el área de comentarios.

¡Tu apoyo es mi mayor motivación para seguir creando! Si este artículo es útil para usted, por favor anímelo, gracias.