Un total de 100 preguntas clásicas de exámenes escritos y entrevistas (puedes obtenerlas todas al final del artículo)

1. ¿Cuál es la diferencia entre reinicio sincrónico y reinicio asíncrono en el diseño de circuitos integrados?

Un reinicio sincrónico completa la acción de reinicio cuando cambia el flanco del reloj. Al reinicio asíncrono no le importa el reloj. Siempre que la señal de reinicio cumpla las condiciones, la acción de reinicio se completará. El reinicio asíncrono tiene requisitos relativamente altos para la señal de reinicio y no debe haber fallas. Si la relación entre él y el reloj es incierta, también puede ocurrir un estado metaestable.

2. ¿Cuáles son las características de las máquinas de estados MOORE y MEELEY?

La salida de la máquina de estado de Moore solo está relacionada con el valor del estado actual, y habrá un cambio de estado solo cuando llegue el flanco del reloj. La salida de la máquina de estado de Mealy no solo está relacionada con el valor del estado actual, sino también con el valor de entrada actual.

3. En un diseño de dominios de tiempo múltiples, ¿cómo lidiar con señales que cruzan dominios de tiempo?

Se requiere procesamiento de sincronización para la comunicación de señales entre diferentes dominios de reloj, lo que puede evitar que la señal metaestable del flip-flop de primer nivel en el nuevo dominio de reloj afecte la lógica de nivel inferior.

Sincronización de señales entre dominios de reloj : cuando una sola señal cruza dominios de reloj, se pueden usar flip-flops de dos etapas para sincronizar; cuando los buses de datos o direcciones cruzan dominios de reloj, se pueden usar FIFO asíncronos para lograr la sincronización del reloj; el tercer método es Utilice señales de apretón de manos.

4. ¿Hablar sobre las ventajas y desventajas de la simulación de sincronización estática y dinámica?

El análisis de temporización estática utiliza un método de análisis exhaustivo para extraer todas las rutas de temporización que existen en todo el circuito, calcula el retardo de propagación de las señales en estas rutas y comprueba si los tiempos de configuración y retención de la señal cumplen con los requisitos de temporización. para encontrar errores que violen las restricciones de tiempo.

Puede agotar todas las rutas sin vectores de entrada, corre muy rápido y ocupa menos memoria. No solo puede realizar una verificación integral de la función de sincronización en el diseño del chip, sino que también utiliza los resultados del análisis de sincronización para optimizar el diseño. El análisis de temporización estática se ha utilizado cada vez más en la verificación del diseño de circuitos integrados digitales.

La simulación de temporización dinámica es la simulación habitual porque es imposible generar vectores de prueba completos que cubran todos los caminos en la lista de red a nivel de puerta. Por lo tanto, en el análisis de temporización dinámica, los problemas de temporización que puedan existir en algunas rutas no pueden exponerse.

5. Un Mux de cuatro niveles, en el que la señal de segundo nivel es la señal clave, ¿cómo mejorar la sincronización?

Clave : coloque la señal de segundo nivel en el último nivel de salida y preste atención a modificar la señal de selección del chip para asegurarse de que su prioridad no haya sido modificada. (¿Por qué?)

6. Dado un diagrama a nivel de puerta y el retardo de transmisión de cada puerta, pregunte cuál es la ruta crítica y pregunte la entrada para que la salida dependa de la ruta crítica.

La ruta crítica es la ruta con el mayor retraso de entrada a salida. Una vez que se encuentra la ruta crítica, se puede obtener la frecuencia máxima de reloj.

7. ¿Por qué la relación ancho-largo del tubo P en un inversor estándar es mayor que la del tubo N?

Está relacionado con los portadores, el tubo P es conductor de huecos, el tubo N es conductor de electrones y la movilidad de los electrones es mayor que la de los huecos. Bajo el mismo campo eléctrico, la corriente del tubo N es mayor que el del tubo P, por lo que se debe aumentar la relación ancho-largo del tubo P. , para hacerlo simétrico, de modo que el tiempo de subida y bajada de los dos sean iguales, el margen de ruido de los niveles alto y bajo Los niveles son los mismos y el tiempo de carga y descarga es igual.

8. ¿Usar tubos mos para construir una puerta NAND de dos entradas?

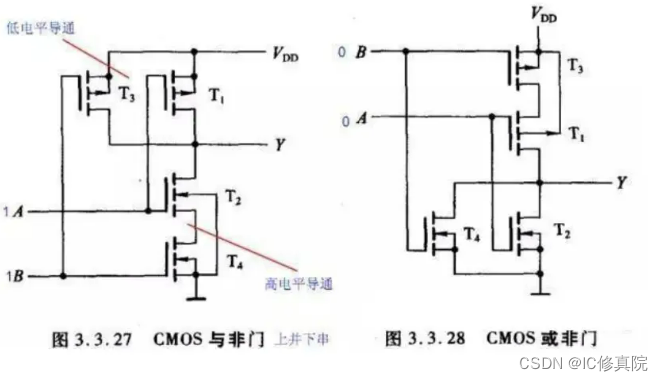

"Fundamentos de tecnología de electrónica digital (quinta edición)" Página 92

Puerta NAND : paralelo superior y serie inferior

Puerta NOR : serie superior y paralelo inferior

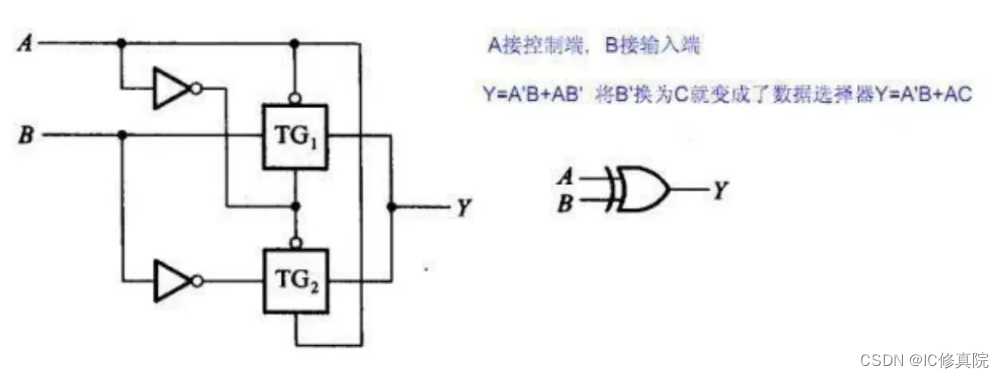

9. Haz un dibujo de CMOS, dibuja el muxgate de remolque a uno.

Y=SA+S'B Utilice puerta NAND e inversor, Y=((SA)'*(S'A)')' después de la conversión, tres puertas NAND y un inversor. Los selectores de datos o puertas XOR también se pueden implementar con puertas de transmisión.

10. ¿Usar un mux de dos opciones y un inv para lograr XOR?

Entre ellos : B está conectado al terminal de entrada de dirección, A y A no están conectados al terminal de selección de datos, F corresponde al terminal de salida y el terminal de habilitación está conectado a tierra de forma fija y puesto a cero (no se muestra). '+

B'A

Usa 1 de 4 para realizar F(x,y,y,z)=xz+yz' F(x,y,y,z)=xyz+xy'z+xyz'+x'yz '=x'y'0 +x'yz'+xy'z+xy1

Y=A'B'D0+A'BD1+AB'D2+ABD3

entonces D0=0, D1=z', D2=z, D3 =1

Los estudiantes que necesiten las preguntas de la entrevista anteriores pueden obtenerlas a pedido. Haga clic en el enlace a continuación para compartirlas con todos ~

Déjame ponerlo aquí: preguntas de la entrevista de IC Pen