Este documento registra los tres métodos de modelado de FPGA y la sintaxis básica de Verilog HDL, y el contenido se actualizará continuamente de acuerdo con el progreso del aprendizaje.

1. Tres métodos de modelado de FPGA

A. Modelado de flujo de datos (asignación)

在数字电路中,信号经过组合逻辑时会类似于数据流动,即信号从输入流向输出,并不会在其中存储。当输入变化时,总会在一定时间以后体现在输出端同样,我们可以模拟数字电路的这一特性,对其进行建模,这种建模方式通常被称为数据流建模1.1 Use la declaración de asignación continua (assign) para describir la función lógica del circuito, lo cual es especialmente conveniente para modelar circuitos lógicos combinacionales

1.2 Impulsado continuamente, la instrucción de asignación continua es impulsada continuamente, es decir, mientras la entrada cambie, la instrucción se recalculará.

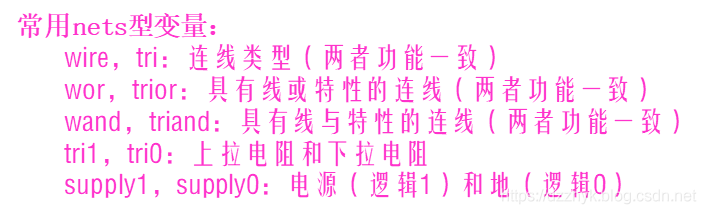

1.3 Solo se pueden asignar variables de tipo red en la declaración de asignación

1.4 Debido a que la variable asignada en la declaración de asignación no almacenará su valor en el emulador, la variable debe ser de tipo Nets, no de tipo registro (reg)

1.5 Las variables del tipo net se pueden controlar varias veces, es decir, la misma red se puede controlar en varias sentencias de asignación<

La diferencia entre los tres métodos de modelado de Day6 FPGA y los conceptos básicos de la gramática Verilog

Supongo que te gusta

Origin blog.csdn.net/qq_43416206/article/details/132255484

Recomendado

Clasificación