El aprendizaje de las máquinas de estado es una gran dificultad para los estudiantes que estudian matemáticas, electrónica y Verilog. Hay un conjunto de plantillas fijas para el aprendizaje automático de estados.En este blog, explicaré brevemente cómo comenzar rápidamente con la programación de máquinas de estados. (Todo el contenido depende de Quarts. Si hay alguna incompatibilidad, se modificará adecuadamente y la idea seguirá siendo la misma).

1. Dibujar un diagrama de estado.

La ventaja de la programación de máquinas de estado es que solo se necesita el diagrama de estado para completar los requisitos del tema. Por lo tanto, el primer paso es, sin duda, dibujar el diagrama de estado del programa.

Dibujar el diagrama de estado a través del diagrama del circuito se divide en 4 pasos: 1. Juzgar el tipo de salida, 2. Escribir la ecuación de excitación, la ecuación de transición de estado y la ecuación de salida, 3. Dibujar la tabla de estado, 4. Dibujar el diagrama de estado. El contenido anterior tiene tutoriales claros y detallados en el tutorial digital, csdn e Internet. No los repetiré uno por uno en este blog.

Si no es un diagrama de estado, sino un caso específico, también puede dibujar un diagrama de estado de clase para lograr el propósito de reemplazar rápidamente el código para realizar la programación de la máquina de estado, lo que muestra la importancia del diagrama de estado.

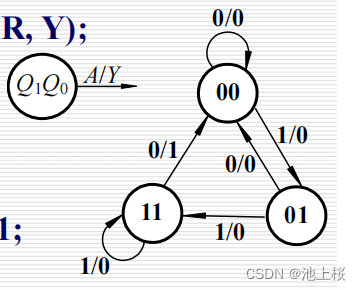

El contenido del diagrama de estado es aproximadamente el siguiente:

(Esta imagen no tiene una relación específica con el código de abajo).

2. Aplicar la plantilla de código.

module Temp1(clk,A,Z);

input clk,A; //时钟和输入

output reg Z; //输出

parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11; //四个状态

//状态机第一段///(用于根据输入进入下一个状态)

reg [1:0] current_state, next_state; //根据需要可更改位数

always@(posedge clk) //时钟上升沿行动

begin

current_state <= next_state; //进入下一个状态

end

/状态机第二段///(用于根据输入和目前状态获得输出和下一个状态)

always@(current_state,A)

begin

case(current_state) //case语句进行寻找现状态的具体值

S0:

begin

Z<=0; //穆尔型不受输入影响,放在if外

if(A==1)

begin //如果为米利型则把Z放在if内,根据状态图赋值

next_state<=S1; //根据状态图可修改

end

else

begin

next_state<=S0; //根据状态图可修改

end

end

S1: //以下内容修改方式同上

begin

Z<=1;

if(A==1)

begin

next_state<=S3;

end

else

begin

next_state<=S0;

end

end

S2:

begin

Z<=0;

if(A==1)

begin

next_state<=S3;

end

else

begin

next_state<=S0;

end

end

S3:

begin

Z<=0;

if(A==1)

begin

next_state<=S2;

end

else

begin

next_state<=S0;

end

end

endcase

end

endmodule

La explicación del código se ha colocado en los comentarios, por lo que no lo repetiré aquí.

Teniendo en cuenta una solución rápida, este módulo de código no utiliza el reinicio. Si necesita usar el reinicio, puede consultar el contenido de otros bloggers en Internet y csdn. Solo practícalo.

De acuerdo con el diagrama de estado, parte del contenido del código se puede reemplazar directamente.

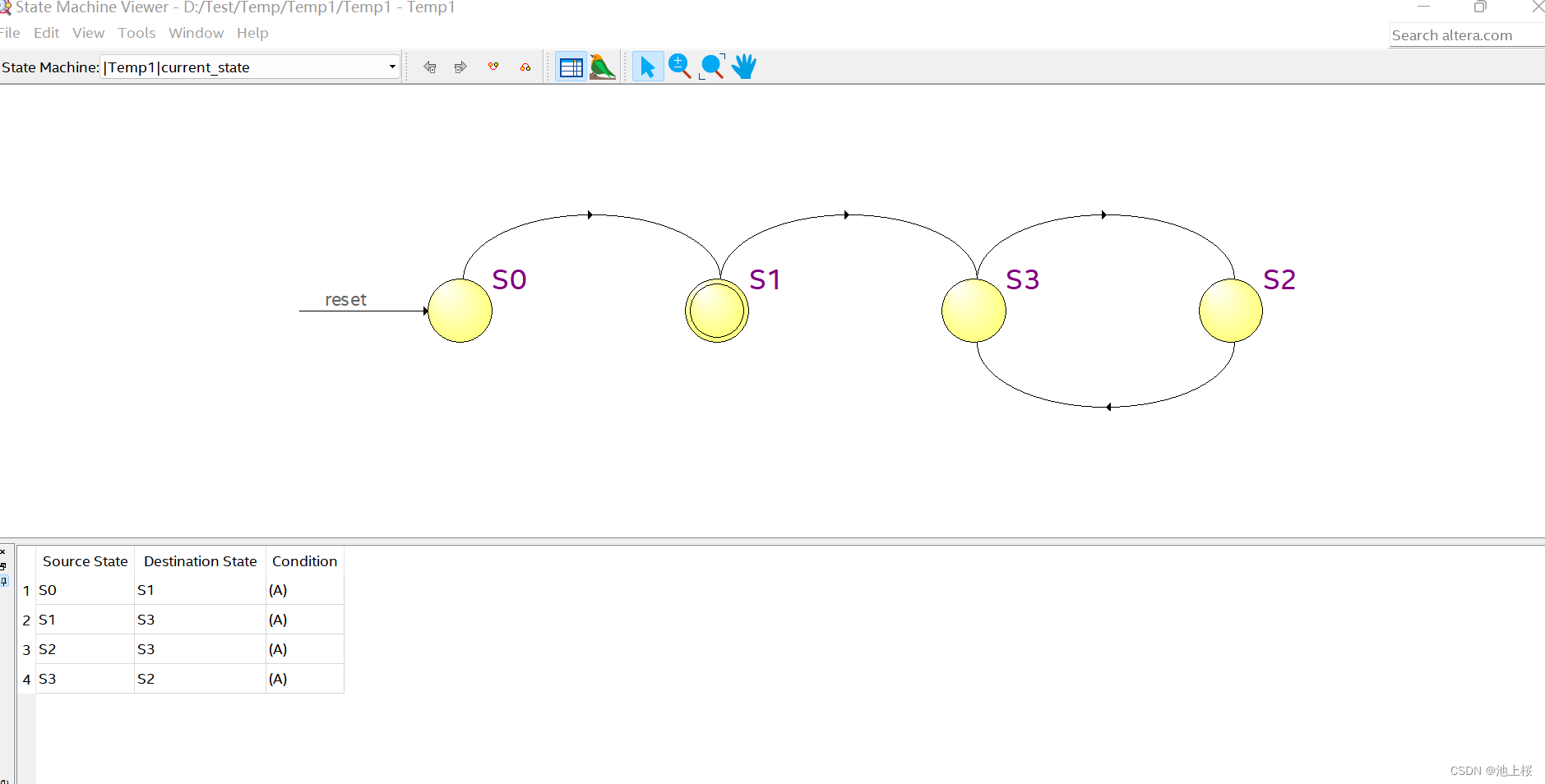

3. Verifique con una máquina de estado.

Haga clic en la barra Herramientas en Quarts, seleccione Netlist Viewers y seleccione los visores de máquinas de estado en la parte inferior para abrir la barra de máquinas de estado.

El contenido general es el anterior, puede verificar si el contenido es incorrecto a través de la máquina de estado.

4. Resumen.

La programación del lenguaje de descripción de hardware de la máquina de estado tiene un conjunto de plantillas universales simples, y es extremadamente fácil comenzar después de aprender.

Llevar adelante el espíritu del código abierto, comenzando desde el primer año ~