wx Gong Zhonghao: Diálogo del diario de Chuangxiang

Enviar: Circuito de música

Obtenga el informe completo en papel sin marca de agua (incluido el diagrama del circuito) de forma gratuita

Directorio de artículos

1. Requisitos de la tarea de diseño

1. Tema de diseño del curso

Diseñe un circuito de interpretación musical que pueda reproducir automáticamente la música escrita. Se requiere reproducir la música a través del altavoz en la caja experimental y usar el diodo emisor de luz para mostrar el ritmo de la música.

(Funciones adicionales: este diseño agrega muchas funciones adicionales basadas en la realización de todas las funciones requeridas por el tema. Todas las funciones se aclararán en la "Reseña general del diseño de ingeniería", que se declara por la presente).

2. Análisis de diseño

(1) Principio básico del circuito de reproducción de hardware de música

El principio de sonido del circuito de hardware, el rango de frecuencia del sonido es de decenas a varios miles de Hz, si el programa se puede usar para controlar un pin determinado de la FPGA Chip para emitir una onda rectangular de cierta frecuencia, conectado al altavoz puede emitir el sonido de la frecuencia correspondiente. Cada nota en la música corresponde a una determinada frecuencia, si quieres que la FPGA emita notas diferentes, solo necesitas controlar la frecuencia de la nota correspondiente. La música está compuesta por una serie de notas, por lo tanto, emita la frecuencia correspondiente a estas notas sucesivamente de acuerdo con la partitura de la música, solo puede enviar el tono de cada nota de forma continua en el altavoz. Para reproducir con precisión una pieza musical, no basta con dejar que el altavoz pueda tocar, sino que también se debe controlar con precisión el ritmo de la música, es decir, la frecuencia y la duración de cada nota en la música son las dos claves. a la interpretación continua del factor musical.

(2) Adquisición de la frecuencia de la nota

Se pueden obtener múltiples señales de diferentes frecuencias dividiendo una determinada frecuencia de referencia. Dado que la frecuencia de cada nota es en su mayoría no entera, y el coeficiente de división de frecuencia no puede ser un decimal, el coeficiente de división de frecuencia obtenido por la computadora debe redondearse a un número entero. Si la frecuencia de referencia es demasiado baja, el coeficiente de división de frecuencia es demasiado pequeño y el error de redondeo será grande. Si la frecuencia de referencia es demasiado alta, aunque se puede reducir el error relativo de la frecuencia, la estructura de división de frecuencia será más grande. De hecho, estos dos factores deben considerarse integralmente y debe seleccionarse una frecuencia de referencia adecuada con la premisa de minimizar el error. Seleccione la frecuencia de referencia de 1 MHz en este diseño. El divisor de frecuencia digital adopta un contador binario de 12 bits. Para silencios en la música, siempre que el coeficiente de división de frecuencia se establezca en 0, es decir, el valor inicial = 4095, el altavoz no sonará en este momento.

De acuerdo con el coeficiente de división de frecuencia, se puede calcular el valor inicial obtenido por el divisor de frecuencia de control numérico. (Las palabras ya no pueden describir el principio, y el programa puede explicar este problema. Para obtener una explicación del valor inicial, consulte el programa que se proporciona a continuación). La

fórmula de cálculo del valor inicial es la siguiente: Dado que el divisor de frecuencia digital diseñado Utiliza 12 MHz como fuente de reloj, y una señal de desbordamiento de pulso con una frecuencia de 1 MHz se da mediante una división de 12 frecuencias, y luego la señal de desbordamiento de 1 MHz se cuenta con un código binario de 12 bits con un número preestablecido y una frecuencia que cambia con el número de preselección se da Señal de pulso. Dado que la señal de pulso no tiene la capacidad de activar el zumbador, la frecuencia de esta señal de pulso se divide por 2 para hacer que suene el zumbador, por lo que la relación entre la frecuencia de la señal de salida final y el número preestablecido es la siguiente:

(3) Control del ritmo de la música

El tiempo mínimo de la música general es 1/4 de tiempo. Si el tiempo de 1 tiempo se establece en 1 segundo, solo necesita dar salida a la duración de 1/4 de tiempo de 4 Hz ( 0,25 segundos) Para otro tiempo ocupado Para un tiempo más largo (debe ser un múltiplo entero de 1/4 de tiempo), solo necesita dar salida a la nota el número de veces correspondiente.

La señal del reloj de conteo se utiliza como señal de control para emitir la velocidad de las notas. Cuando el reloj es rápido, la velocidad de salida es rápida y la velocidad de reproducción también es rápida. Cuando el reloj es lento, la velocidad de salida es lenta. , y la velocidad de reproducción se reduce naturalmente.Es necesario agregar un programa de dos frecuencias, por lo que la señal del reloj del contador debe ser 2 veces de 4Hz, es decir, 8Hz.

(4) Generación de partitura musical

Este diseño almacena los datos de la nota en la partitura musical en el LPM-ROM.Si un sonido permanece en la lógica durante 4 tiempos de reloj, es decir, 1 segundo, la nota se almacenará en el LPM-ROM. Se almacenan las cuatro direcciones consecutivas en la ROM. Cuando llega un reloj de 4 Hz, se emiten datos de nota desde el LPM-ROM en consecuencia.

(5) Módulo de selección

El módulo de selección utilizará una señal de control de 4 dígitos para controlar la selectividad de los datos del módulo de partitura musical.Es relativamente simple de describir en lenguaje vhdl y no se describirá en detalle aquí.

(6) Decodificador y otros módulos

El decodificador y otros módulos se han realizado en experimentos anteriores, y el principio es relativamente simple y fácil de entender, por lo que no lo explicaré aquí.

3. Descripción general del diseño de ingeniería

Cuando llega un pulso de reloj de 4 Hz, el módulo generador de partituras musicales envía datos de nota al módulo de coeficiente de división de frecuencia, y el módulo de coeficiente de división de frecuencia genera el valor inicial requerido para el coeficiente de división de frecuencia correspondiente a la nota, y el valor inicial se envía al módulo divisor de frecuencia digital.Cuando llega el pulso de reloj de 12 MHz, el divisor de frecuencia de control numérico emitirá la frecuencia correspondiente (es decir, la frecuencia correspondiente a la nota) al altavoz de acuerdo con la división de frecuencia Coeficiente, y el altavoz puede emitir la nota correspondiente. El sonido viene. El pulso de reloj continuo de 8 Hz envía los datos de la nota almacenados en el generador de puntuación al módulo de coeficiente de división de frecuencia uno por uno, y luego pasa a través del módulo de división de frecuencia de control numérico, y finalmente el hablante envía los datos de las notas uno por uno y llega la voz correspondiente. La canción también se reprodujo sin problemas. Al mismo tiempo, el tubo digital LED mostrará la puntuación correspondiente junto con la música, y las luces LED de 3 dígitos parpadearán en correspondencia con la frecuencia alta, media y baja. Cuando la melodía se reproduce una vez, el generador de melodías puede comenzar automáticamente desde el principio para reproducirse en un bucle. En este momento, use el interruptor DIP para seleccionar la música que se reproducirá, y el interruptor DIP le dará al selector una señal de selección para seleccione la canción correspondiente. El módulo de traducción de datos reproduce las canciones correspondientes. Se seleccionan cuatro piezas de música en este proyecto y se codifican en forma de código Gray. Solo se cambia un bit del interruptor DIP cada vez, lo que es más conveniente para la selección . (Ver Descargar para el resto de los detalles completos)

2. Diagrama de marco general

El proyecto está compuesto por módulos, cuatro de los cuales son ROMs para módulos de almacenamiento de partituras, como se muestra en la figura.

1. La función del divisor de frecuencia es dividir el reloj de 50 MHz provisto en el chip en relojes de 12 MHz y 8 Hz, que son utilizados por el contador y el controlador de división de frecuencia (divisor de frecuencia NC) respectivamente.

2. El contador completa la función de conteo, y la base 183 (la tabla de crisantemo de la canción más larga tiene 183 caracteres) agrega uno a cada borde del reloj.

3. Los cuatro módulos de música graban las partituras de 4 canciones respectivamente. Leer los datos en la dirección correspondiente según el número contado por el contador del módulo anterior y pasarlo al siguiente módulo.

4. El selector completa la función de selección de canciones.

5. El módulo de traducción de datos traduce los datos de la dirección en la rom de la canción seleccionada por el selector en los datos de control requeridos para la división de frecuencia del controlador de frecuencia (divisor de frecuencia de control numérico), los datos de 3 luces LED (alta, media y bajo), y el decodificador los datos requeridos.

6. El controlador de división de frecuencia también es un divisor de frecuencia controlado numéricamente, que completa la función de división de frecuencia y activa el zumbador.

7. El decodificador muestra los datos de puntuación en el tubo digital LED.

3. Seleccione el dispositivo

Ver descarga para más detalles

4. Módulos funcionales

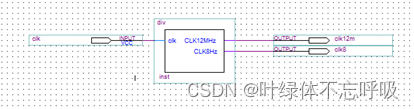

1. El divisor de frecuencia (div)

divide el reloj de 50 MHz provisto en el chip en relojes de 12 MHz y 8 Hz, que son utilizados por el contador y el controlador de división de frecuencia (divisor de frecuencia NC) respectivamente.

(1) Gráficos del módulo:

(2) El programa es el siguiente:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY div IS

PORT(

clk :IN STD_LOGIC;

CLK12MHz,CLK8Hz: OUT std_logic);

END div;

ARCHITECTURE one of div is

begin

nana:process(clk)

variable cnt:integer range 0 to 2;

variable tmp:std_logic;

begin

if(clk'event and clk='1')then

if cnt>=1 then

cnt:=0;

tmp:=not tmp;

else

cnt:=cnt+1;

end if;

end if;

CLK12MHz<=tmp;

end process nana;

nbnb:process(clk)

variable cnt:integer range 0 to 3125000;

variable tmp:std_logic;

begin

if(clk'event and clk='1')then

if cnt>=3124999 then

cnt:=0;

tmp:=not tmp;

else

cnt:=cnt+1;

end if;

end if;

CLK8Hz<=tmp;

end process nbnb;

end one;

(3) Forma de onda de simulación:

(4) Análisis de forma de onda de simulación

Se puede ver en la forma de onda que ckl es una señal de reloj de entrada de 50 MHz, ckl12 es una señal de reloj de salida de 12 MHz y clk8 es una señal de reloj de 8 Hz. Debido a limitaciones papel, no se imprimen todas las formas de onda.

Después del análisis, la función de este módulo es completamente correcta.

2. Contador (notetabs)

(ver descarga para más detalles)

3. Seleccione el módulo (elección)

(ver descarga para más detalles)

4. Módulo de traducción de datos (tontaba)

Traduce los datos de la dirección en la rom de la canción seleccionada por el selector en los datos de control requeridos para la división de frecuencia del controlador de frecuencia (divisor de frecuencia de control numérico), los datos de 3 luces LED (alta, media y baja) y el datos requeridos por el decodificador.

(1) Imagen del módulo:

(2) El programa es el siguiente:

library ieee;

use ieee.std_logic_1164.all;

entity tonetaba is

port(index:in std_logic_vector (4 downto 0);

code:out std_logic_vector(3 downto 0);

high0:out std_logic_vector(2 downto 0);

tone:out std_logic_vector(11 downto 0))

;

end;

architecture one of tonetaba is

begin

search:process(index)

begin

case index is

when"00000"=>tone<="111111111111";code<="0000";high0<="000";--0/4095

when"00001"=>tone<="011100011111";code<="0001";high0<="001";--L1/1823

when"00010"=>tone<="100000001111";code<="0010";high0<="001";--L2/2063

when"00011"=>tone<="100011110010";code<="0011";high0<="001";--L3/2291

when"00100"=>tone<="100101010101";code<="0100";high0<="001";--L4/2390

when"00101"=>tone<="101000010000";code<="0101";high0<="001";--L5/2576

when"00110"=>tone<="101010111000";code<="0110";high0<="001";--L6/2745

when"00111"=>tone<="101101001011";code<="0111";high0<="001";--L7/2891

when"01000"=>tone<="101110001111";code<="0001";high0<="010";--M1/2960

when"01001"=>tone<="110000001001";code<="0010";high0<="010";--M2/3082

when"01010"=>tone<="110001111001";code<="0011";high0<="010";--M3/3193

when"01011"=>tone<="110010101100";code<="0100";high0<="010";--M4/3244

when"01100"=>tone<="110100001001";code<="0101";high0<="010";--M5/3337

when"01101"=>tone<="110101011100";code<="0110";high0<="010";--M6/3420

when"01110"=>tone<="110110100101";code<="0111";high0<="010";--M7/3494

when"01111"=>tone<="110111000111";code<="0001";high0<="100";--H1/3528

when"10000"=>tone<="111000000101";code<="0010";high0<="100";--H2/3589

when"10001"=>tone<="111000111100";code<="0011";high0<="100";--H3/3645

when"10010"=>tone<="111001010110";code<="0100";high0<="100";--H4/3670

when"10011"=>tone<="111010000100";code<="0101";high0<="100";--H5/3717

when"10100"=>tone<="111010101101";code<="0110";high0<="100";--H6/3758

when"10101"=>tone<="111011010010";code<="0111";high0<="100";--H7/3795

when others=>null;

end case;

end process;

end;

(3) Forma de onda de simulación:

(4) Análisis de forma de onda de simulación

由波形可看出,当输入信号index为00110时high0显示1,code显示6(即 中音6),预置初值为101010111000,查询上文所列的表,可发现功能完全正确。

第二个波形图,输入信号00010,输出为中音2,再查预置初值,同样可发现完全正确。因此该模块功能完全正确。

5. Módulo decodificador (eliminado)

(ver descarga para más detalles)

6. Módulo divisor de frecuencia digital (altavoz)

(ver descarga para más detalles)

7. ROM de datos de partituras musicales (cuatro módulos)

(ver descarga para más detalles)

8. Selección de líneas de dirección:

además de los módulos mencionados anteriormente, también se debe agregar la selección de líneas de dirección. Se han seleccionado diferentes funciones del cuadro inferior experimental. Este experimento utiliza tubos digitales LED, por lo que la asignación de línea de dirección vga es vga0 =0, vga1=1, vga2=0, vga3=0. Como se muestra abajo:

9. La solución de la función de selección de posición del tubo digital LED:

este proyecto solo necesita mostrar un dígito, por lo que se puede seleccionar un tubo digital.Dado que el tubo digital en la caja de experimentos es un tubo digital de ánodo común, solo es necesario seleccionar un tubo digital El tubo se puede asignar a un nivel bajo, como se muestra en la figura: (He seleccionado 2, 4, 6 y 8 cuatro tubos digitales para mostrar juntos)

5. Diagrama de circuito de diseño general

1. Diagrama esquemático del circuito del diseño de nivel superior

2. Los resultados de la simulación del diseño de nivel superior

Dado que la señal de reloj de entrada general del proyecto es de 50 MHz, que tiene que pasar a través de múltiples divisores de frecuencia y el coeficiente de división de frecuencia es enorme, es imposible tener éxito en la simulación general (es hará que el tiempo de simulación sea demasiado largo y falle). Con respecto a este problema, le pregunté específicamente al Sr. Li Bing. El maestro me dijo que eliminara algunos módulos durante la simulación y solo simulara una parte de las funciones. Los módulos eliminados se pueden simular por separado para probar la corrección de todo el proyecto. I He pensado en este plan durante mucho tiempo.Se ha descubierto que esta simulación puede eliminar primero el módulo de división de frecuencia div y luego cambiar el programa speakera (como la simulación del módulo speakera) para la simulación, o eliminar los módulos div y speakera al mismo tiempo para la simulación. Sin embargo, estos dos métodos también se dividen en varias partes para la simulación, pero no hay simulación de todo el proyecto, por lo que esta simulación es esencialmente lo mismo que simular cada módulo por separado para verificar la corrección de su función.

Siempre que se demuestre que la función de cada módulo es completamente correcta, se puede concluir que la función general del proyecto se puede realizar.La función de cada módulo se ha demostrado que es completamente correcta anteriormente, por lo que la función de todo proyecto también es completamente correcto. Después del análisis, la función de simulación de diseño de nivel superior es completamente correcta.

3. El diagrama de asignación de pines del archivo de nivel superior del circuito es el siguiente

4. Conexión y descarga

Este programa se implementa en el circuito de hardware. CLK está conectado a la entrada del oscilador de cristal de 50 MHz; los indicadores de selección de música están conectados respectivamente a IO9, I010, IO11, IO12 y luego se conectan a las luces LED; luego conecte al LED, conecte SPKOUT a IO13 y luego conéctelo al altavoz.

6. Conclusión

La interpretación musical se usa ampliamente en dispositivos de respuesta automática, tonos de llamada de teléfonos móviles, teléfonos grupales y equipos de instrumentación inteligente. Hay muchos métodos de implementación, entre los cuales, se utiliza hardware puro para completar la interpretación musical.Con la mejora de la integración de FPGA, el precio baja, las herramientas de diseño de EDA se actualizan y las funciones son cada vez más populares, lo que hace que la aplicación de este esquema cada vez más popular. Los diseñadores de lógica digital de hoy están bajo presión para diseñar decenas de miles de puertas con un tiempo de comercialización cada vez más corto, mientras que a los diseñadores no se les permite sacrificar la eficiencia del silicio para mantener la singularidad estructural. No es una cuestión sencilla utilizar las herramientas de software EDA de hoy en día para hacer frente a estos problemas. FPGA está precargado con muchos dispositivos LPM de unidad de biblioteca parametrizados construidos. Mediante la introducción de herramientas de software EDA[1] compatibles con LPM, los diseñadores pueden diseñar productos que sean estructuralmente independientes y utilicen chips de silicio de manera muy eficiente.

El diseño y la implementación de este circuito de rendimiento de hardware de música basado en FPGA no solo adopta el método de diseño jerárquico y modular VHDL, sino que también adopta la idea de diseño de división de frecuencia de control numérico y LPM-ROM personalizado, que optimiza mejor el diseño del Circuito digital de rendimiento musical Sobre esta base, la música se puede cambiar a voluntad sin cambiar la estructura de archivos de nivel superior, lo que acorta efectivamente el ciclo de desarrollo del producto, reduce la cantidad de chips diseñados, reduce el consumo de energía y mejora la flexibilidad del diseño, la confiabilidad y escalabilidad