1. Resumen de interrupciones

1.1 Mecanismo de respuesta a interrupciones y clasificación

Cuando la CPU está procesando programas normales, a veces se requiere que procese tareas con niveles de demanda más altos, por lo que tiene que interrumpir el proceso de la tarea actual e ingresar a la rutina de servicio de interrupción. Después de procesar estas tareas adicionales, debe volver a la tarea anterior. Por lo tanto, debe guardar la escena antes de ingresar al programa de interrupción para asegurarse de que puede regresar con precisión a la tarea anterior después de que se interrumpa la tarea principal y se complete el programa de interrupción. Nodo de tareas.

Las solicitudes de interrupción se pueden dividir en:

- Interrupción enmascarable: se puede procesar juzgando la prioridad

- Interrupción no enmascarable: detenga a la fuerza el proceso de la CPU e ingrese al programa de interrupción, como reinicio y NMI.

Las fuentes de interrupción también se pueden dividir en dos categorías:

- Fuentes de interrupción internas en el chip: PWM, CAP, QEP, temporizador, etc.

- Chip de fuente de interrupción externa: señales introducidas por los pines de entrada de interrupción externa XINT1 y XINT2

1.2 Estructura de interrupción

F28335 tiene muchos recursos periféricos. Estos recursos periféricos pueden liberar tareas adicionales a la CPU al mismo tiempo. En otras palabras, hay muchas fuentes de interrupción de F28335. Si estas fuentes de interrupción quieren la respuesta de la CPU, deben transmitir señales a través de la línea de interrupción. A la CPU. Sin embargo, el número de líneas de interrupción de F28335 es limitado En este momento, el módulo PIE asigna recursos de interrupción.

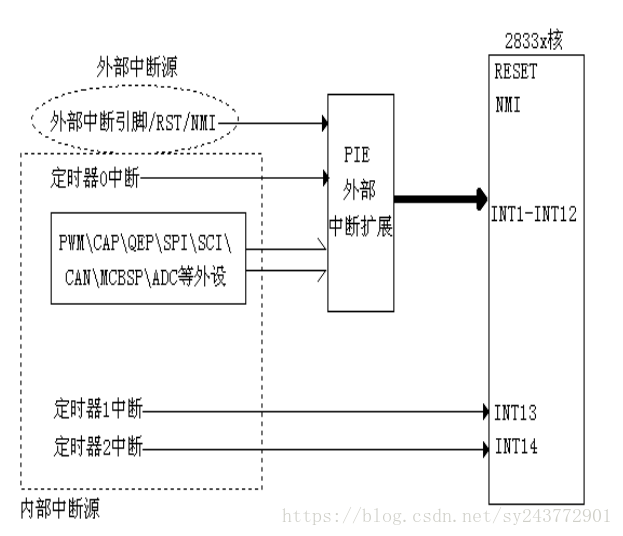

Como puede verse en la figura,

- Las fuentes de interrupciones externas se juzgan y procesan a través del módulo PIE

- Entre las fuentes de interrupción internas, el temporizador 1 y el temporizador 2 se procesan a través de INT13 e INT14 por separado, y otros también se procesan a través del módulo PIE.

- El módulo PIE maneja INT ~ INT12

- Un total de 16 líneas de interrupción

2. Módulo de gestión de interrupciones PIE

La función del módulo PIE es gestionar la activación de múltiples fuentes de interrupción en el caso de líneas de interrupción limitadas.

2.1 Estructura del módulo PIE

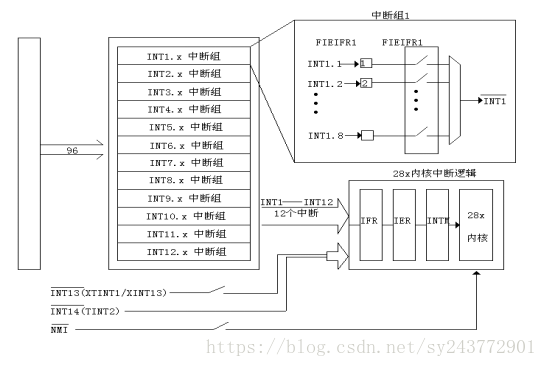

La estructura del PIE se muestra en la figura anterior El módulo PIE está compuesto por múltiples grupos de interrupción y un multiplexor para cada grupo de interrupción. De INT1 a INT12 son interrupciones enmascarables administradas por el módulo PIE, y cada una de estas 12 interrupciones se compone de 8 interrupciones diseñadas externamente Por ejemplo, INT1.X corresponde a INT1.1 ~ INT1.8 en camino. Una interrupción de nivel periférico es nuestro pin de fuente de interrupción externa correspondiente.

El módulo PIE agrupa estas 8 interrupciones periféricas en un grupo a través de un multiplexor de 8 a 1. Cuando configuramos en el programa, también lo configuramos en base a esta estructura.

Complementar la prioridad de la respuesta PIE

- INT1> INT2> ...> INT12

- INT1.1> INT1.2> ...> INT1.8

2.2 Mecanismo de respuesta del módulo PIE

El módulo PIE tiene tantos periféricos para administrar, por lo que debe haber secuencias de respuesta y registros correspondientes que deben configurarse.

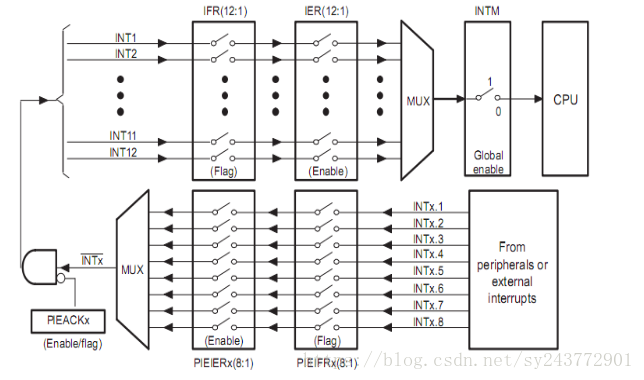

En el módulo PIE, cada grupo de interrupciones tiene una bandera de interrupción correspondiente (PIEIFRx) y un bit de habilitación (PIEIERx.y) Además, cada grupo de interrupciones PIE (INT1 ~ INT12) tiene una bandera de respuesta (PIEACK). La siguiente figura muestra el flujo de operación del hardware PIE con diferentes configuraciones de PIEIFR y PIEIER.

Una vez que el controlador PIE genera una interrupción, se establece el bit de bandera de interrupción correspondiente (PIEIFRx.y). Si el bit de habilitación de interrupción de PIE correspondiente también se establece en 1, el PIE comprobará el PIEACKx correspondiente para determinar si la CPU está lista para responder a la interrupción. Si se borra el bit PIEACKx correspondiente, PIE se aplica a la CPU para una interrupción; si PIEACKx se establece en 1, PIE esperará hasta que se borre el PIEACKx correspondiente antes de solicitar una interrupción a la CPU. PIE controla el bit PIEACKx para controlar que solo se pueda responder una interrupción en cada grupo.Una vez que se da la respuesta, la respuesta PIEACKx debe borrarse a cero para que pueda responder a la interrupción desde la parte posterior del grupo.

Por ejemplo, si desea que la CPU responda a las interrupciones INT1.1.

Solo necesito

- Posición 1 de la bandera PIEIFR1.1

- PIEIFR1.1 habilita bit 1

- Señal de respuesta PIEIFR1.1 bit 1

- Posición de bandera global IFR 1 (solo para INT1 ~ INT12)

- La habilitación de interrupción global IER se establece en 1 (solo para INT1 ~ INT12)

2.3 Tabla de vectores de interrupción

Dado que la dirección correspondiente a cada fuente de interrupción de F28335 se establece de antemano, no podemos cambiarla, por lo que se debe preparar una tabla de vectores de interrupción.

Se puede ver en la figura.

- Cada uno de INT1 ~ INT12 corresponde a 8 interrupciones externas

- Hay 96 recursos receptivos en total y hay muchos recursos ricos

2.4 Ejemplo simple de configuración de interrupciones

La configuración de la interrupción corresponde completamente al mecanismo de respuesta del módulo PIE.

Configure la alarma externa XINT1.

primer paso:

Después de la inicialización básica, especifique el módulo PIE, generalmente en InitPieVectTable (); especifique después de que se inicialice el módulo PIE.

void main(void)

{

InitSysCtrl();

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW;

PieVectTable.XINT1 = &xint1_isr;

EDIS;

}El segundo paso:

Encienda el reloj del módulo PIE Después de consultar la tabla de vectores de interrupciones, sabemos que la interrupción externa XINT1 está habilitada en INT1.4 Encienda esta habilitación de interrupciones.

void main(void)

{

InitSysCtrl();

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW;

PieVectTable.XINT1 = &xint1_isr; //赋予中断地址

EDIS;

IER |= M_INT1; //全局使能INT1

PieCtrlRegs.PIEIER1.bit.INTx4 = 1; //使能INT1.4

EINT;

ERTM;

}En ese momento, me preguntaba a dónde iba la bandera PIEIFR 1. De hecho, se estableció automáticamente en 1 cuando se respondió la interrupción. Solo necesitamos habilitarlo para que pueda pasar sin problemas.

El tercer paso:

escribir la función en nuestra interrupción y borrar el indicador de respuesta de interrupción PIEACK en la interrupción.

interrupt void xint1_isr(void)

{

Xint1Count++;

GpioDataRegs.GPACLEAR.all = 0x4;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

}