The GPIO related configuration register

STM32F407ZGT6 has a total of 7 groups of IO ports, each group of IO ports has 16 IOs, a total of 16X7=112 IOs, plus 2 PH0 and PH1, a total of 114 IO ports.

- A port mode register (GPIOx_MODER)

- A port output type register (GPIOx_OTYPER)

- A port output speed register (GPIOx_OSPEEDR)

- A port pull-up and pull-down register (GPIOx_PUPDR)

- One port input data register (GPIOx_IDR)

- One port output data register (GPIOx_ODR)

- A port set/reset register (GPIOx_BSRR)

- A port configuration latch register (GPIOx_LCKR)

- Two alternate function registers (low GPIOx_AFRL & GPIOx_AFRH)

Each IO port contains the following 10 registers. That is, 10 registers can control 16 IO ports of a group of GPIO in total.

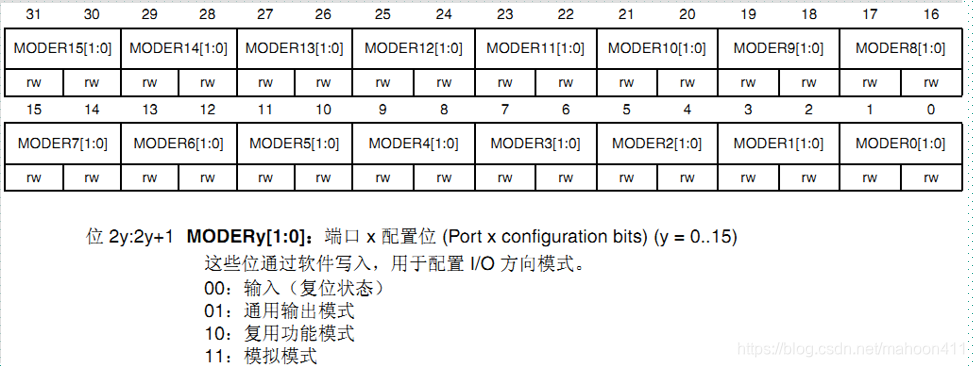

1. Port mode register (GPIOx_MODER)

GPIO port mode register

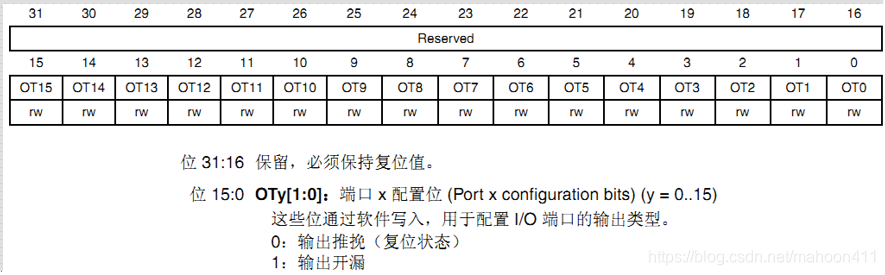

2. Port output type register (GPIOx_OTYPER)

GPIO port output type register

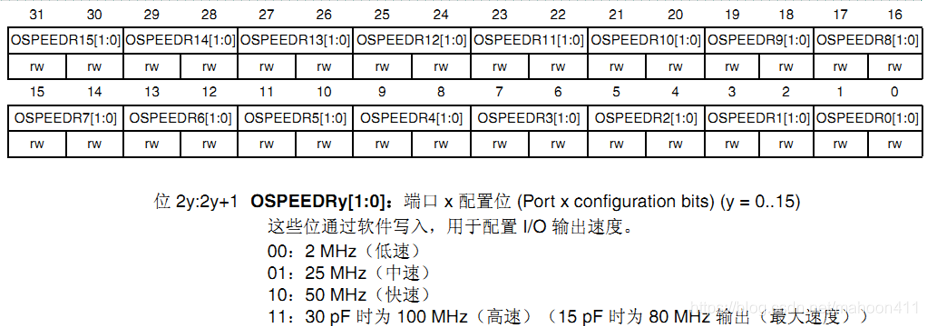

3. Port output speed register (GPIOx_OSPEEDR)

GPIO port output speed register

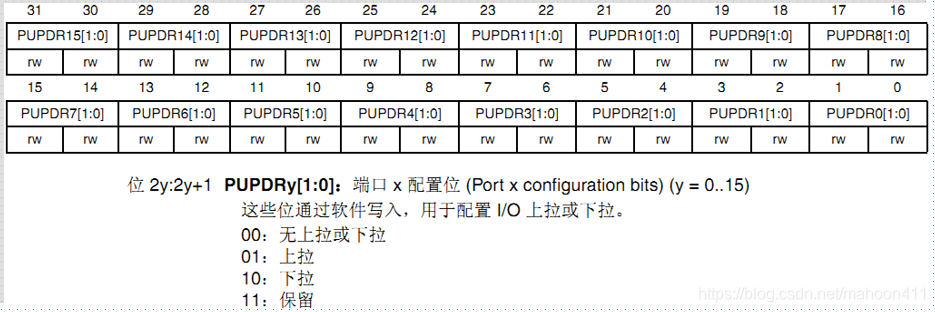

4. Port pull-up and pull-down register (GPIOx_PUPDR)

GPIO port pull-up/pull-down register

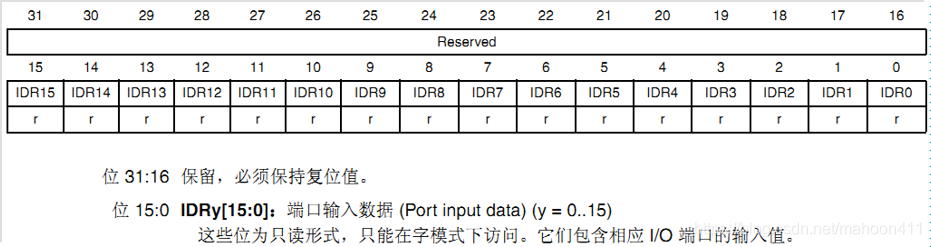

5. Port input data register (GPIOx_IDR)

GPIO port input data register

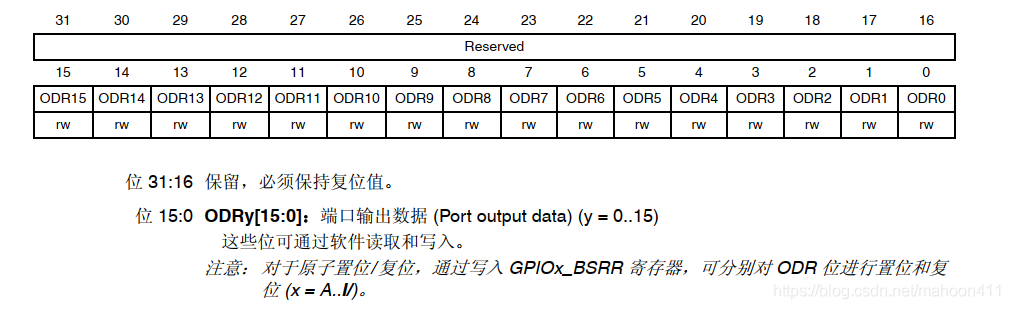

6. Port output data register (GPIOx_ODR)

GPIO port output data register

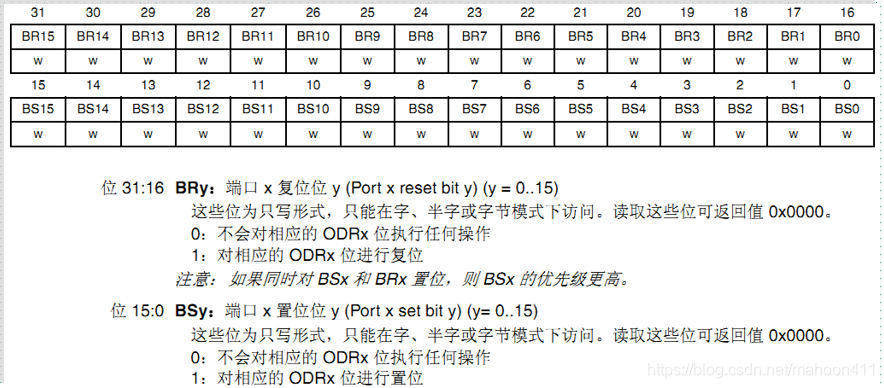

7. Port set/reset register (GPIOx_BSRR)

GPIO port bit set/reset register

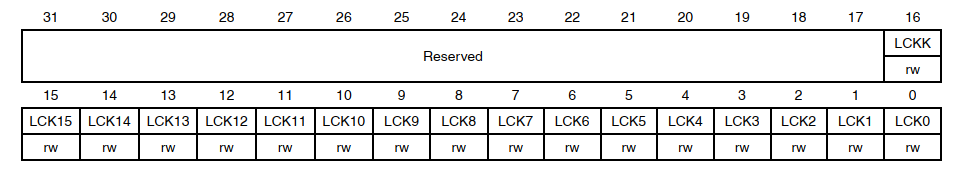

8. Port configuration latch register (GPIOx_LCKR)

GPIO port configuration lock register

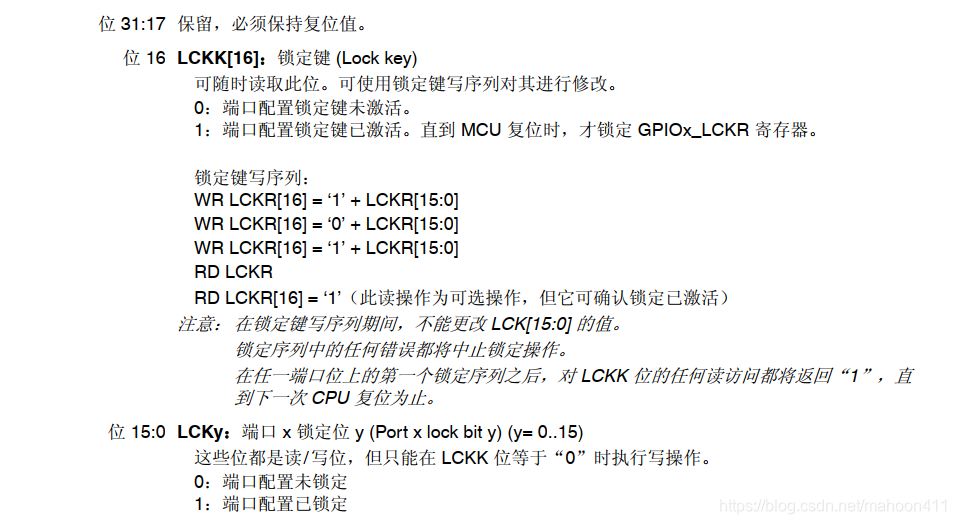

9. GPIO multiplexing function low register (GPIOx_AFRL)

GPIO alternate function low register

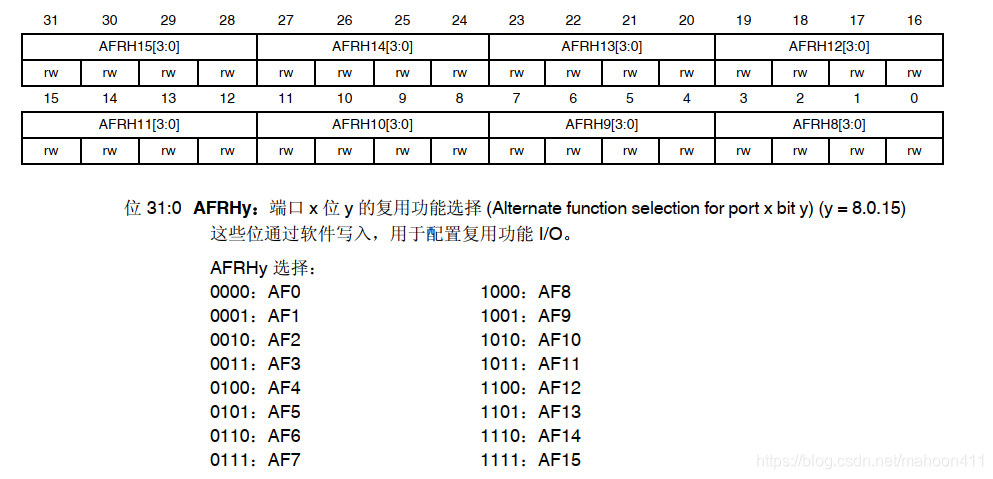

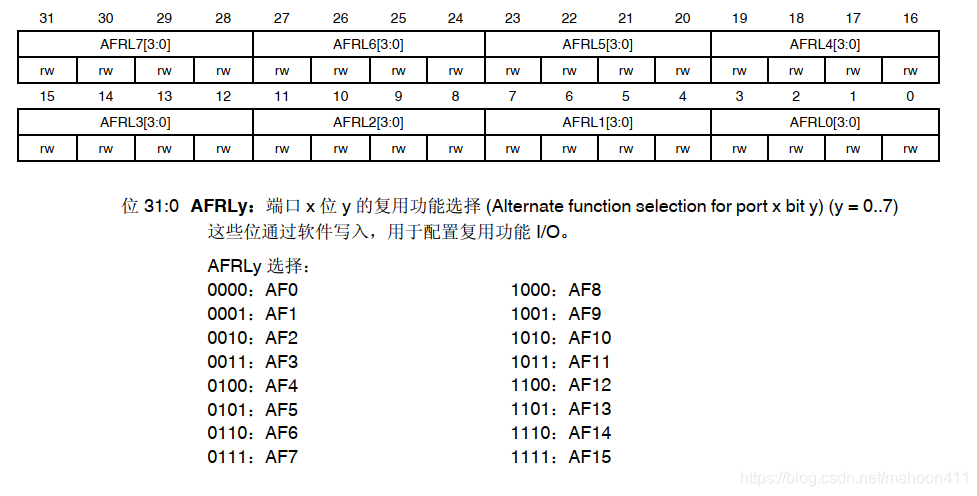

10. GPIO multiplexing function high register (GPIOx_AFRH)

GPIO alternate function high register