S3C2440时钟体系的简单编程

Programming purpose:

Make FCLK=400MHZ

HCLK=100MHZ

PCLK=50MHZ

Steps:

1. Set the MPLLCON register to make FCLK=400MHZ

2. Set the CLKDIVN register so that HCLK=FCLK/4 and PCLK=FCLK/8 to get HCLK=100MHZ, PCLK=

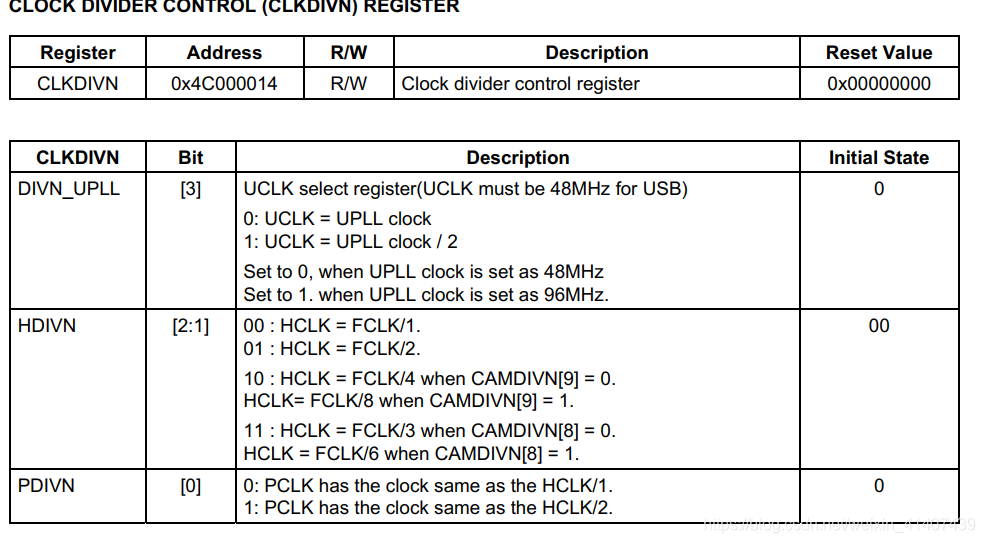

Below 50MHZ is the configuration manual of the register:

you can see that it states that when HDIVN 2:1 is set to 10, HCLK=FCLK/4, but he has a prerequisite that CMDIVN[9]=0; by searching the manual, The default value of CAMDIVN[9] is 0, so we don't need to worry about it here. Looking further down, when the 0 bit of CLKDIVN is 1, PCLK=HCLK/2.

you can see that it states that when HDIVN 2:1 is set to 10, HCLK=FCLK/4, but he has a prerequisite that CMDIVN[9]=0; by searching the manual, The default value of CAMDIVN[9] is 0, so we don't need to worry about it here. Looking further down, when the 0 bit of CLKDIVN is 1, PCLK=HCLK/2.

That is:

CLKDIVN[2:1]=0100

CLKDIVN[0] =0001

CLKDIVN=0101=0X5

Next, let's set the clock of MPLL:

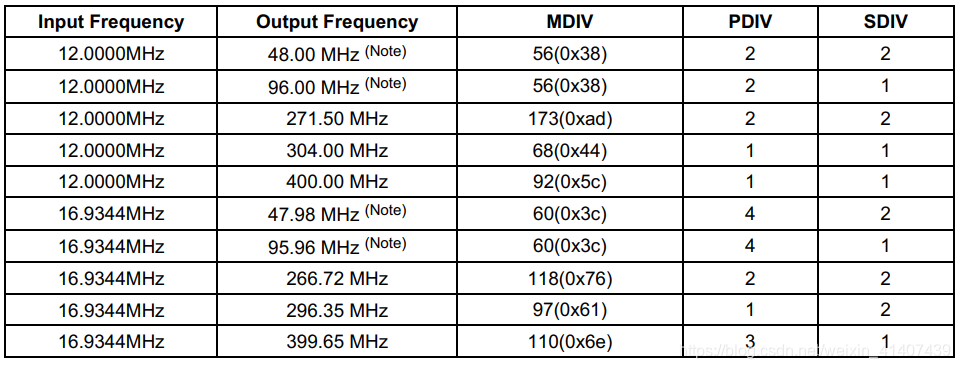

Let's see the manual:

when the crystal oscillator is 12M, if you want to set the speed of 400MHZ, you

when the crystal oscillator is 12M, if you want to set the speed of 400MHZ, you

need to set

MDIV=92

PDIV=1

SDIV=1

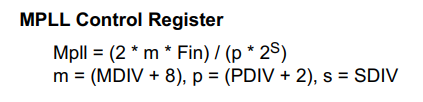

. There is also a calculation formula on the manual:

after conversion, it is :

* MPLL=(2 (MDIV+8) FIN)/((PDIV+2) 2^SDIV)

FIN= crystal oscillator frequency.

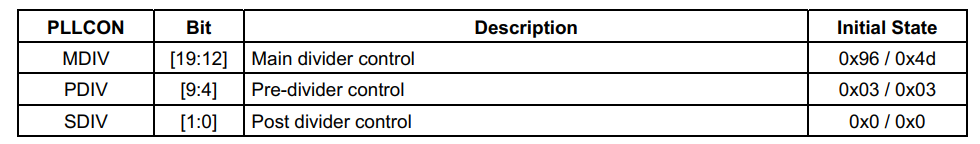

From this we can set the register like this:

**PLLCON=(92<<12)|( 1<<4)|(1<<0)** can achieve our goal:

remember to check the manual for precautions after setting the register.

Now we can start to write the code: the

code is as follows

. text

.global _start

_start:

/* 关闭看门狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

/* LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 设置CPU工作于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 然后CPU工作于新的频率FCLK

*/

/* 设置内存: sp 栈 */

/* 分辨是nor/nand启动

* 写0到0地址, 再读出来

* 如果得到0, 表示0地址上的内容被修改了, 它对应ram, 这就是nand启动

* 否则就是nor启动

*/

mov r1, #0

ldr r0, [r1] /* 读出原来的值备份 */

str r1, [r1] /* 0->[0] */

ldr r2, [r1] /* r2=[0] */

cmp r1, r2 /* r1==r2? 如果相等表示是NAND启动 */

ldr sp, =0x40000000+4096 /* 先假设是nor启动 */

moveq sp, #4096 /* nand启动 */

streq r0, [r1] /* 恢复原来的值 */

bl main

stop:

b stop