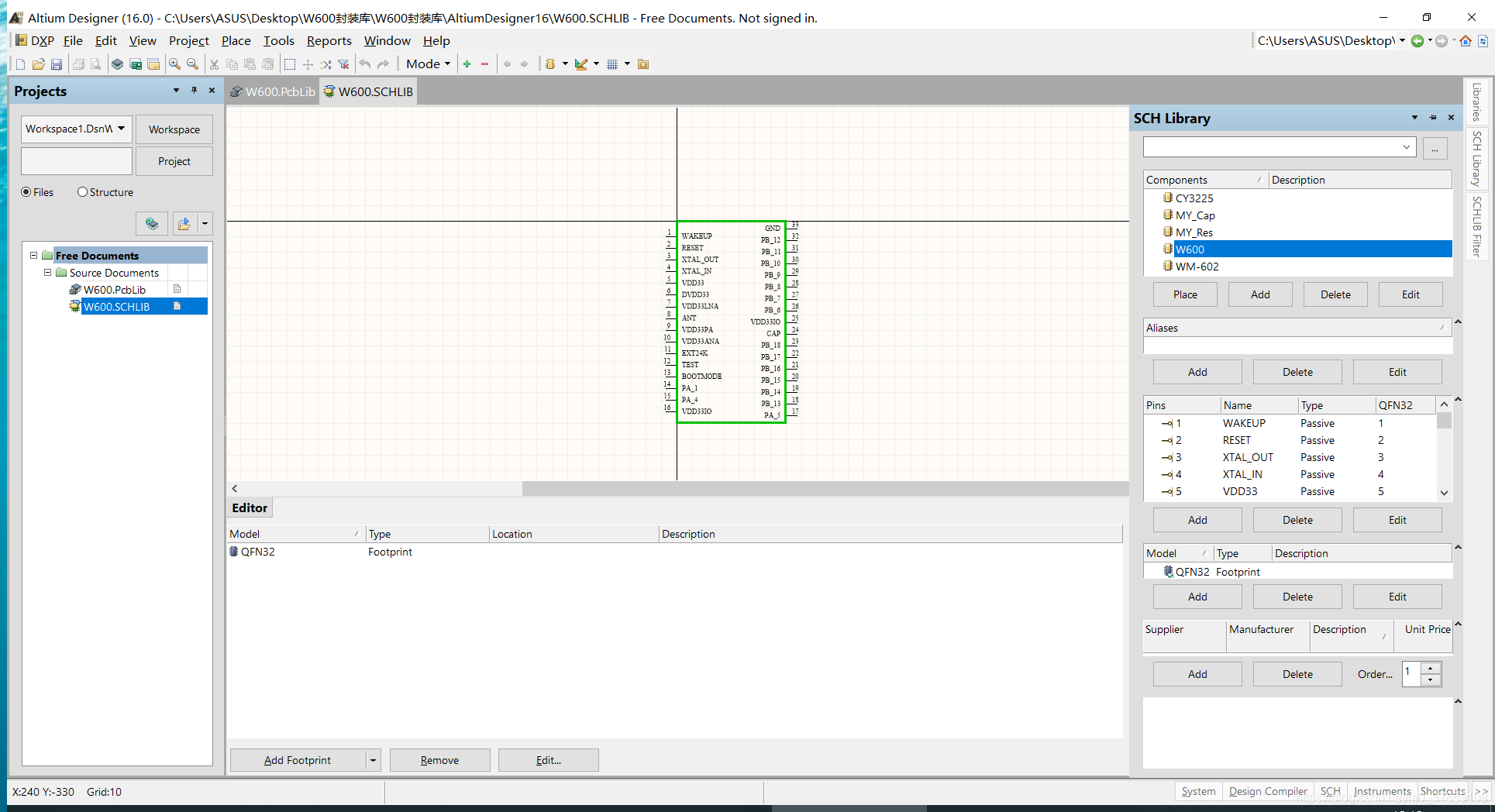

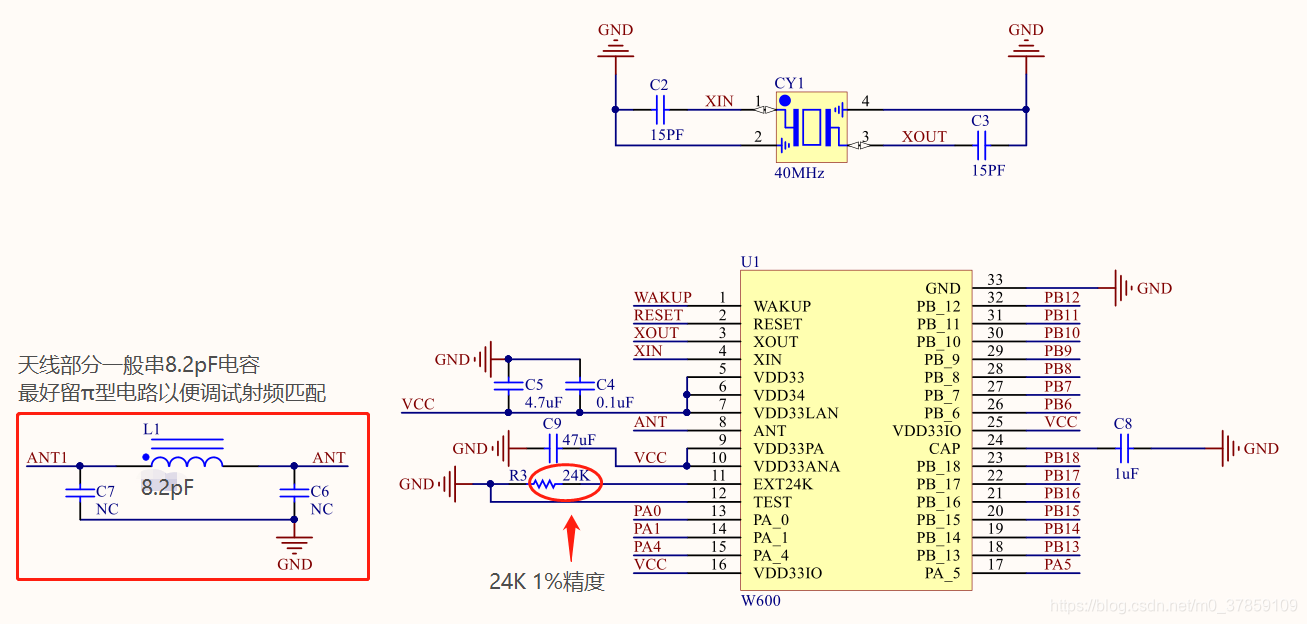

W600的硬件设计外围很简单,需要注意的是:

- 芯片5,6,7脚附件分别为 10uf 和 4.7nf 滤波器电容。

- 芯片9,10 脚附近放置 47uf 滤波电容。

- 芯片 11 脚需外接 24K 1%精度电阻。

- 芯片 24 脚需要外接 1uf 滤波电容。

- 射频部分空间允许情况下可以留π型网络,以便后期射频调试。(尤其是过认证要求会高一些)

- 晶振频率为40MHz,晶振匹配电容一般为15pF,由于各家晶振生产工艺,PCB走线设计等因素,可能需要根据实际情况调节匹配电容容值(频偏在±10ppm范围内较好)

设计前强烈建议看下官网《W600 芯片设计指导书》

最小系统可参考下图:

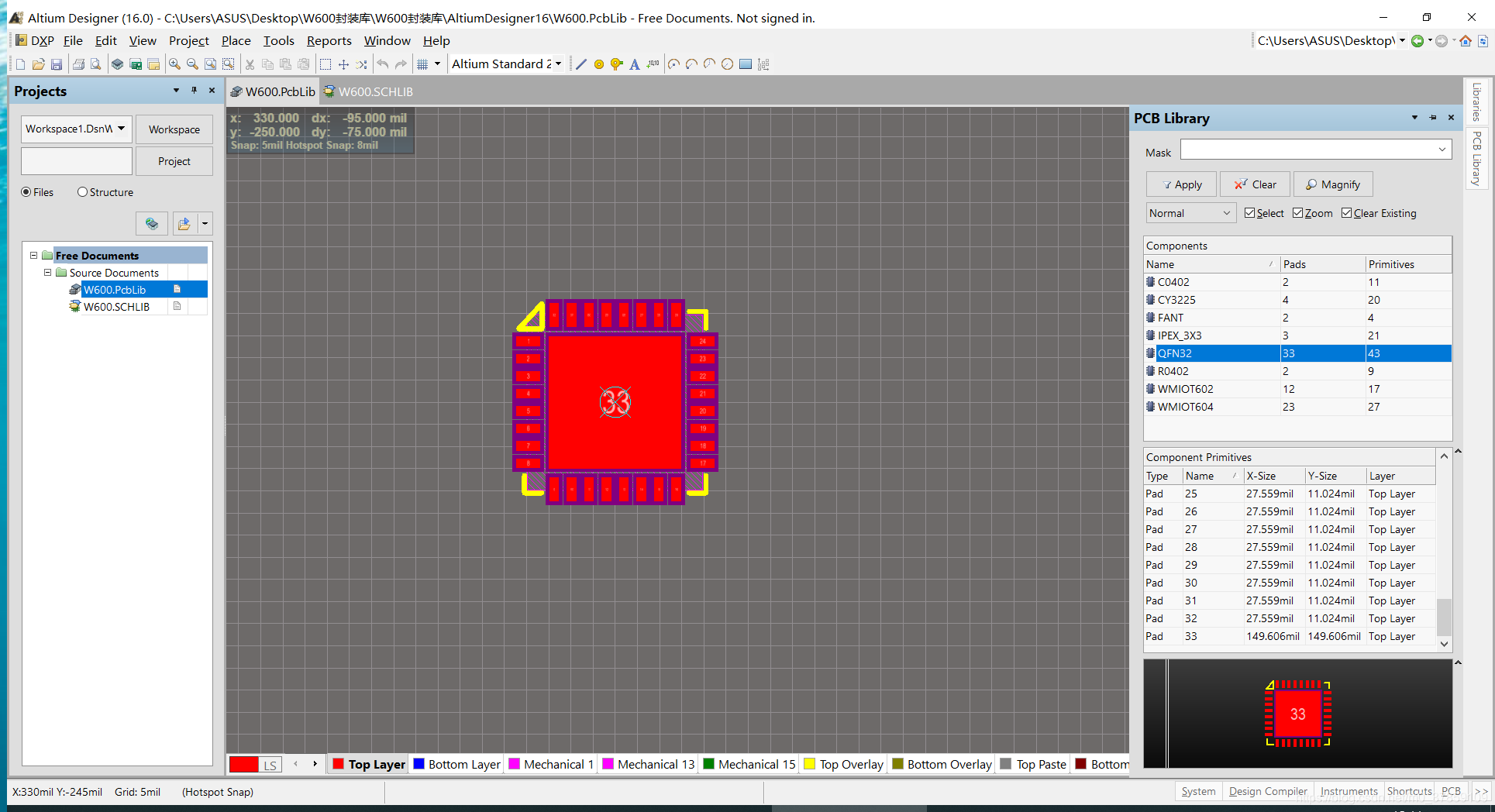

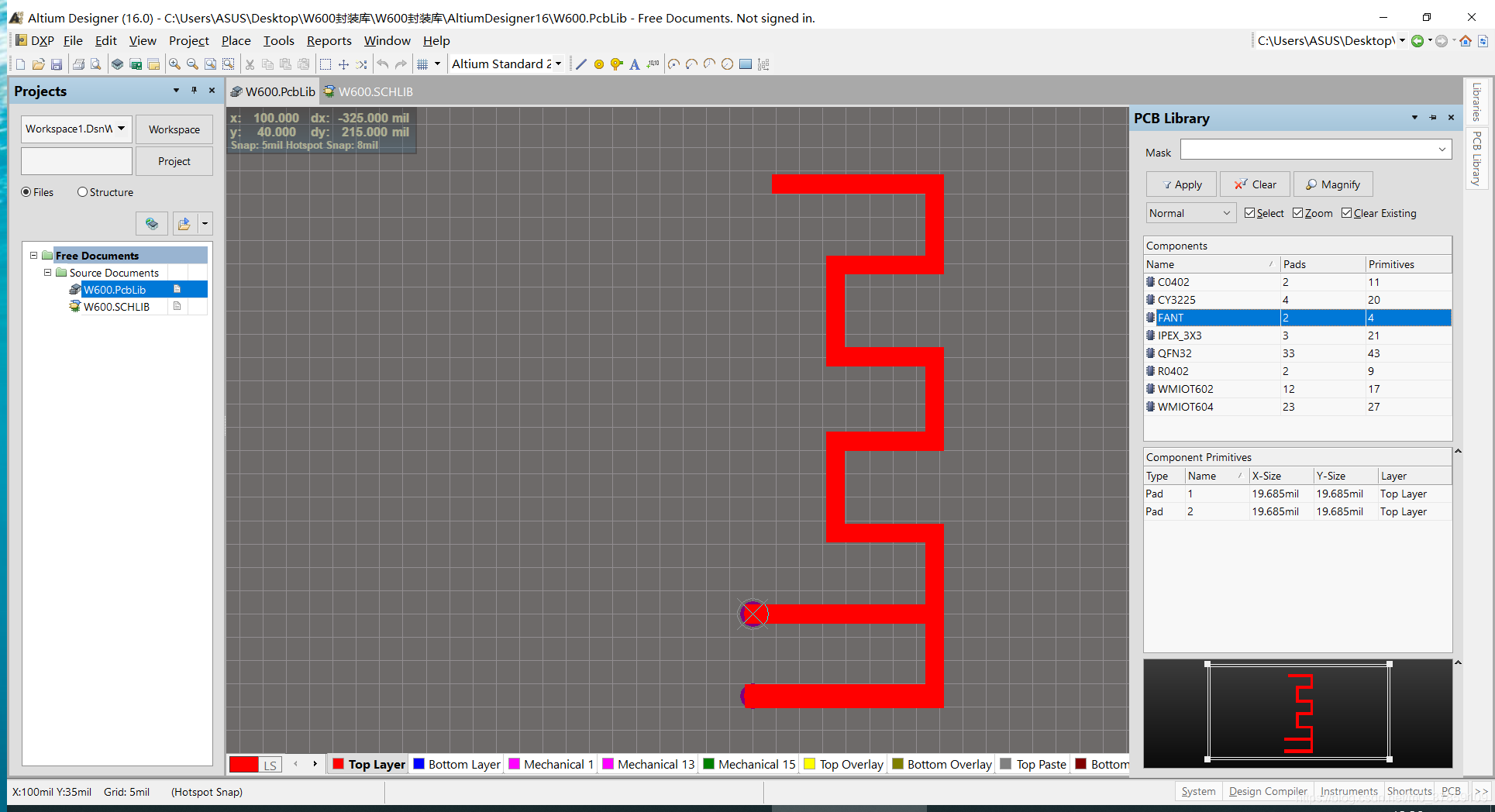

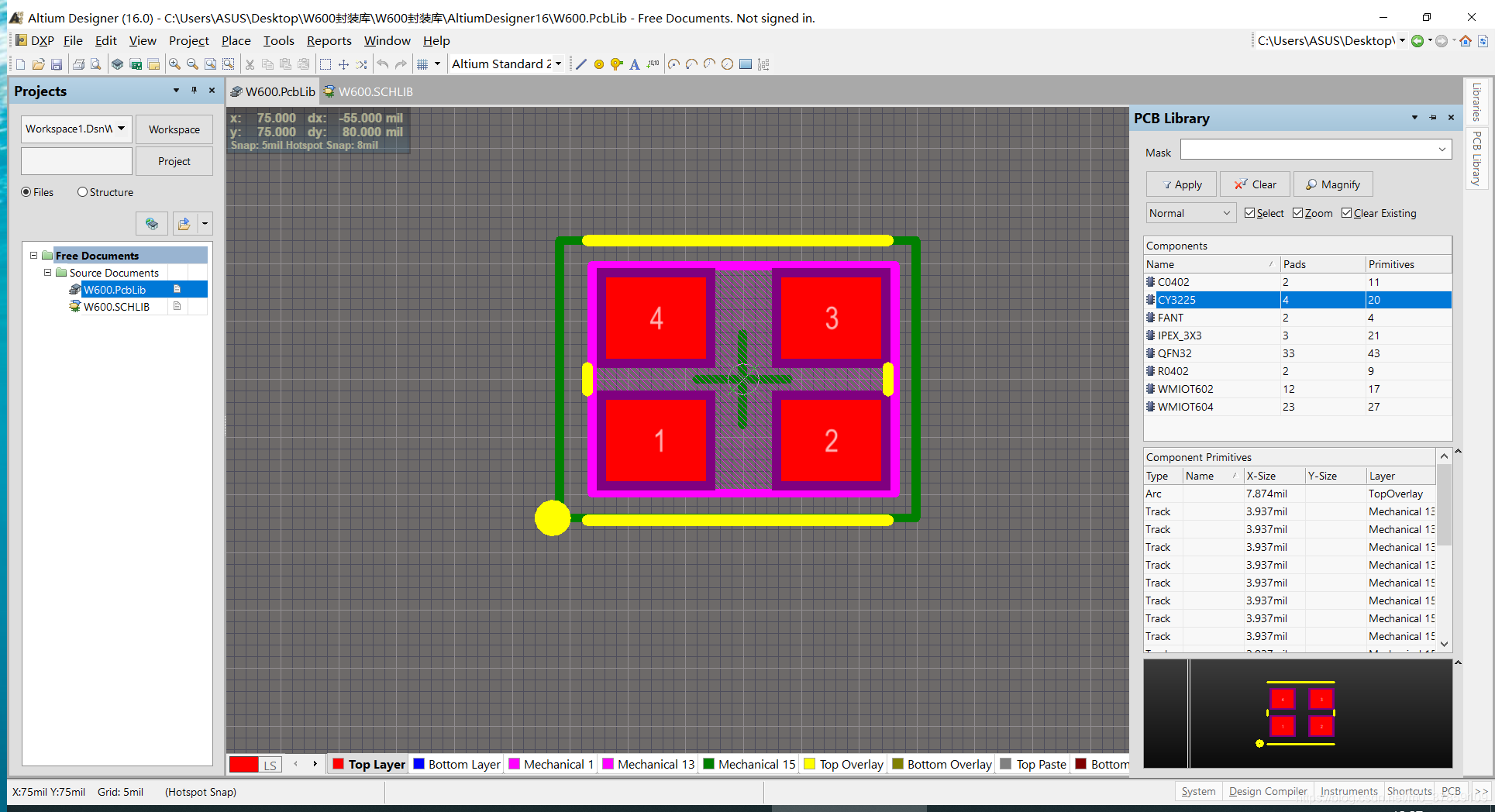

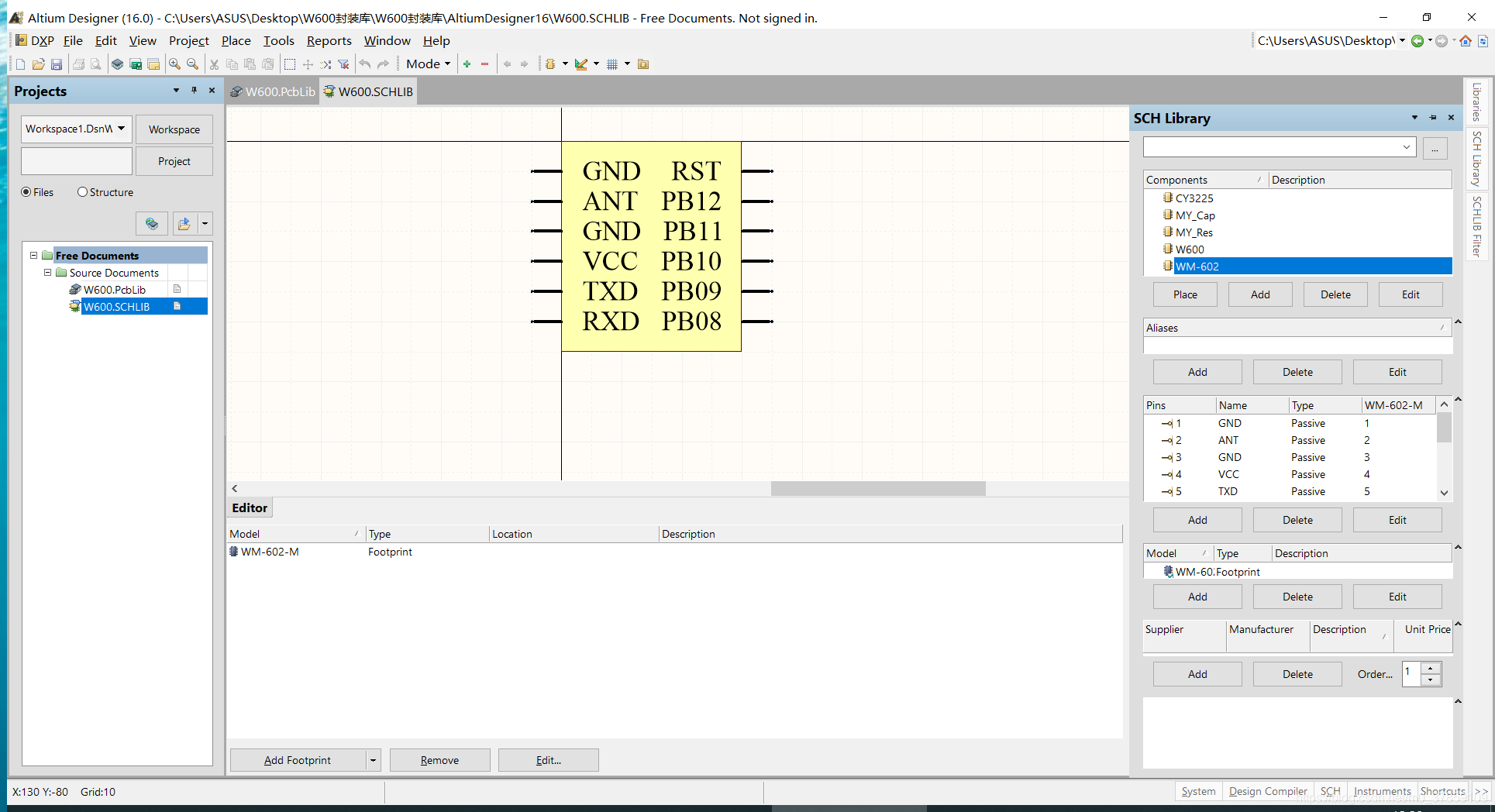

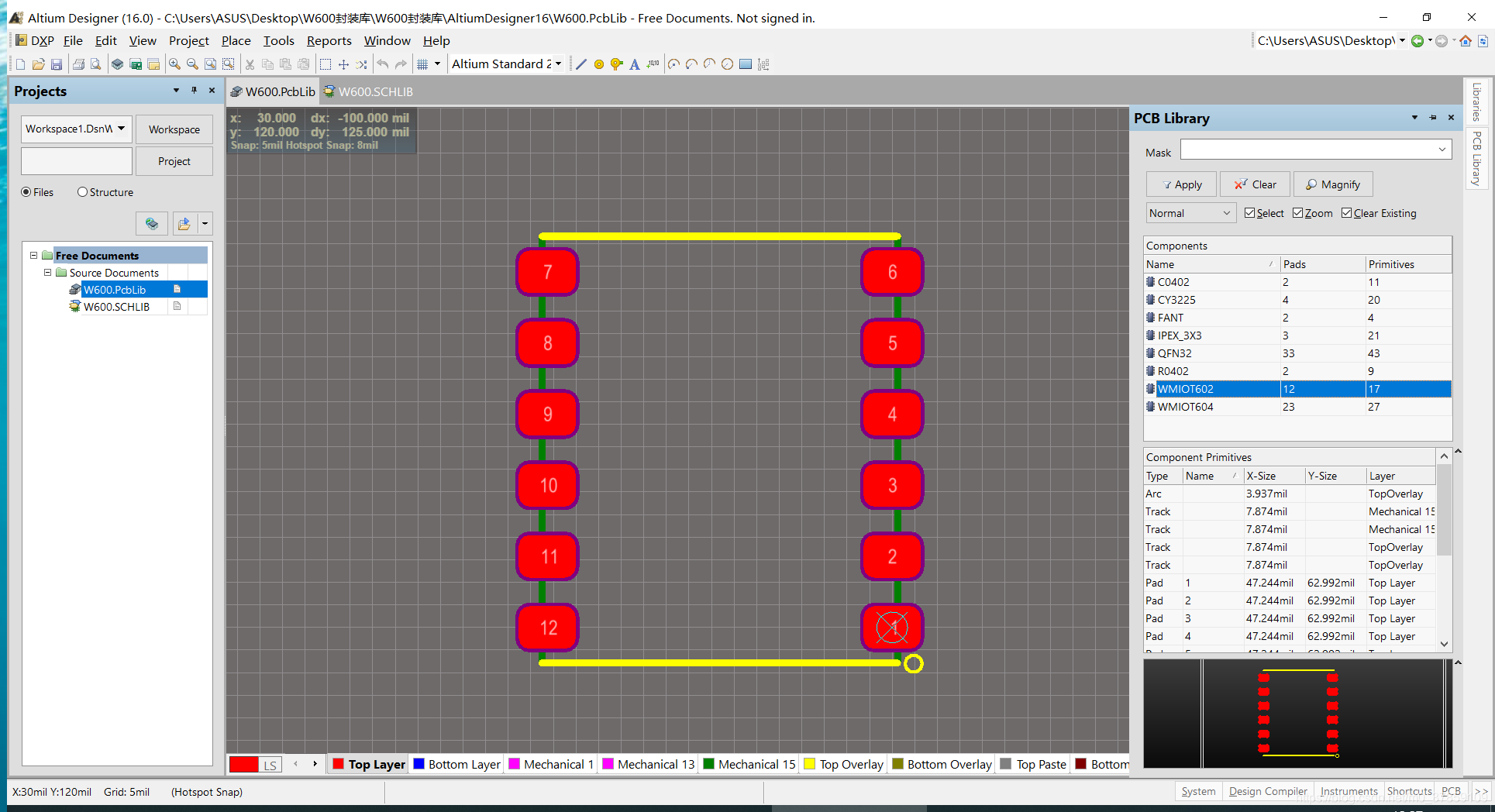

接下来是W600 可能用到PCB封装库文件供大家参考