目录

misunderstanding about data hazard

speculation based on hw

speculation is aiming to solve the particular problem happen in the architecture based on Tomasulo algorithm. it's a technique for reducing the effects of control dependences in a processor implementing.

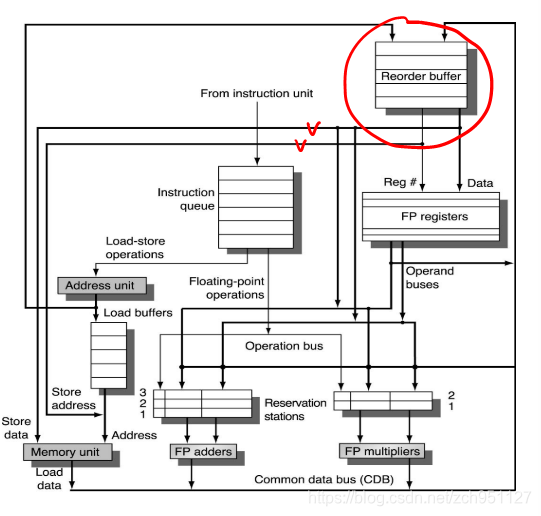

the main idea of this method is to add a reorder buffer between CDB and FP register. This buffer can provide data directly to the reservation station. the main function of this buffer is to allow data committed in order in the commit stage rather than write result stage. and only if the processor commits the result, it can be written to the register.

the following table shows the difference between the previous version of Tomasulo scheduling

multiple issue processor

the main idea of this method is to increase the thread of issuing instructions to reduce the clock cycle used by each instruction. in this way, the clock cycle used by instruction can be even less than 1 clock cycle. and the processor can commit two or even more results at the same time. (commit stage should be later than write result stage)

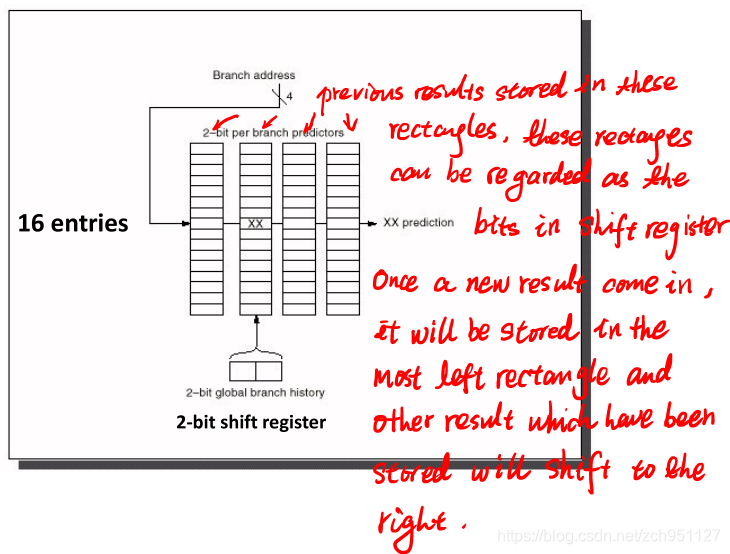

(m,n)correlating prediction

this method means that use the previous m branches' results to predict the result of the current branch result. They use the behavior of the last m branches to choose from 2m branch predictors, each of which is a n-bit predictor

e.g. (2,2) predictor implementation

(but I still feel confused about the prediction criteria)

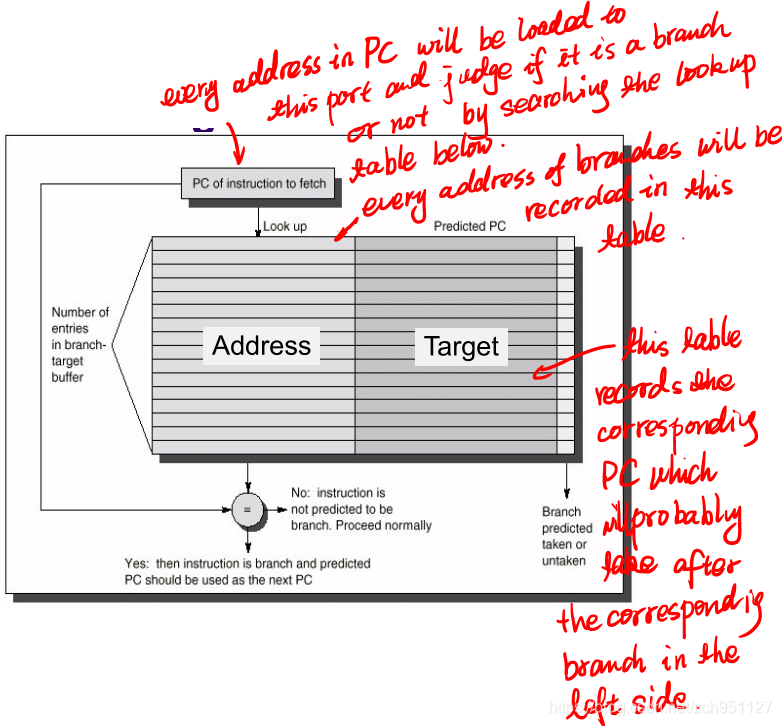

branch-target buffer

it's very easy to understand with the following diagram

misunderstanding about data hazard

there are 3 kinds of dependence may cause data hazard: data dependence, naming dependence(anti, output)

assume the sequence of instruction is i,j

data dependence: i writes the result in the register which will be used by j, and i and j is very close (there is a data flow between i and j)(WAR)

naming dependence: (no data flow between i and j)

anti: i uses the register written by j (RAW)

output: i and j use the same output register (WAW)