compiles with IEEE1364 : verilog语言的仿真基于分层的事件队列

VCS 仿真模块的顺序(先从没有延迟的事件开始,执行它们,然后把时间设为0,然后按照时间顺序依次执行各个时间,同一层的时间,什么执行顺序都是可以的):

(1)no delay(initial / always)

(2)set t=0

(3)active region

执行一些原语(UDP),$display,assigns,blocking assignments,nonblocking RHS

(4)inactive region (#0)

(5)Nonblocking assign region 非阻塞语句赋值

(6)monitor region ( $ strobe $ monitor ) 当变量发生变化,检测

(7)future region 其他指定的PLI命令语句

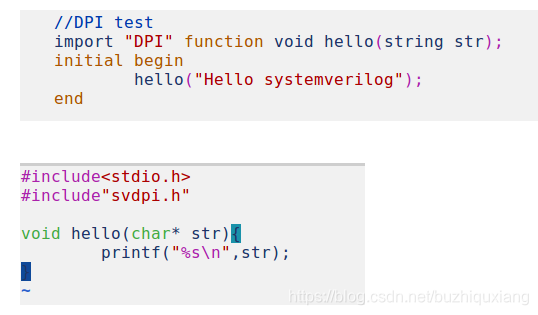

Verilog PLI(Programming Language Interface )是一种Verilog代码调用C/C++函数的机制。它能让Verilog像调用一些系统调用(如 $display/ $stop/ $random)一样调用用户编写的C/C++函数,这样我们可以用C/C++语言开始自己的system task/function, 来实现用verilog不太方便的功能,并与外界建立了联系。

VCS 的运行方式有两种,一种是交互模式(interactive mode),一种是批处理模式(batch

mode),两种方式各有优劣,具体用在不同的情况下。在测试小模块或者底层模块,情况不

太复杂的时候,而又需要很详细信息的时候,可以采用交互模式,交互性能更好,显示更直

观;当进行复杂测试而关注于整体性能,而不必去查看每个信号的时候,只需要查看所需要

关心的信号即可,这种情况可以用批处理模式

- Interactive Simulator Controls

步骤:RTL、TB(加入vcspluson 否则无法debug)

直接输入命令

vcs souce_file -full64 +v2k debug_pp -l compile.log

./simv -gui -l fsm.log

或者

vcs souce_file -full64 +v2k debug_pp -R -gui -l - post-processing with VCD+ files

编写makefile对电路进行处理,一般用于后期的仿真

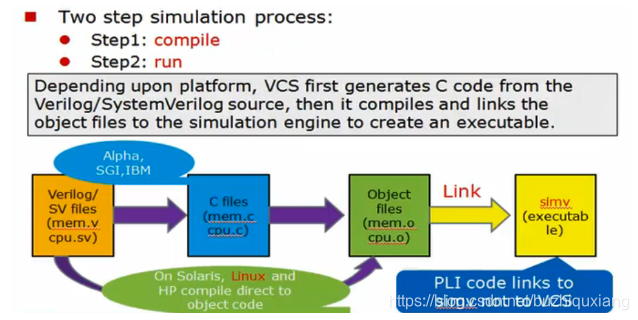

(一)编译compile

VCS对源文件进行编译,生成中间文件和可执行文件

-

-Mupdate (Incremental compilation (only changed files are compiled)

-

-R (Run after compilation)

-

-gui (Starts the DVE gui at runtime)

-

-l filename (set log file name)

-

-sverilog (Enable SystemVerilog language support)

-

+v2k (compile with support for verilog 2001 extensions)

-

-v lib_file (search for unresolved module reference in the lib_file)寻找设计文件中缺少的UDP或模块(寻找设计文件中未定义但已实例引用的UDP或模块编译器)

-

-y lib_dir (search for unresolved module reference in files residing in directory lib_dir)

-

+libext+lib_ext (vcs 在参考库目录下寻找以.v和.vhd为扩展名的文件,多个扩展名之间用“+”连接)

-

+licdir+inc_dir (search inc_dir directory for `include files)

-

-f file(File containing a list of absolute pathnames for the source_files and a subset of VCS options)

-

-o foo(Creats executable foo instead of simv)

-

-full64 (vcs 以64位模式编译,生成64位的simv)

-

-comp64(vcs 以64位模式编译,生成32位的simv)

-

-debug_pp (产生vpd文件,enable DVE for post-processing)

-

-debug (相对于-debug_pp,多了UCLI调试功能)

-

-debug_all (相对于-debug_all,多了单步调试功能)

-

-notice 给出详细的编译信息

-

-q 不在终端输出编译时的信息

-

+define+macrol+ 将宏macrol传给源代码

-

+notimingcheck 禁止时序检查任务,改善仿真速度

-

-E echo (displays compile-time options used for the creation of the current simv executable)

-

-s (编译之后,运行simv时,仿真时刻停止在0处)

-

+rad (开启仿真时的radiant技术,会将代码进行优化,会增加编译时间)

Improve RTL simulation performance by using the +rad compile time switch,Fast RTL-level verification can be able to Improve RTL simulation performance with good coding styles.

good coding styles:

(1)use synthesizable subset of verilog language

1、Give VCS better chance of perform code optimization

(2)raise your level of abstraction

1、give simulator less work to do

(3)avoid inefficient constructs

1、switch level primitive and bidirectional

2、strength modeling

(4)use small stimulus blocks

1、avoid large initial blocks(<10000 line of code)

2、use file based stimulus (例如readmemh) -

-timescale=<time_unit>/<time_precision>

-

+race (自动产生一个race.out 文件,列出竞争)

-

+prof (产生一个vcs.prof文件,报告CPU和memory的使用情况,可以找到关键路径和memory consumption)

-

-xzcheck (当一个条件等于x、z的值,VCS给出警告信息,可以在模块中加入$xzcheckoff 和 $xzcheckon)

-

-line (实现单步仿真,将会极大地增加运行时间)

-

-nospecify (禁止模块路径延迟和时序检查,提高仿真速度)

(二)simulation

Simulation results reported via

(1) Verilog system task calls

(2) User defined PLI routines

Three general debugging methods:

(1) verilog SystemVerilog System Task calls

(2) VCS UCLI

(3) VCS DVE(GUI)

Four factors to consider:

- simulation speed

- signal visibility

- signal tractability

- usability

系统任务:

- Debug visibility:

(1)$ display (prints formatted message to console)

(2)$ strobe(Like $display except printing is delayed until all events in the current time step have executed)

(3) $ monitor (Monitor signals listed and prints formatted message whenever one of the listed signals changes)

(4)$time (Returns current simulation time as a 64bits integer) - stopping simulation

(1)$ stop (Halts simulation like a breakpoint)

(2) $finish (Halts simulation and terminated the simulation) - Simulation stimulus and reference

(1)$ readmemh/$readmemb (reads ASCII data from a disk file,each digit is hexadecimal/binary) - Read/Write commands:

(1)$force [-deposit] [-freeze] [-drive] path value

(2) $release path

(3) $memory-read | -write nid -file filename [-radix radix][-start start_address][-end end_address] - 调试DVE(Discovery Visual Environment)

(1)$dumpvars (创建一个VCD文件)

(2) $vcdplusfile(“filename”); (指定一个vpd文件名代替默认vcdplus.vpd)

(3) $vcdpluson(level,instance,net_or_reg) (开始创建一个vpd文件,level表示记录的层次,0或者缺省表示所有层;instance为模块的例化名;net_or_reg为net变量或reg变量,缺省时记录所有的变量)

(4) $vcdplusoff(instance,net_or_reg) (停止写vpd文件)

(5) $vcdplusautoflushon (当vcs遇到中断时,将仿真结果写入vpd文件中)

(6) $vcdplusautoflushoff (关闭自动flush)

(7) $test $plusargs (在testbench中包括该任务,可以在仿真中加入该任务的参数来控制某段代码是否执行)

initial

if($test$plusargs("postprocess"))

begin

$vcdpluson;

#10000 $vcdplusoff;

end

//运行时,simv+postprocess 即可执行if中的代码,否则不执行

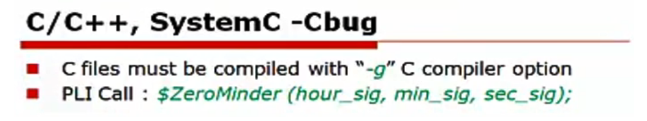

(三)C/C++, System C

最终可debug PLI命令语句(可以使用ctrl+c kill halt simulation, $ display 和$monitor print out to determine the cause of the problem)

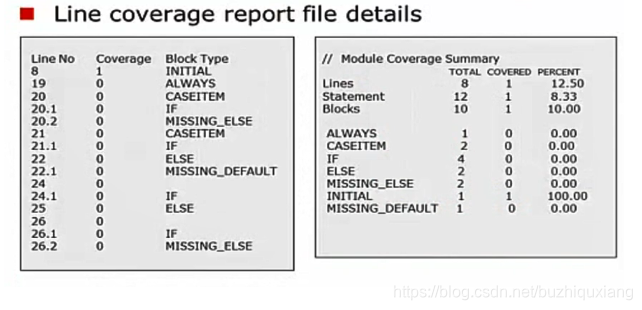

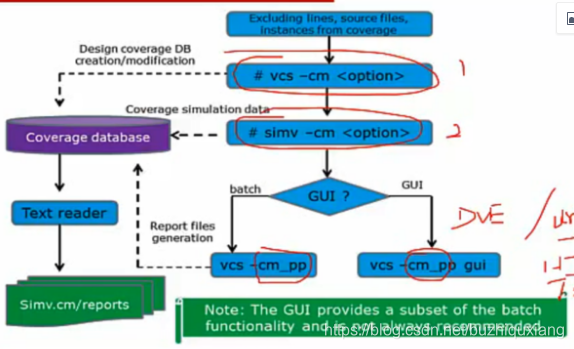

(四)code coverage

1、statement or line coverage:检测哪一行,哪一条语句没有执行

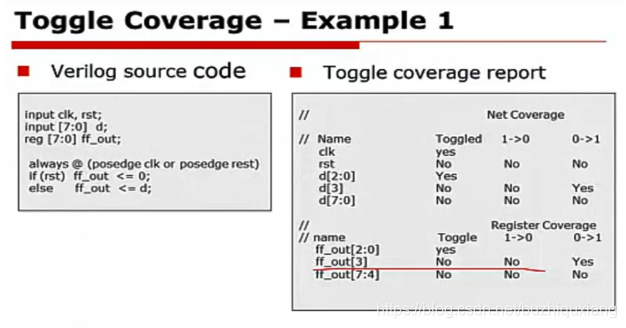

2、toggle coverage:检测net、reg和向量中的每一位是否都经过了0->1和1->0的跳转

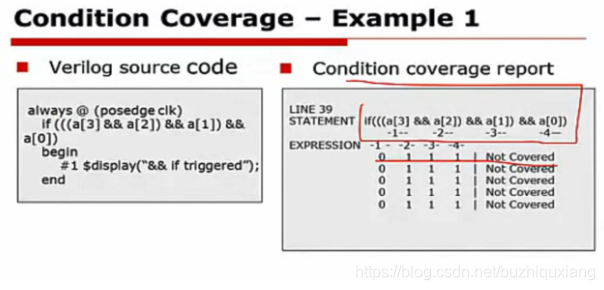

3、conditional coverage:检测代码的条件为1或0是否都出现过

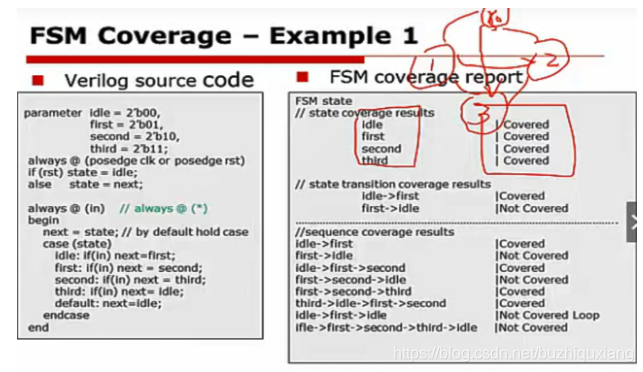

4、fsm coverage:检测状态的跳转和哪一个状态没有被跳转到,以及错误的状态跳转

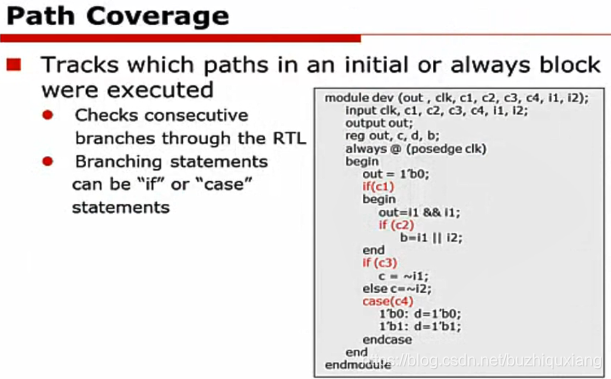

5、path coverage:显示initial和always块中所有条件的组合是否实现

VCS Coverage Metrics

- Batch mode:to generate coverage report file and graded test cases

vcs -cm_pp -cm line -cm_dir directory -cm_hier hieroptions - GUI mode:to show and manipulate coverage data in graphical form

vcs -cm_pp -cm line -cm_dir directory -cm_hier hieroptions -gui

vcs sourcefiles -cm <coverage_type> < other coverage options>

- 其中-cm <coverage_type> specifies the type of coverage to collect:(The options are line、tgl、cond、fsm、path)

- -cm_dir: to specify an alternate location and name of the coverage database

- rename simv.cm with -o

- -cm_hier: (configuration file,which includes/excludes parts of design for different kinds of coverage)

- -cm_name :specifies the name of report files (instead of default cmview),usually defines testcase name for coverage database.

transport delay:小于该延迟的脉冲仍然可以通过

inertial delay:小于该延迟的脉冲无法通过,默认的sdf文件中的gates、switchs、UDP、module input port delay、和连续赋值的延迟都是惯性延迟。