主存(Main Memory)

主存储器简称主存,用来存放程序运行期间的大量程序和数据。存主存主要由半导体器件组成,一个双稳态半导体电路可以组成一个存储元,即表示可以存储1 “位”(位)二进制代码。若干个存储元构成一个存储单元,每个存储单元有唯一的编号,称为地址。许多存储单元构成一个存储器。存储内容断电后即消失,为非永久性存储器,在内存中的地址是以字节为基本单位的,是从小到大连续的,一个存储单元至少包含一个字节,也可包含多个字节。

高速缓存Cache

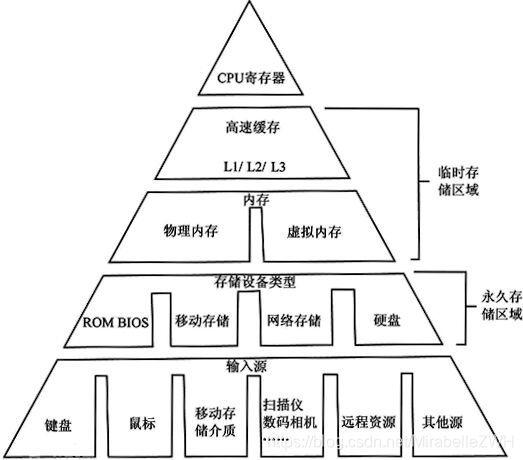

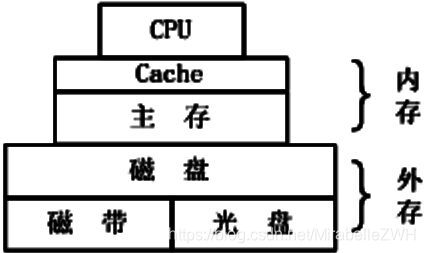

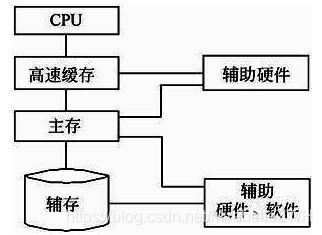

Cache是一种高速缓冲存储器,目的是为了解决CPU与主存之间速度不匹配的问题,为了追求快速,包括控制与管理等所有的功能全部由硬件实现,对程序员是透明的.Cache在存储器层次结构中的位置如图所示。

缓存的基本原理

CPU缓存与的之间交换数据是以字为单位的,而主缓存存与之间的数据交换是以块为单位的。当CPU需要读取一个数据时,便用该数据的内存地址访问内存,并迅速判定该地址中的信息是否已进入高速缓存中,若进入,则将内存地址变换为高速缓存地址,立即访问高速缓存。若不在,则将该数据从内存中读出送往CPU,与此同时,把含有这个数据的整个数据块从主存中读取送到缓存中,任何时候缓存中的信息都是主存中某一部分信息的副本

Cache的命中率

命中率:在一个程序执行期间,设Nc个表示缓存完成存取的总次数,NM表示主存完成的总次数,高速缓存的命中率定定义为,则有:H = NC /(NC + Nm)的

平均访问时间:若TC表示命中时缓存访问时间,1-h表示未命中率,则缓存存储系统的平均访问时间ta为:ta = h tc +(1-h)tm。

缓存存储系统速度提高倍数R:使用高速缓存比不使用高速缓存的CPU访问存储器速度提高的倍数R = TM / TA。

存主与高速缓存地址的映射

在CPU需要读写指令和数据时,送出的是指令和数据的主存地址,为了从高速缓存存储器中读写信息,必须采用某种方法把主存地址转换为高速缓存存储器的地址,称为地址映象。

地址映射方式有全相联映象方式,直接映象方式和组相联映象方式三种。

全相联映象方式

将主存中的一个块直接拷贝产品到缓存中任意一块上,高速缓存的数据块大小与主存的数据块存储的数据量大小相等。

主存的块调入缓存中的位置不受限制,所以冲突率最低:优点。

缺点:无法从主存地址中直接获得缓存的块号,变换复杂,速度较慢。

直接映象方式

的英文一个主存块只能直接拷贝产品产品到高速缓存的一个固定的位置上去,做法是将主存分成与高速缓存一样大小的区,每个区的第0块只能调入到高速缓存的第0块上,第1块只能放到第1块,其他依次类推直接映象方式是一种多对一的映射关系。

优点:地址变换很简单,访问速度快。

缺点:不同区的相同块号不能同时放进缓存,即便高速缓存内有空闲块,所以冲突率最大。

组相联映象方式

是前两种方式的折衷,是将主存中的区和高速缓存中的块再分成组,主存的每个区和高速缓存的大小一样,将主存中每个区和高速缓存中的每4块分为一组,主存中每个区就分为2组,分别是第0组和第1组,而高速缓存也一样,分为第0组第1组。这里规定主存中的组采取直接映像方式而块采取全相连映像方式。即主存中任何区的0组只能放存放到高速缓存中的0组,1组只能存放到高速缓存中1组,依此类推。而组内的块则采用全相连映像方式,即主存一组内的块可任意存到高速缓存相应组号内的任意块中。