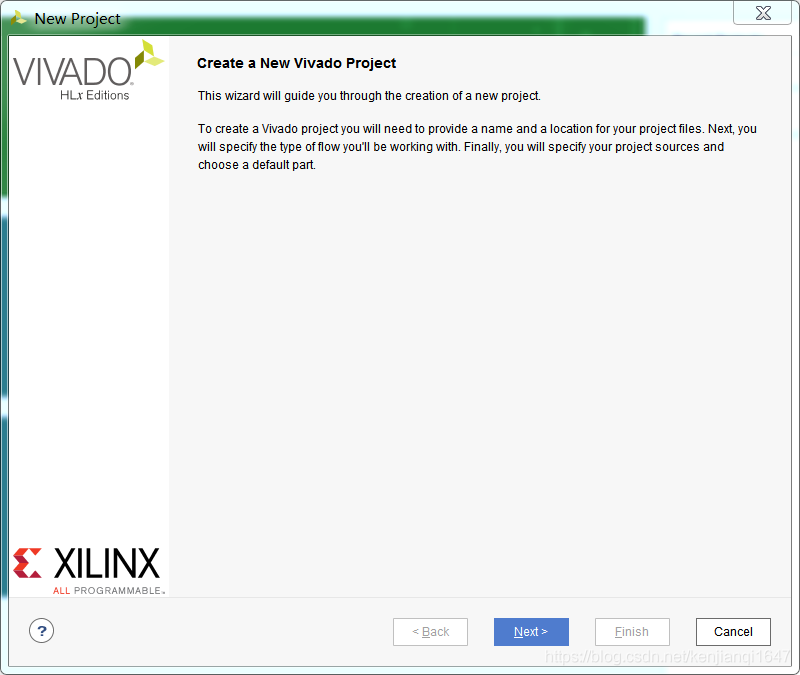

一、创建工程

1、Create Project

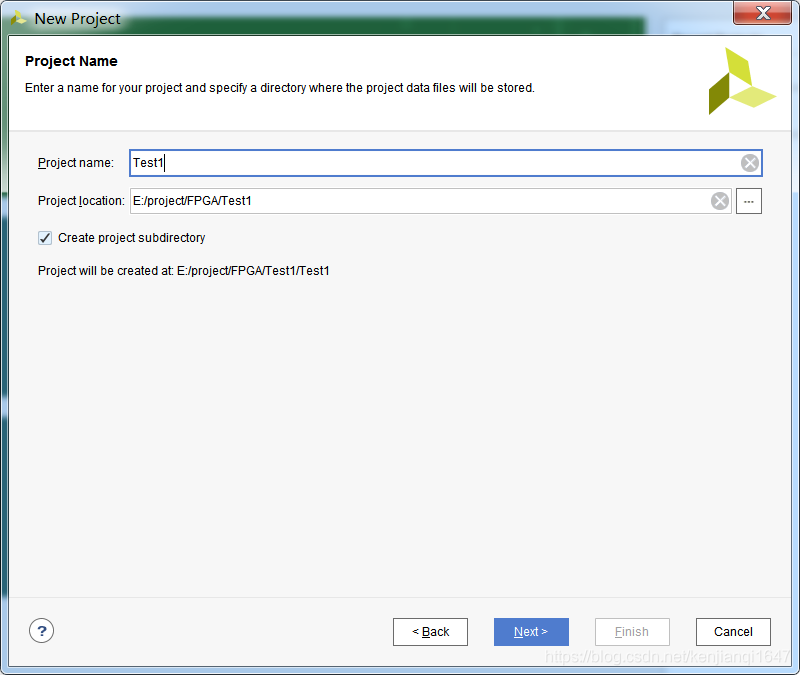

2、填写工程名和路径

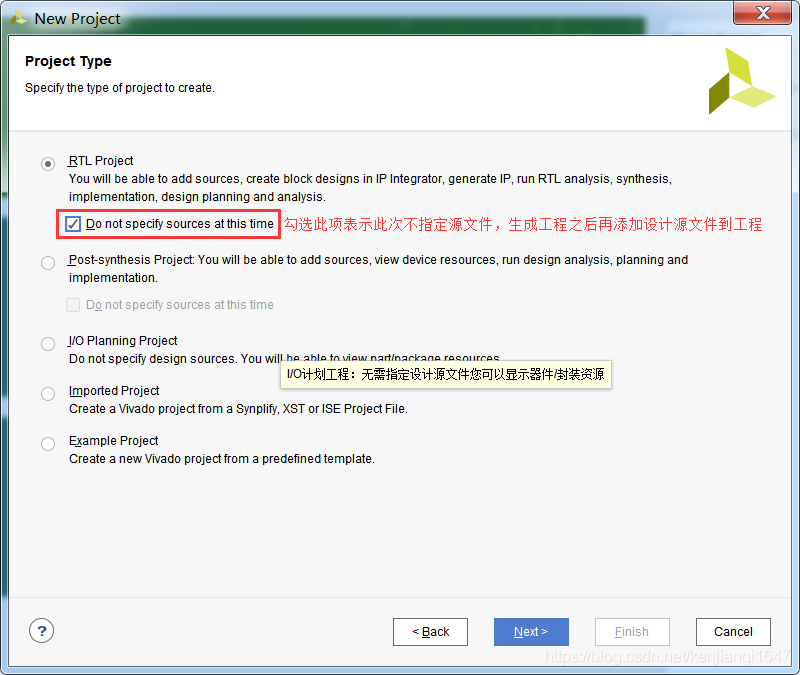

3、选择创建RTL工程

4、选择使用的芯片型号或开发板型号

5、完成

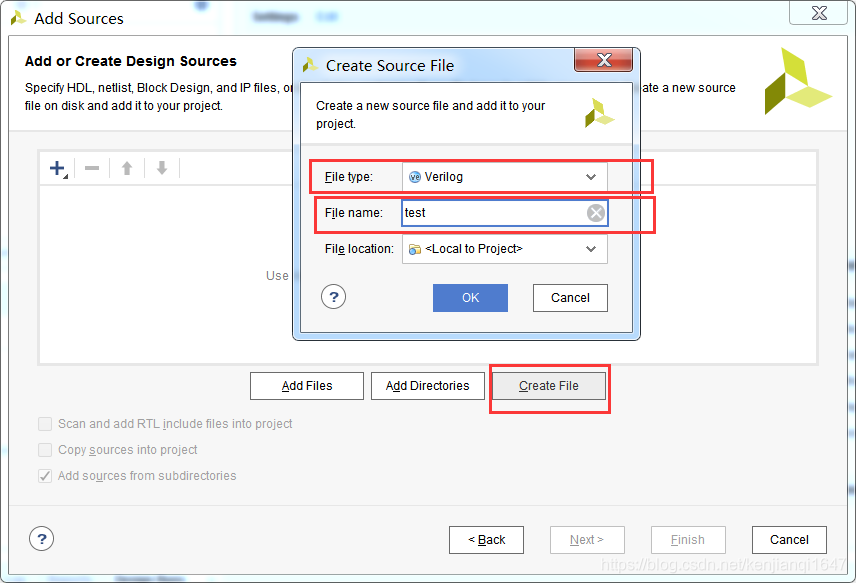

二、添加一个设计文件

1、Add Source

2、添加设计文件

3、完成后,可以添加输入、输出引脚,也可以忽略后下一步添加

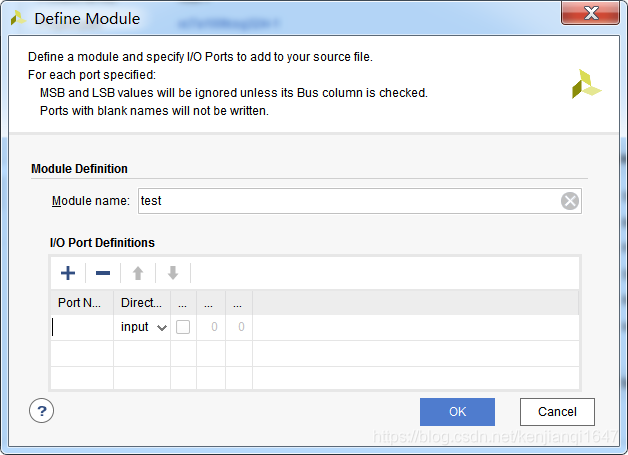

4、打开.v文件,编辑

默认的字体比较小,可以通过以下方法进行修改

编写内容:做一个简单的测试

module test(

input a,

input b,

output [5:0] z

);

assign z[0]=a&b;

assign z[1]=~a&b;

assign z[2]=a|b;

assign z[3]=~(a|b);

assign z[4]=a^b;

assign z[5]=a~^b;

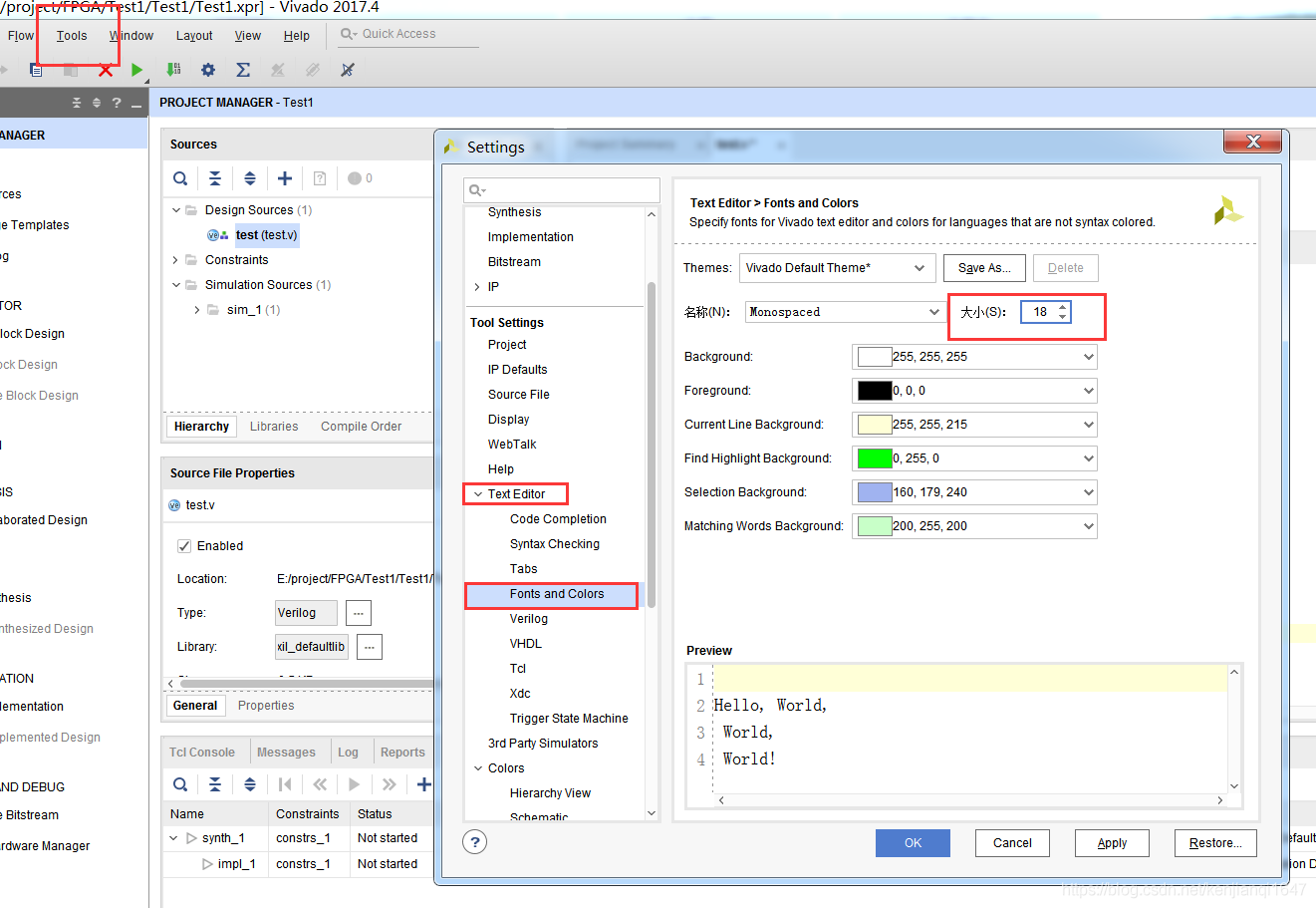

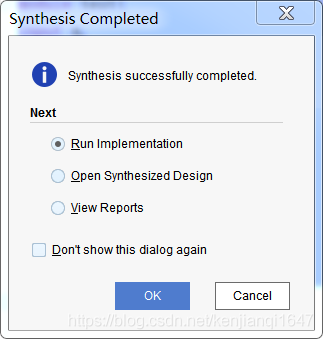

endmodule5、综合

没有错误之后,弹出

6、行为级仿真

(1)添加仿真文件 Add Sources

(2)编写仿真文件,并保存

注意test为被仿真的文件名

module test_sim(

);

reg a;

reg b;

wire [5:0] z;

test uut(

.a(a),

.b(b),

.z(z)

);

initial

begin

while(1)

begin

a=0;

b=0;

#100;

a=0;

b=1;

#100;

a=1;

b=0;

#100;

a=1;

b=1;

#100;

end

end

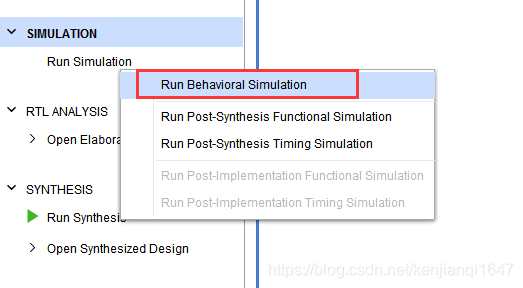

endmodule(3)启动行为仿真

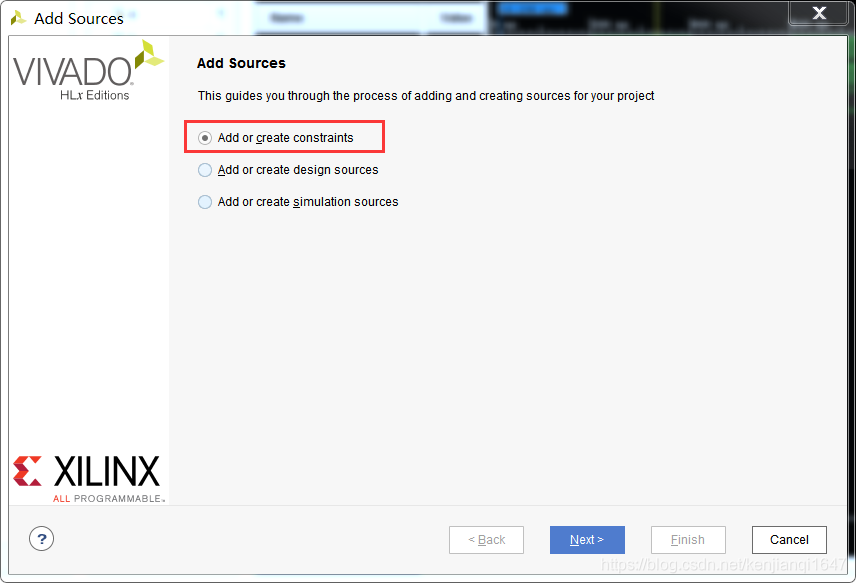

7、创建实现约束

约束的方法有两种,一种通过GUI设置约束;另一种通过文本编辑的方法实现约束

GUI设置约束:

(1)Add Source

(2) 创建文件

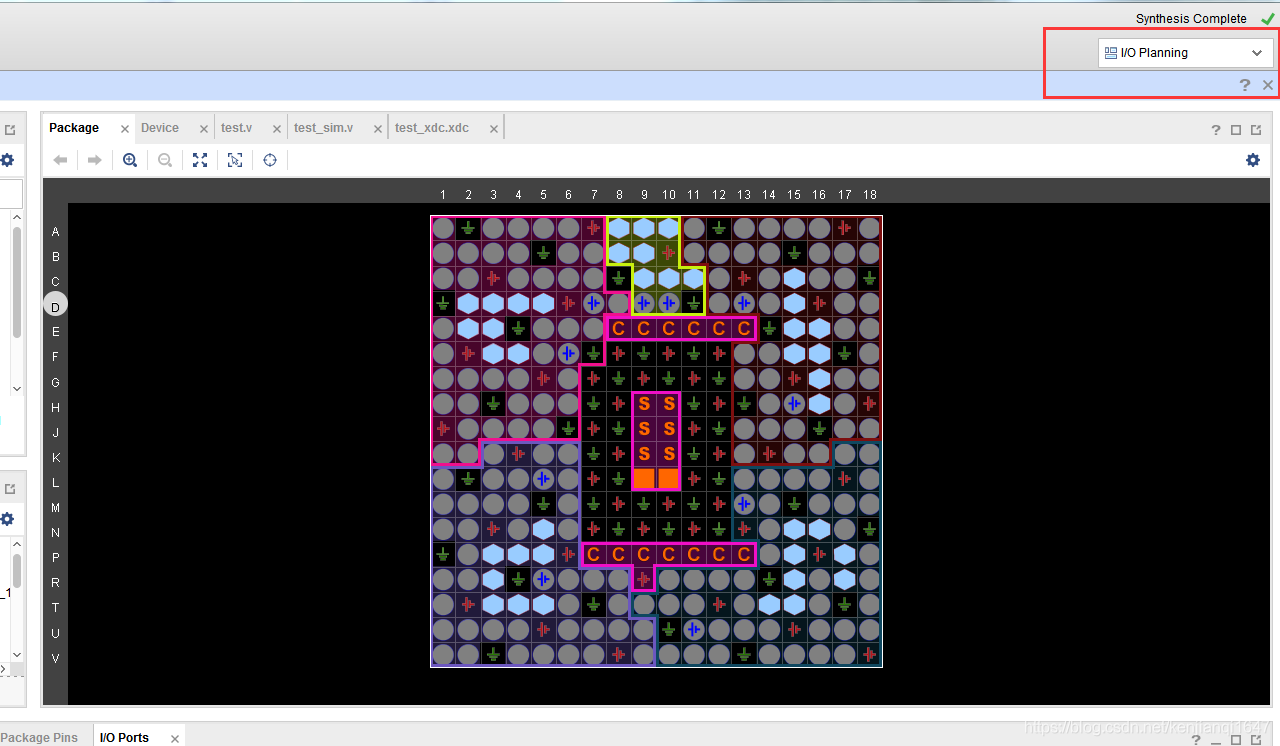

(3)启动I/O Planning

需要综合后,点击Open Synthesized Design后,右上角选择I/O Planning

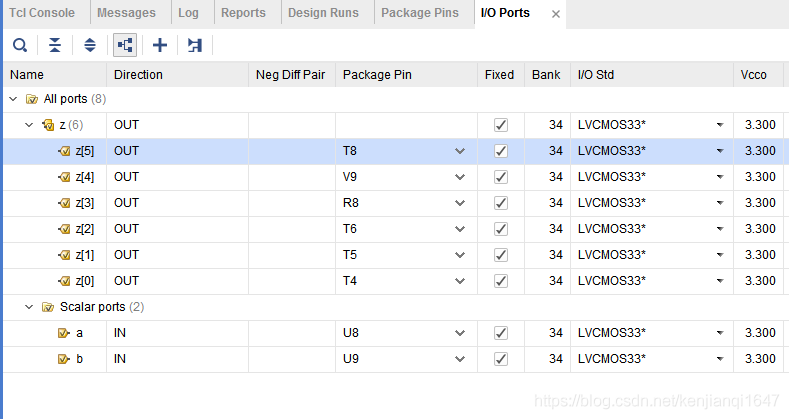

设置端口

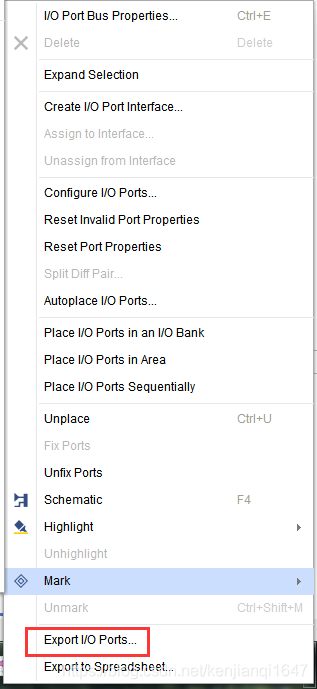

完成之后,右键单击

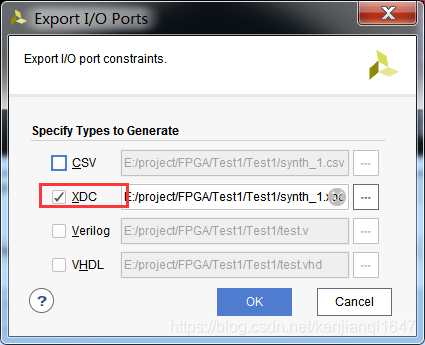

勾选XDC

注意XDC文件右侧的输出路径要设置成前面自己新建的XDC文件的路径。

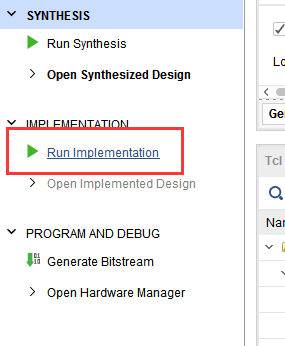

8、实现

选中.V文件

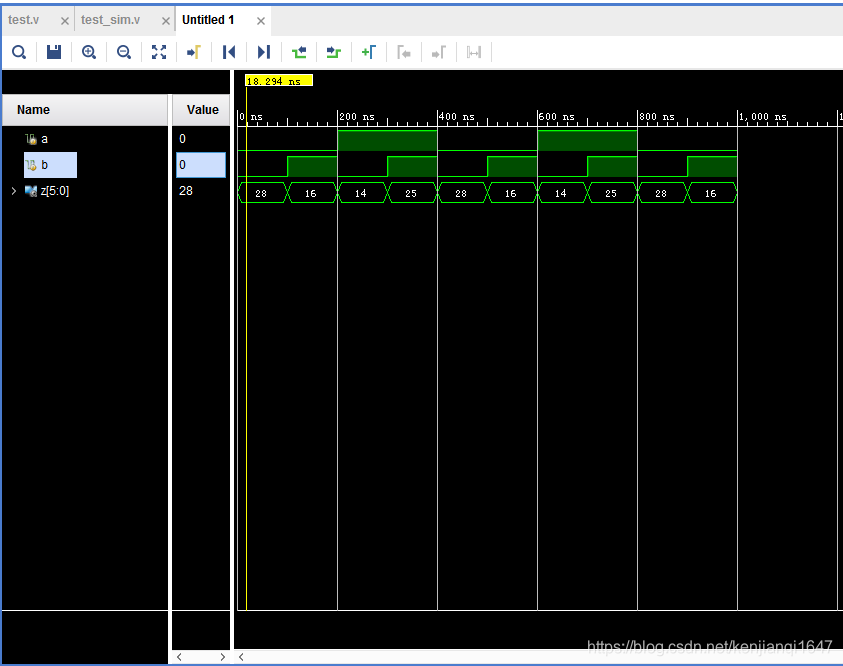

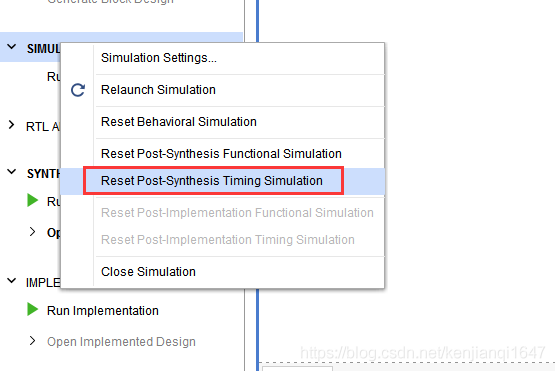

9、设计时序仿真

时序仿真和行为级仿真最大的不同点在于时序仿真带有标准延迟格式,而行为级仿真不带有时序信息。毛刺、竞争冒险等时序问题都会表现在设计时序仿真中。

选择.v文件,找到“Simulation”,运行实现后时序仿真选项

查看仿真效果

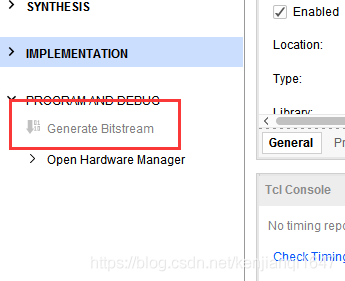

10、生成编程文件

(1)选中.v文件

(2)点击生成比特流文件

三、下载比特流文件到FPGA

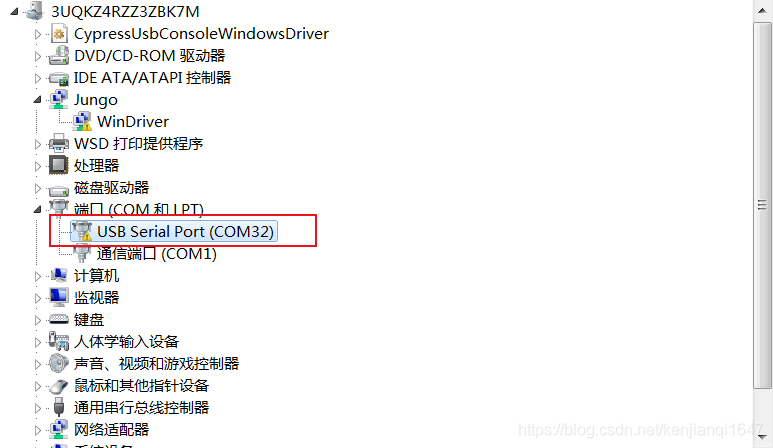

1、Nexys通过USB连接电脑

首次连接需要安装驱动,才能识别Nexys4,可以使用驱动精灵或驱动人生软件自动安装

连接之后,我的是com32端口,虽然带有警告标志,不影响后面下载程序

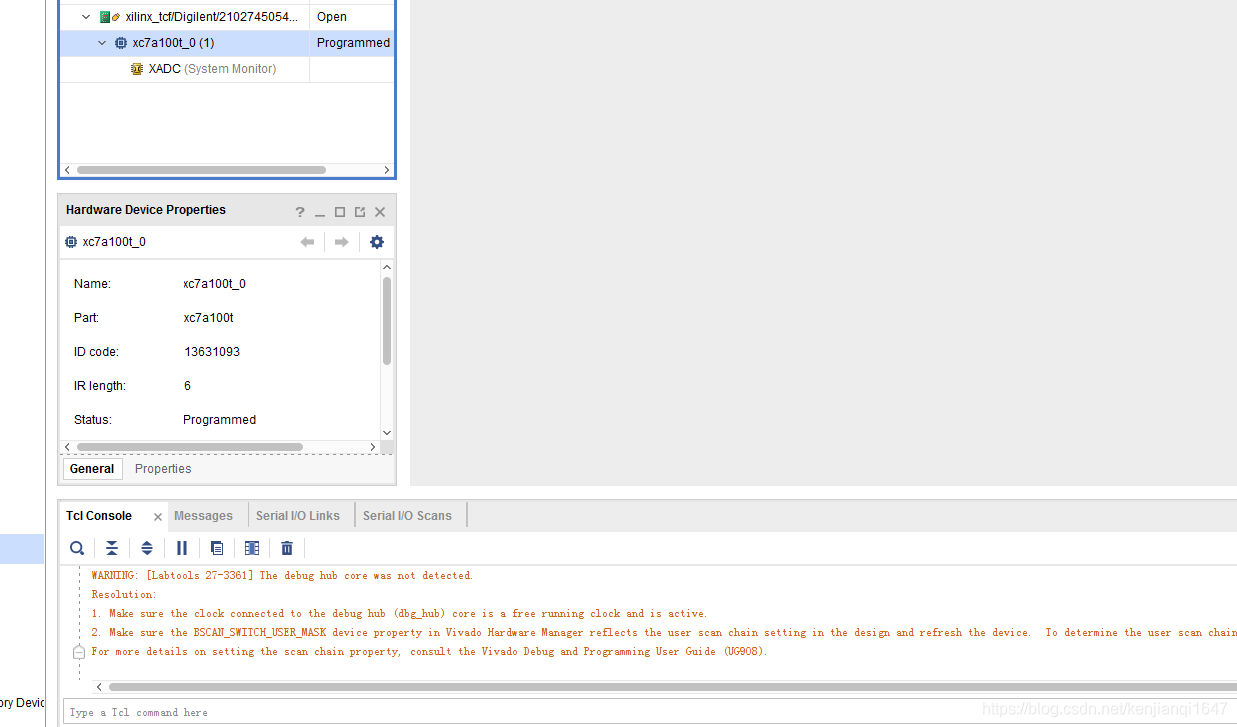

2、连接开发板

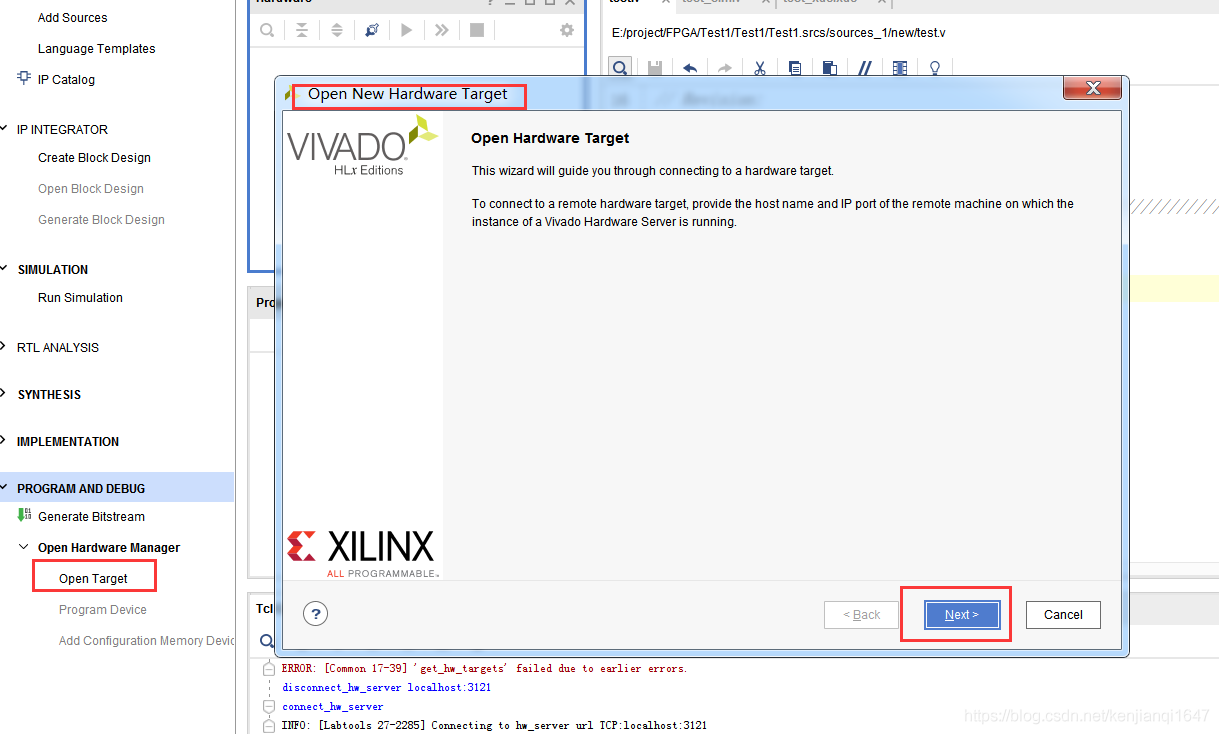

(1)PROGRAM AND DEBUG - Open Hardware Manager - open target - open New Target...

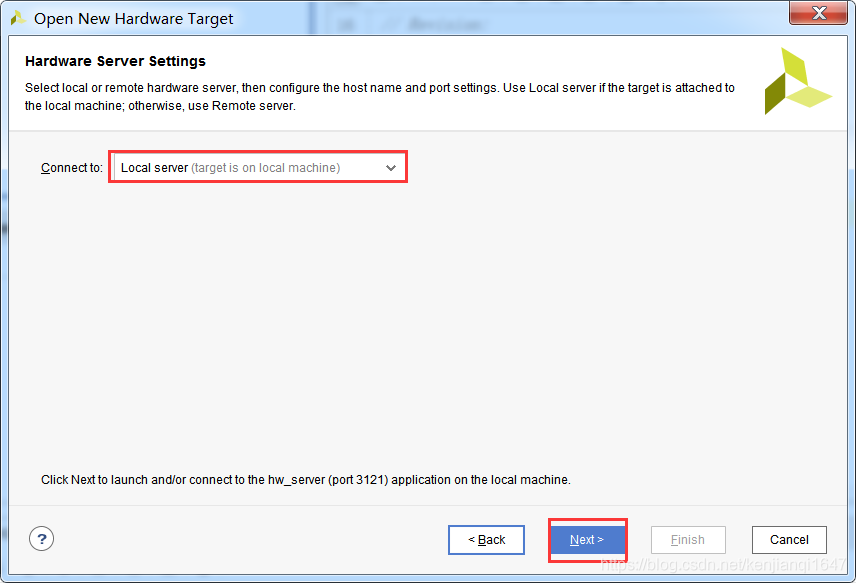

(2)选择Local server

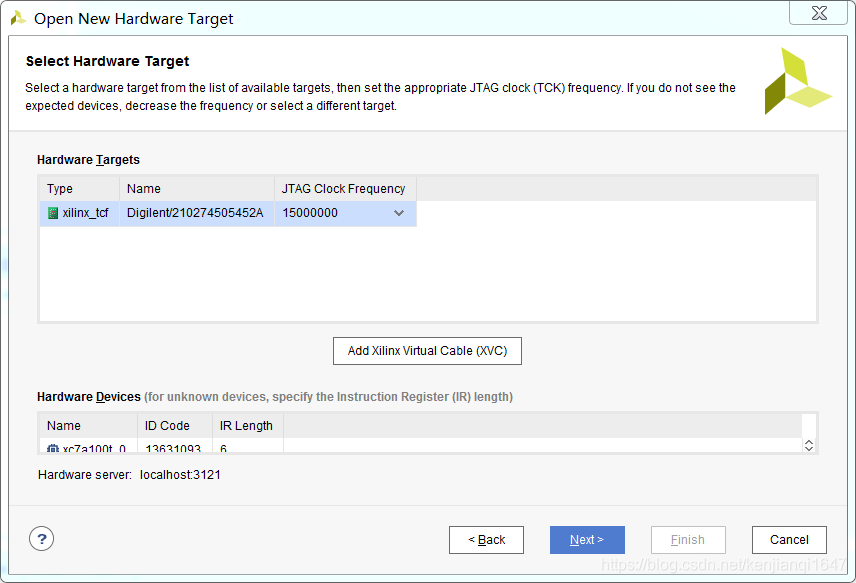

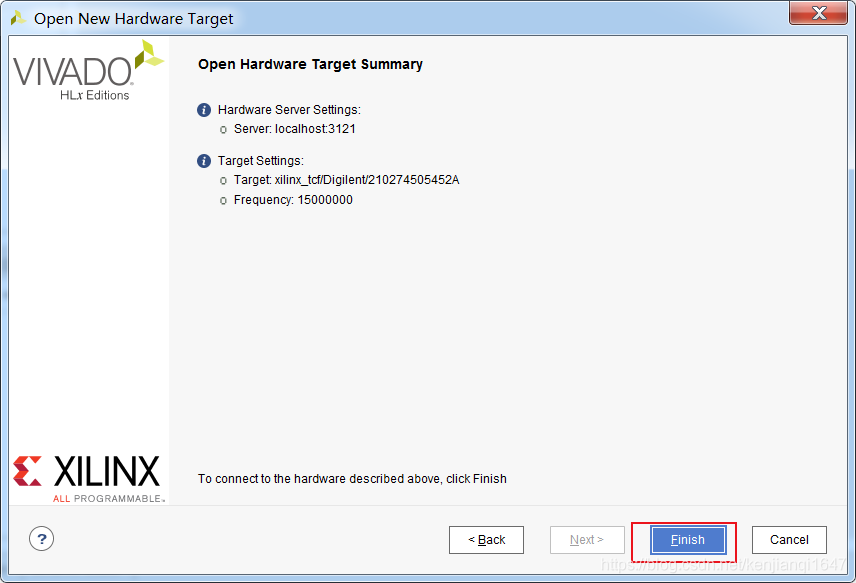

Next后找到设备

3、下载bit文件

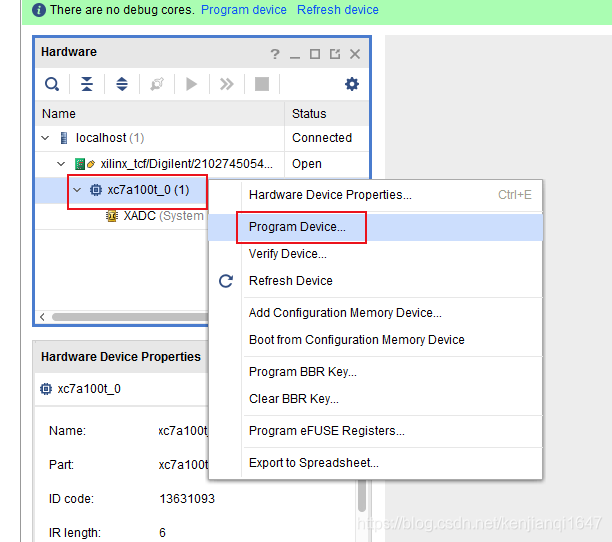

(1)选中找到的芯片,右键单击,选择Program Device...

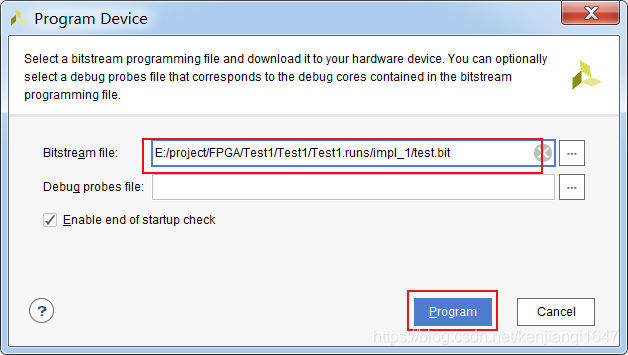

(2)添加bit文件的路径,点击Program

(3)下载成功,忽略警告