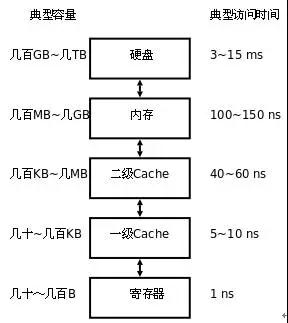

存储器是分层次的,离CPU越近的存储器,速度越快,每字节的成本越高,同时容量也因此越小。寄存器速度最快,离CPU最近,成本最高,所以个数容量有限,其次是高速缓存(缓存也是分级,有L1,L2等缓存),再次是主存(普通内存),再次是本地磁盘。

寄存器的速度最快,可以在一个时钟周期内访问,其次是高速缓存,可以在几个时钟周期内访问,普通内存可以在几十个或几百个时钟周期内访问。

存储器分级,利用的是局部性原理。我们可以以经典的阅读书籍为例。我在读的书,捧在手里(寄存器),我最近频繁阅读的书,放在书桌上(缓存),随时取来读。当然书桌上只能放有限几本书。我更多的书在书架上(内存)。如果书架上没有的书,就去图书馆(磁盘)。我要读的书如果手里没有,那么去书桌上找,如果书桌上没有,去书架上找,如果书架上没有去图书馆去找。可以对应寄存器没有,则从缓存中取,缓存中没有,则从内存中取到缓存,如果内存中没有,则先从磁盘读入内存,再读入缓存,再读入寄存器。

本系列的文章重点介绍缓存cache。了解如何获取cache的参数,了解缓存的组织结构,了解cache对程序的影响,了解如何利用cache提升性能。

本文作为系列文章的第一篇,讲述的如何获取cache的组成结构和如何获取cache的参数。

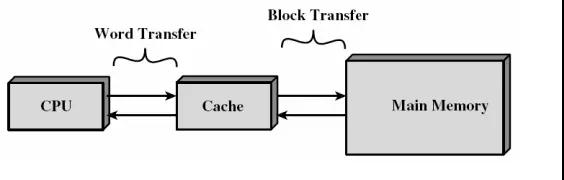

cache分成多个组,每个组分成多个行,linesize是cache的基本单位,从主存向cache迁移数据都是按照linesize为单位替换的。比如linesize为32Byte,那么迁移必须一次迁移32Byte到cache。 这个linesize比较容易理解,想想我们前面书的例子,我们从书架往书桌搬书必须以书为单位,肯定不能把书撕了以页为单位。书就是linesize。当然了现实生活中每本书页数不同,但是同个cache的linesize总是相同的。

所谓8路组相连( 8-way set associative)的含义是指,每个组里面有8个行。

我们知道,cache的容量要远远小于主存,主存和cache肯定不是一一对应的,那么主存中的地址和cache的映射关系是怎样的呢?

拿到一个地址,首先是映射到一个组里面去。如何映射?取内存地址的中间几位来映射。

举例来说,data cache: 32-KB, 8-way set associative, 64-byte line size表示Cache总大小为32KB,8路组相连(每组有8个line),每个line的大小linesize为64Byte,OK,我们可以很轻易的算出一共有32K/8/64=64 个组。

对于32位的内存地址,每个line有2^6 = 64Byte,所以地址的【0,5】区分line中的那个字节。一共有64个组。我们取内存地址中间6为来hash查找地址属于那个组。即内存地址的【6,11】位来确定属于64组的哪一个组。组确定了之后,【12,31】的内存地址与组中8个line挨个比对,如果【12,31】为与某个line一致,并且这个line为有效,那么缓存命中。

OK,cache分成三类:

- 直接映射高速缓存,这个简单,即每个组只有一个line,选中组之后不需要和组中的每个line比对,因为只有一个line。

- 组相联高速缓存,这个就是我们前面介绍的cache。 S个组,每个组E个line。

- 全相联高速缓存,这个简单,只有一个组,就是全相联。不用hash来确定组,直接挨个比对高位地址,来确定是否命中。可以想见这种方式不适合大的缓存。想想看,如果4M 的大缓存

描述一个cache需要以下参数:

- cache分级,L1 cache, L2 cache, L3 cache,级别越低,离cpu越近

- cache的容量

- cache的linesize

- cache 每组的行个数.

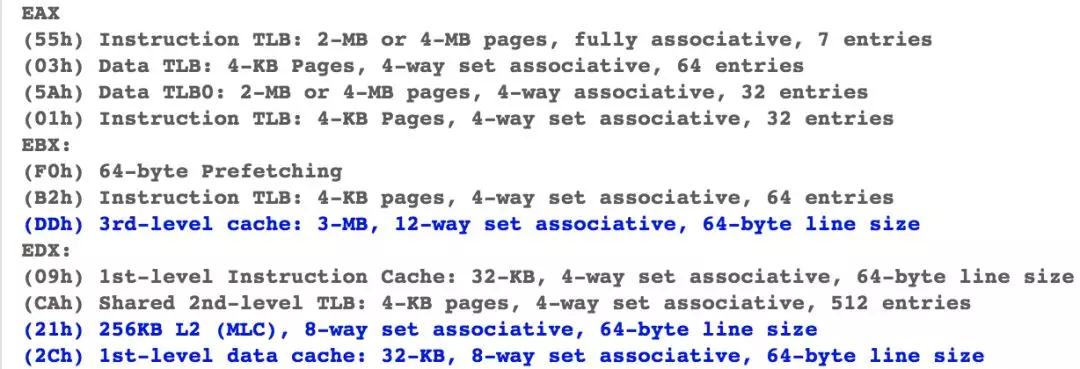

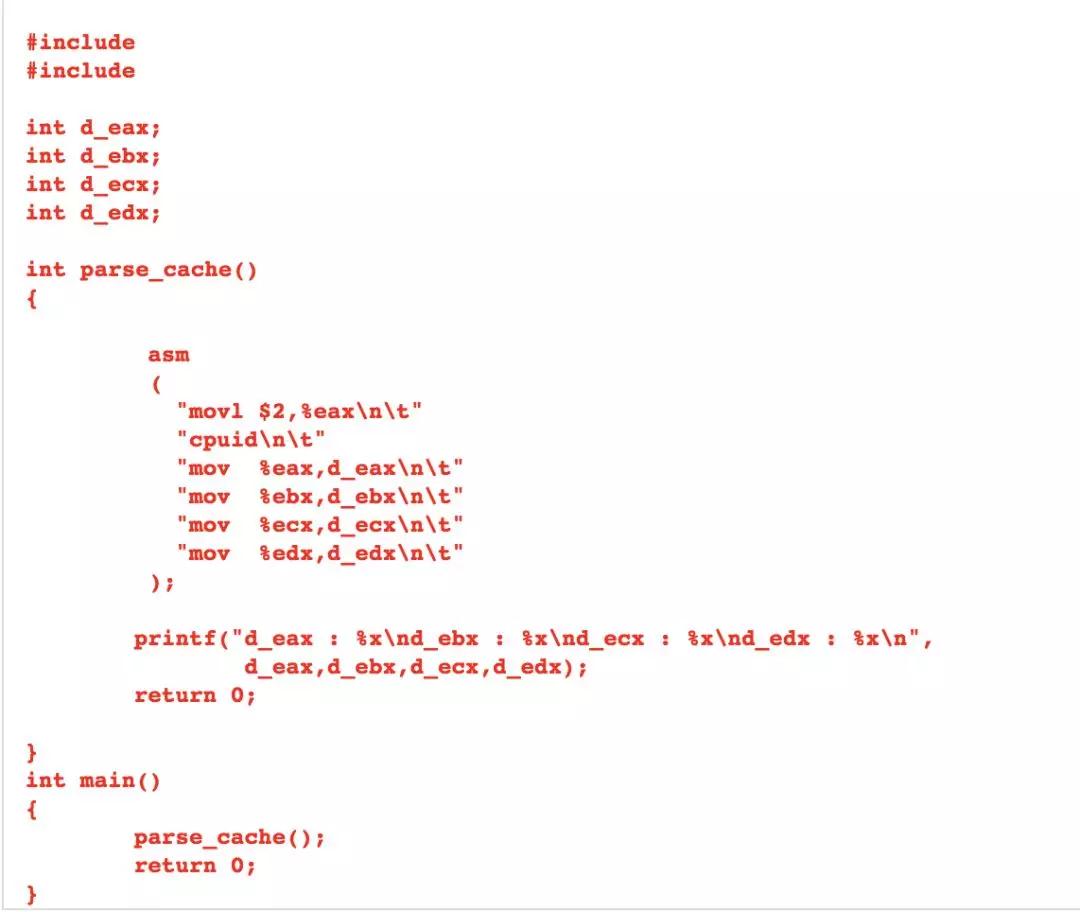

组的个数完全可以根据上面的参数计算出来,所以没有列出来.Intel手册中用这样的句子来描述cache:8-MB L3 Cache, 16-way set associative, 64-byte line size ,如何获取cache的参数呢,到了我们的老朋友cpuid指令,当eax为0x2的时候,cpuid指令获取到cache的参数. 下面给出代码:

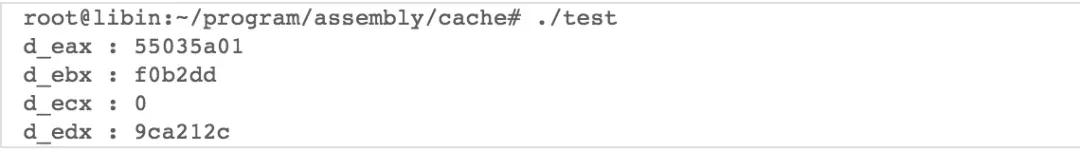

我的电脑上运行结果如上图,查看intel的手册可知