讲解内容:

时钟系统框图

时钟配置相关函数

参考资料 《STM32F4开发指南库函数版本》4.3小节STM32F4时钟系统

《STM32F4中文参考手册》第六章 复位和时钟系统

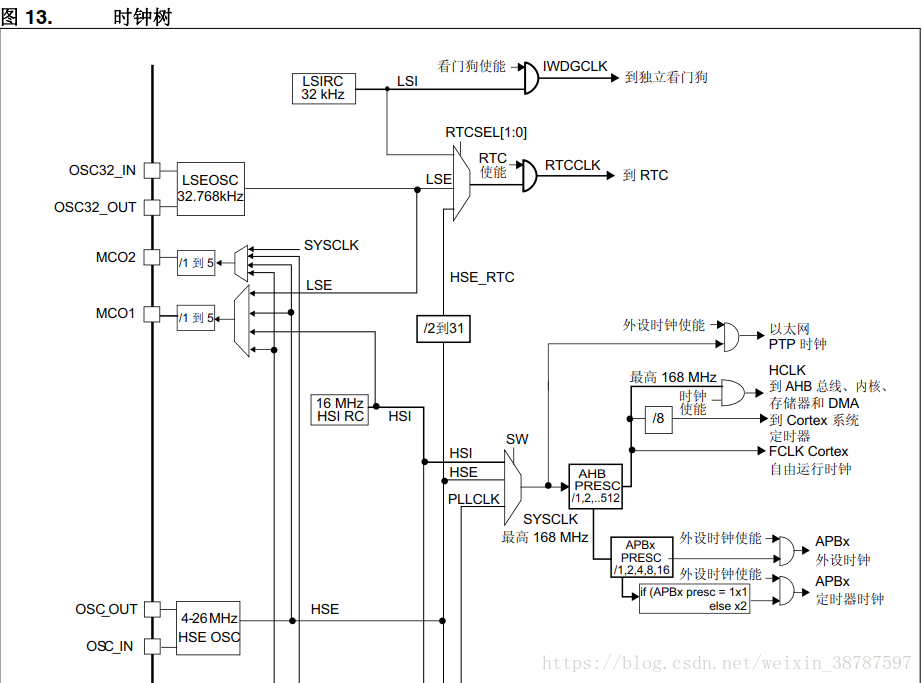

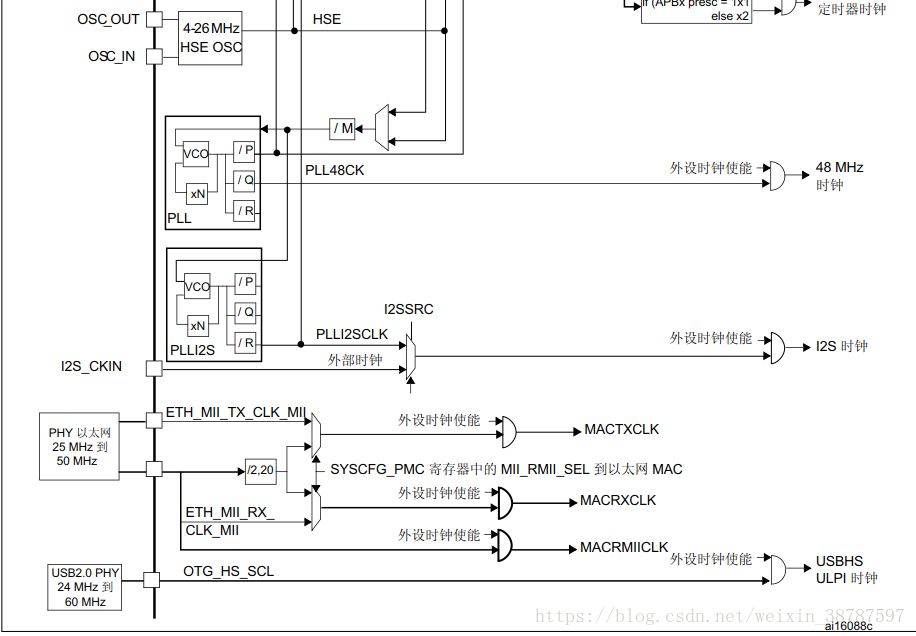

先看开发指南4.3小节的时钟树 时钟框图在中文参考手册的6.2小节,STM32的时钟系统还是很复杂的,为什么ARM的时钟系统要做的这么复杂,采用 多时钟源, 时钟频率越高功耗 越高。

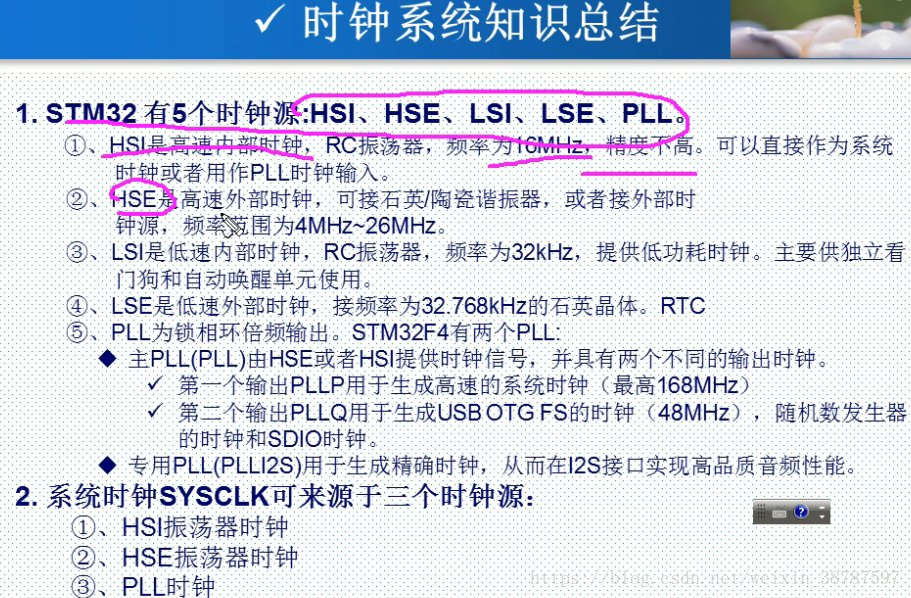

F4与F1类似也有5个时钟来源

1 LSIRC 低速 的内部时钟

2 LSEOSC 低速的外部时钟

3 HSIRC 高速的内部时钟

4 PLLCLK 锁相环时钟输出

5 HSEOSC 也是一个很重要的时钟源,也是我们最常用的

在讲解这5个时钟源之前,需要指出一个非常重要的时钟,叫系统时钟 SYSCLK,它是大部分的外设的时钟的直接或者间接来源

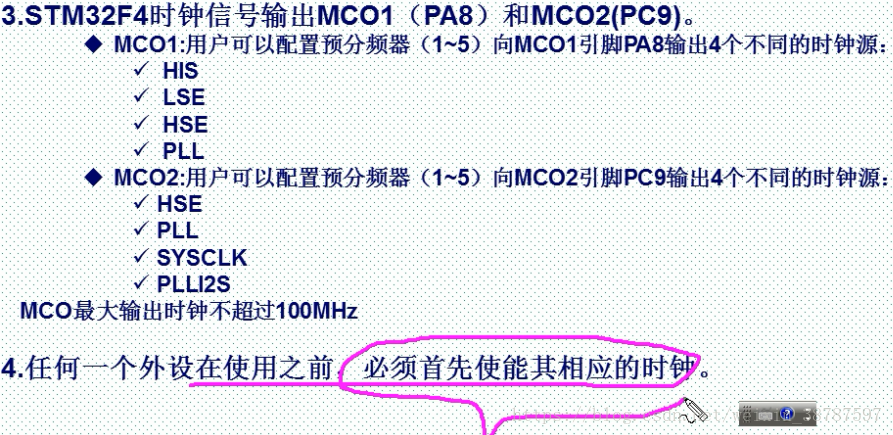

接下来我们会从LSIRC(低速的内部时钟)这里开始讲起,低速的内部时钟他的频率是32khz,它是由内部的RC 振荡器来产生的,由于是RC振荡器 产生的,所以他的频率不是很稳定,所以他的主要作用就是给独立看门狗作为时钟源(IWDGCLK), 所有的STM32外设在使用之前都要开启相应的外设时钟,比如,我们要使用这个看门狗就要先 使能看门狗的时钟使能位,下图中的梯形是 时钟选择器,同一个外设可以选择不同的时钟作为时钟源。LSEOSC是由我们在外部连接一个 精确的32.768kHz的晶振来产生的,晶振产生的频率他的稳定性就非常 的高,所以一般情况下RTC的时钟都是选择LSEOSC,RTC还有一个时钟源可以来自HSEOSC(高速的外部时钟)(外接晶振的范围4-26MHz),正点原子开发板接的是8Mhz,HSEOSC产生之后会经过一个分频器,从下图可以看到分频器的分频系数是2-31,分频之后的时钟才可以作为RTC的时钟。但是大部分情况下都是选择外部晶振LSEOSC 32.768kHz,MOCO1 (对应PA8) 和MCO2 (对应PC9) 对应两个引脚,可以将系统内部的时钟输出到这两个引脚,这里用户可以配置 预分频器(分频系数是1-5),向MCO1引脚PA8输出4个不同的时钟源,MCO2也有4个时钟源,通过分频器分频后将时钟输出到对应引脚

以MCO2为列有4种时钟源分别是 1、SYSCLK

2、PLLI2SCLK(这个是由PLLI2S这个锁相环产生的精确时钟)

3 HSEOSC(高速的外部时钟)

4 主PLL锁相环产生,是我们等下要讲解的重点

以MCO1为列有4种时钟源分别是 1、HSI

2、LSE

3 HSEOSC(高速的外部时钟)

4 主PLL锁相环产生,是我们等下要讲解的重点

特别注意 MCO最大输出时钟不超过100Mhz,也就说假如 系统时钟SYSCLK 是168MHz,那么它输出到MCO2就要让它进行分频,比如说我们分频2,那么分频之后就是84Mhz,如果你不分频那么这个时钟输出的频率会不准确

我们再来看一下HSI这个时钟源,他也是由内部RC振荡器产生的一个16Mhz的时钟,精度比不上外接晶振,它可以作为MCO1的时钟来源,它可以直接作为系统时钟的一个来源,往下可以作为PLL48CK上方这个选择器的输入,PLL48CK这个选择器还可以由HSE/HSI这两个时钟作为输入,比如说下图我们选择了HSE作为了PLL的时钟源输入,输入前有一个/M意思是:将HSE或者HSI除以一个M后产生一个时钟到主PLL(下图中上面的是主PLL,下面的是专用PLL),到VCO,到xN(xN意思就是倍频),xN之后就有3种选择: 1. /P 除以P,也就是经过一个P分频产生一个时钟 ,作为PLLCLK

2. /Q 除以Q,也就是产生PLL48CK时钟 ,是让USB模块来用的

3 /R 除以R,主PLL暂时没有使用到

上面的PLL它的主要作用是产生两种时钟,一种是作为系统时钟的时钟源,另外一种是产生PLL48CK,作为USB OTG的时钟

下面还有一个专用的PLL,专用的PLL他的时钟主要是给这个I2S这个模块来用的,由于I2S涉及到音质音量的问题,所以他对频率的要求非常高,所以这里就用到这个专用的PLL,对于这个专用的PLL他的时钟源的话实际上和主PLL是一样的,他的频率转化方法也和上面的主PLL一样,/R产生了I2S的时钟。回到前面/P产生了PLLCLK时钟后,供给系统时钟,从下图可以看出系统时钟有3种来源HSI、HSE、PLLCLK.

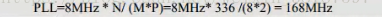

接下来我们来看一下PLLCLK时钟怎么来算,这个是我们的重点,假如说我们选择f(f是HSE 或者HSI)为主PLL的输入

那么就有: ((f/M)*N)/P 就输出了PLL的时钟,我们算PLLCLK:假如我们选择HSE(如果HSE是8MHz)

那么PLLCLK= ((8/M)*N)/P,使用固件库的话设置系统时钟为168Mhz,就是以PLLCLK作为系统时钟的时钟源,在开发指南库函数版本的手册

就是根据上面这个公式来的,外接晶振是8MHz,N(倍频系数设置为336),第一级的分频系数M设置为8,第二级的分频系数P设置为2,最后产生168Mhz的时钟频率。这个配置过程在Sysclockinit()这个函数有讲时钟配置过程。

下面就讲解右半部分:

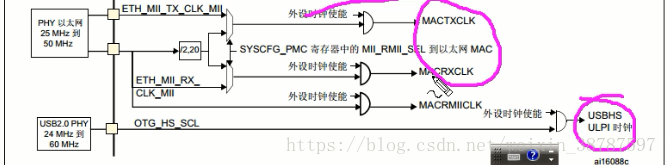

上图主要是以太网和USB的时钟,这里暂时不做介绍。

接下来看看右半部分,产生了系统时钟之后,可以直接作为以太网PHP时钟,还可以经过AHB预分频器,产生PCLK和HCLK,还可以由AHB经过APB这个预分频器,产生APB1或者APB2的这些时钟,这些就是供片上外设来使用,大家在用到相关的一些外设时可以去看一下相关库函数的配置,相关的宏定义就会有调用这些时钟,编程时遇到困难也可以看一下时钟树加深印象

下面我们随便打开一个程序看看有关系统时钟的定义:在stm32f4xx.h里面有关于RCC的结构体,其中常用的寄存器主要有

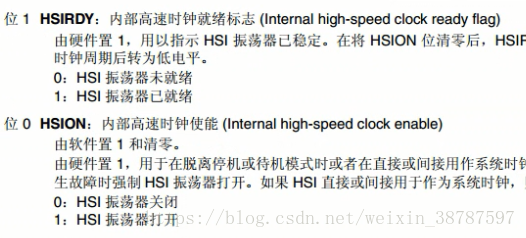

其中,CR寄存器主要是用作相关时钟源的使能,例如他的最低位是内部高速时钟使能,第二位是内部高速时钟使能就绪。因为我们在使用时钟源时必须使能相应的寄存器的相应位,这里我们以HSI为例。那么使用的顺序就是:

1.打开时钟源 ,也就是使能

2当我们要配置HSI作为系统时钟,要等待它稳定之后才能作为系统时钟(等待它就绪)

所以CR寄存器的作用就是去使能一些时钟,并等待时钟就绪

下面介绍RCC_PLLCFGR 主要用于配置PLL锁相环的P\Q\R\M这些值

还有一个RCC_CFGR寄存器主要是设置一些分频系数,还有一些时钟源的选择

下面这5个主要用于外设时钟使能

而时钟的配置过程主要在下面这几个寄存器

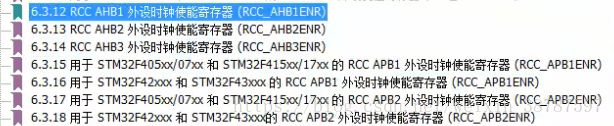

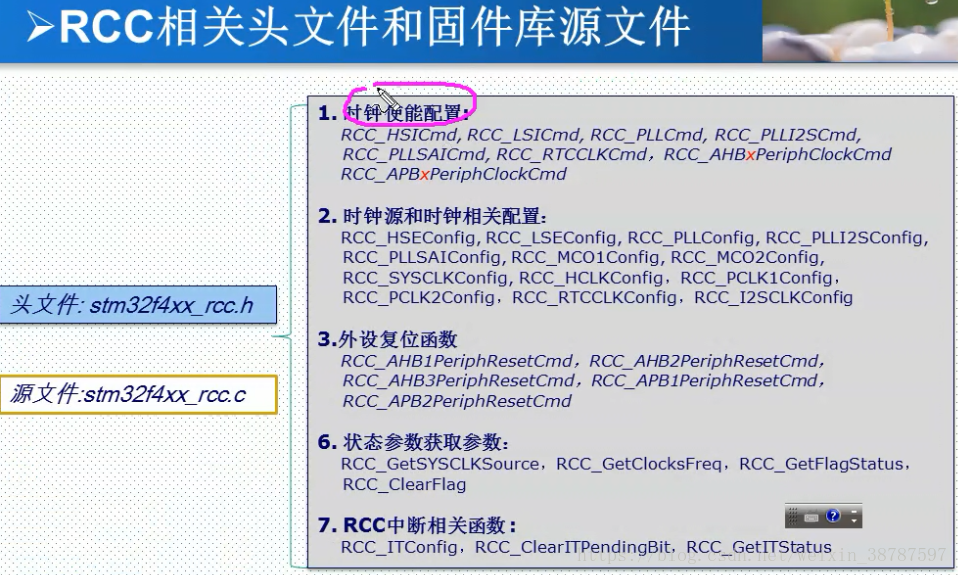

下面是RCC相关函数的分类:

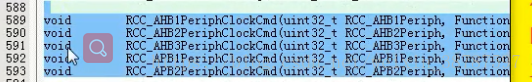

下面这5个函数是我们经常用的外设时钟使能函数

对用上面这些函数除了外设时钟使能函数之外,其他函数恨少能够用到,因为ST官方提供了一个固件库函数,他就通过直接配置库函数去做了系统初始化,如果大家在写自己的一些系统初始化函数的时候,要用到一些寄存器的话,可以去上面这些地方找,去调用这些函数去配置,这样会好一点。