1、什么是ISSP?ISSP有什么用?

Quartus II提供了In-System Sources and Probes Editor调试工具,通过JTAG接口使用该工具可以驱动和采样内部节点的逻辑值。即通过 Sources功能来驱动fpga内部信号,通过Probes功能来探测内部节点的逻辑值。在系统设计还不完整的时候可以利用该工具模拟众多的输入激励。比如,可以通过该IP核来实时修改内部某些寄存器的值,而不用重新修改代码,再全编译,再下载调试。

通俗来说,使用ISSP IP核可以对被测模块提供输入,而这个输入是可以在线更改的;同时,还可以检测被测模块的输出值(作用类似Signaltap)。

2、ISSP的使用

在数码管的静态显示章节(FPGA极易入门教程----数码管篇(1)静态显示)我们编写了动态驱动代码,并使用定时生成数据的方式对驱动代码进行了测试。这种测试方式的覆盖率高,但是不够灵活。我们如果使用ISSP IP核来测试就可以直接在线修改输入,起到特定的调试作用。

1、先新建一个工程issp_test

2、新建数码管驱动文件并将其添加到工程

//6位8段式数码管静态显示驱动

//端口定义

module dis_sta_dri (

input sys_clk , //时钟信号

input sys_rst_n , //复位信号(低有效)

input [3:0] num, //数码管显示的十进制数

output reg [5:0] dis_sel, //数码管位选

output reg [6:0] dis_seg, //数码管段选

output dis_dp //数码管小数点

);

assign dis_dp = 1'b1; //小数点,我们暂时不同,使其无效即可

//控制数码管位选信号(低电平有效),选中所有的数码管

always @ (posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

dis_sel <= 6'b111111; //复位熄灭所有数码管

else

dis_sel <= 6'b000000; //复位完成后给所有数码管供电

end

//根据数码管显示的数值,控制段选信号(低电平有效)

always @ (posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

dis_seg <= 7'b111_1111; //复位时熄灭数码管(这一条用处不大,因为复位时数码管也不供电)

else begin

case (num)

4'h0 : dis_seg <= 7'b000_0001; //显示数字“0”,则数码管的段选编码为7'b000_0001

4'h1 : dis_seg <= 7'b100_1111;

4'h2 : dis_seg <= 7'b001_0010;

4'h3 : dis_seg <= 7'b000_0110;

4'h4 : dis_seg <= 7'b100_1100;

4'h5 : dis_seg <= 7'b010_0100;

4'h6 : dis_seg <= 7'b010_0000;

4'h7 : dis_seg <= 7'b000_1111;

4'h8 : dis_seg <= 7'b000_0000;

4'h9 : dis_seg <= 7'b000_0100; //显示数字“9”,则数码管的段选编码为7'b000_0100

default : dis_seg <= 7'b111_1111; //其他数字(16进制的数字相对10进制无效)则熄灭数码管

endcase

end

end

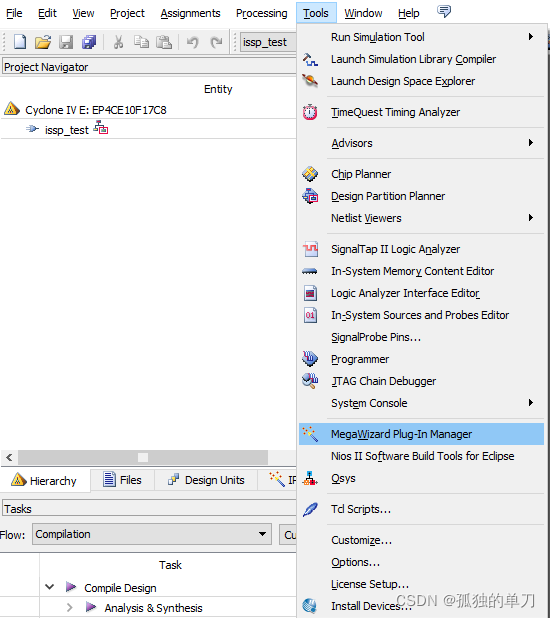

endmodule3、进入IP选择界面

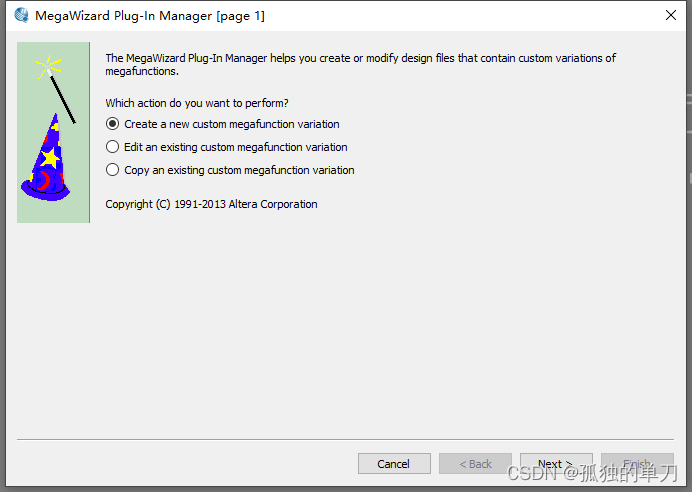

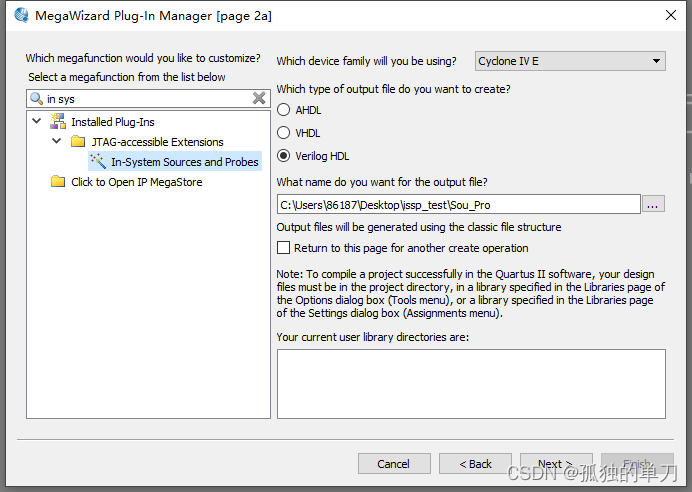

4、例化In-System Sources and Probes Editor IP核,名(随便取)为Sou_Pro ,点击 Next进入 IP参数设置界面。

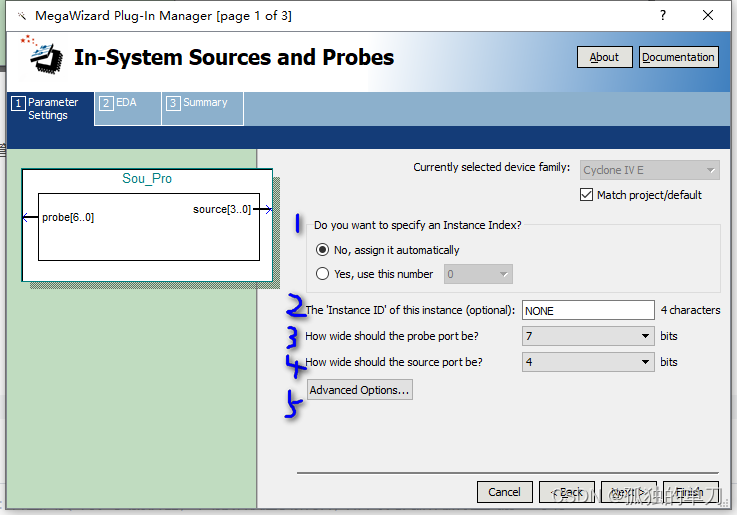

5、按以下设置IP参数

(1)选择是否指定例化IP的编号,默认设置,不用修改

(2)是否设置IP核的ID号。因为在一个工程中,可以例化多个In-System Sources and Probes Editor IP核,该ID号就是用来区分不同的IP核

(3)用来设置探测(Probes)端口,probe功能我们用来检测数码管的段选值,以此验证输入数值是否能有对应的正确输出,位宽设置为7,

(4)用来设置驱动(Sources)端口,source位宽设为20(注意图片不一致),与数码管驱动数字的位宽一致

(5)高级设置选项。可以用来设置驱动 信号的初始值以及发送驱动信号是否与源时钟同步。(通常保持默认即可)

6、一直点next直到finish,完成IP的创建。

7、编写顶层文件并将其添加到工程,例化数码管驱动和ISSP IP核,如下:

//ISSP IP 测试文件

module issp_test(

input sys_clk , //时钟信号

input sys_rst_n , //复位信号(低有效)

output [5:0] dis_sel , //数码管位选

output [6:0] dis_seg , //数码管段选

output dis_dp //数码管小数点

);

wire [3:0] num; //数码管显示的十进制数,10进制,范围0-9

//例化数码管驱动

dis_sta_dri dis_sta_dri_inst(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.num (num ),

.dis_sel (dis_sel ),

.dis_seg (dis_seg ),

.dis_dp (dis_dp )

);

//例化ISSP IP核

Sou_Pro Sou_Pro_inst (

.probe (dis_seg ), //探测数码管段选

.source (num ) //生成数码管显示数据

);

endmodule8、全编译工程,并将生成的文件下载到FPGA

至此就完成了IP核的创建,接下来就使用在线调试工具对被测模块进行调试。

3、测试过程与结果

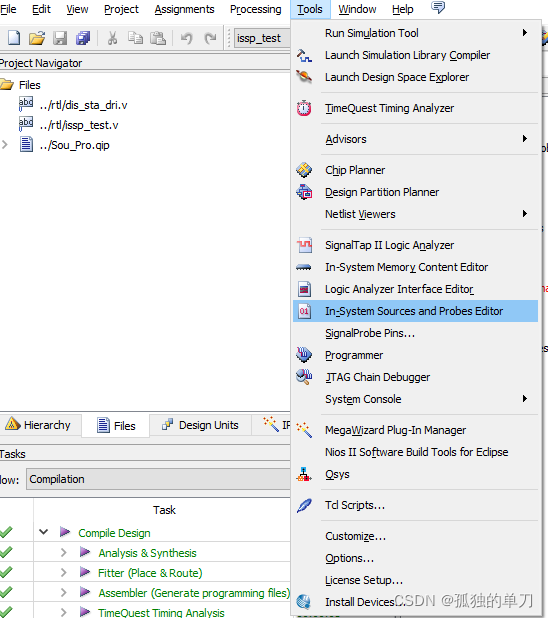

1、打开在线调试工具,如下:

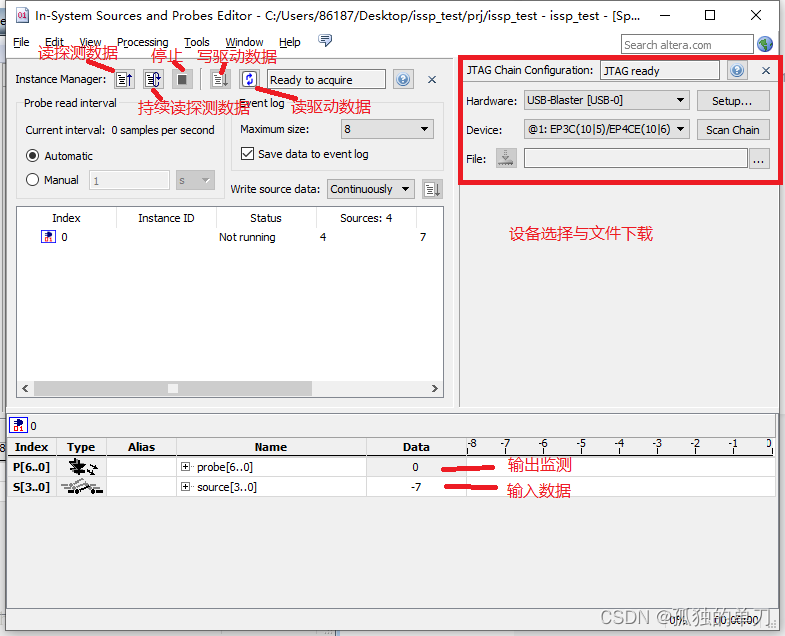

2、窗口右边选择自己的JTAG接口

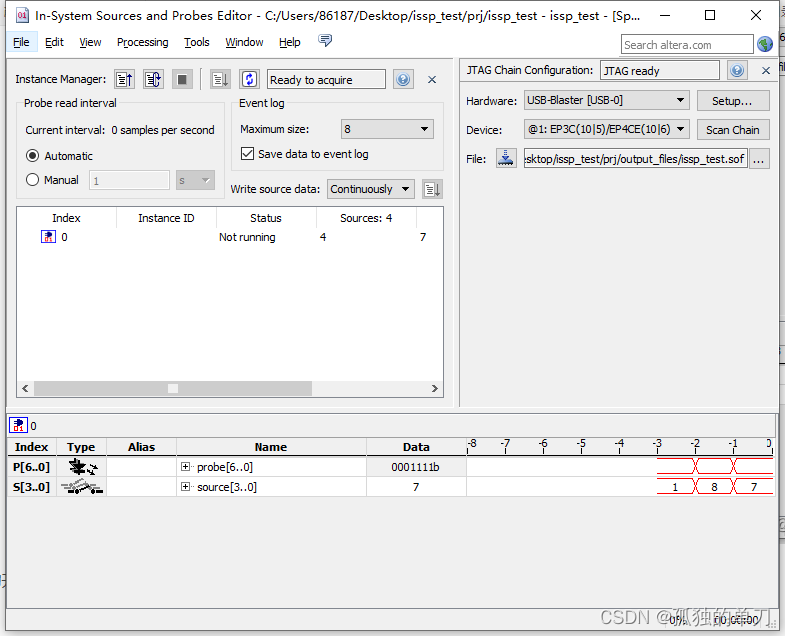

3、界面如下:

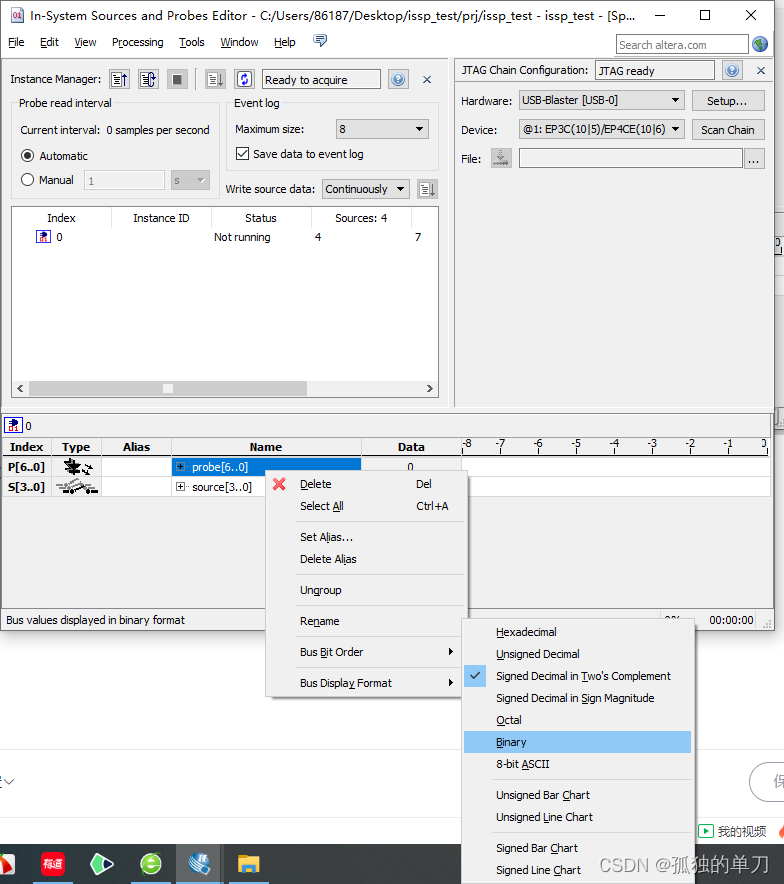

4、右击probe和source,可以选择数据的进制,分别将 probe设置为2进制,将source设置为10进制

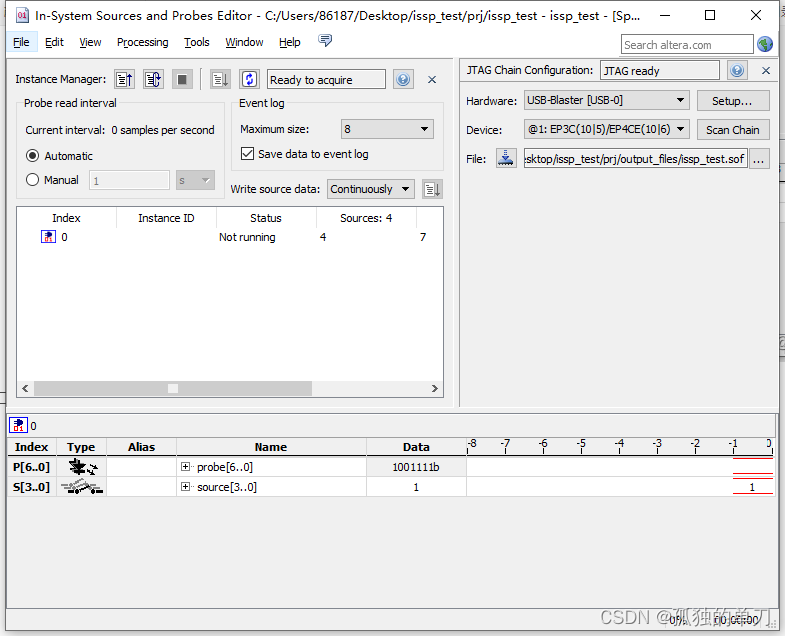

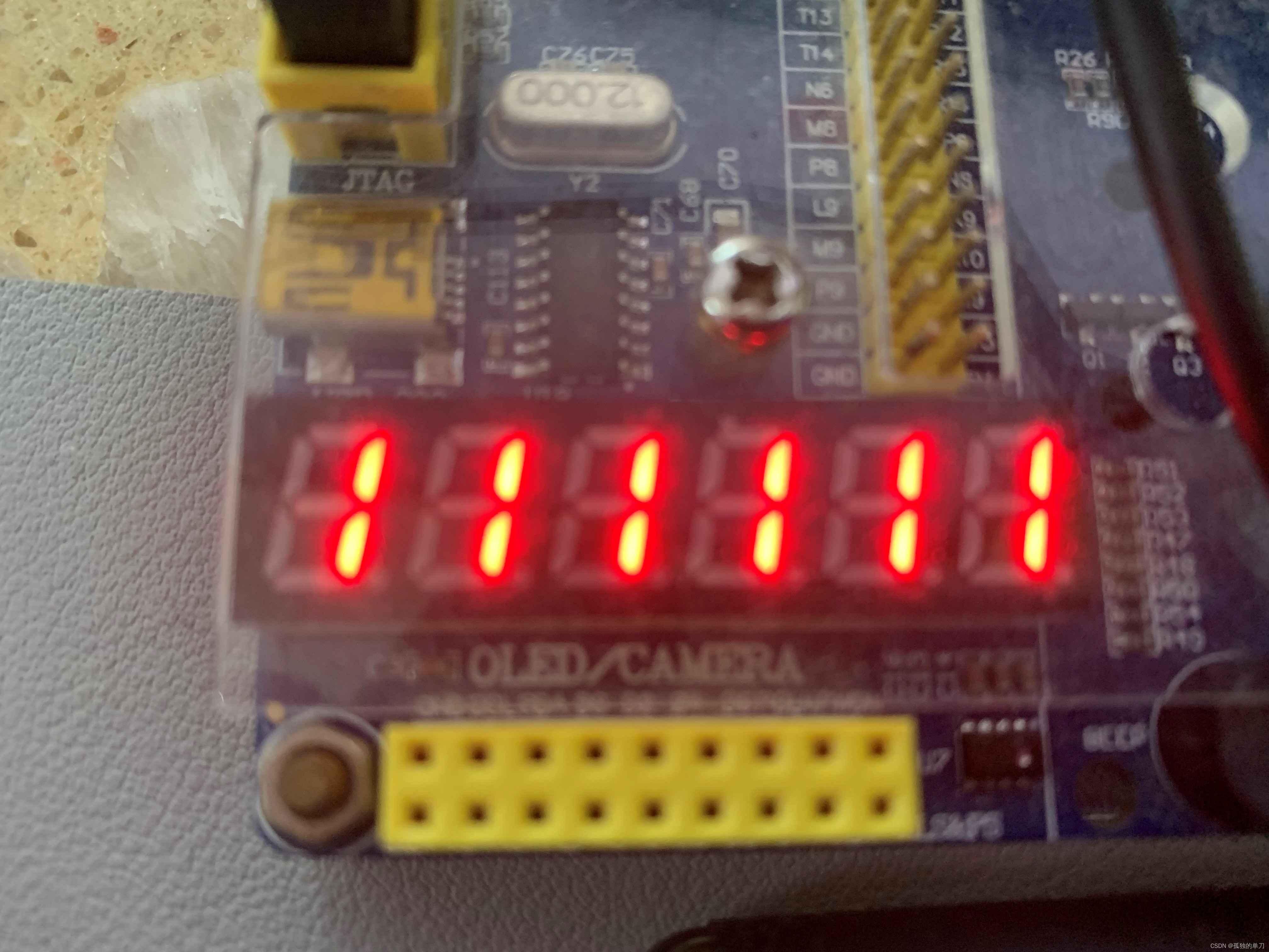

5、我们在source窗口输入1,然后读取探测数据,此时读到的数码管段选值为10011111,与预计一致

同时发现我们的开发板上的数码管显示111111,与预计一致

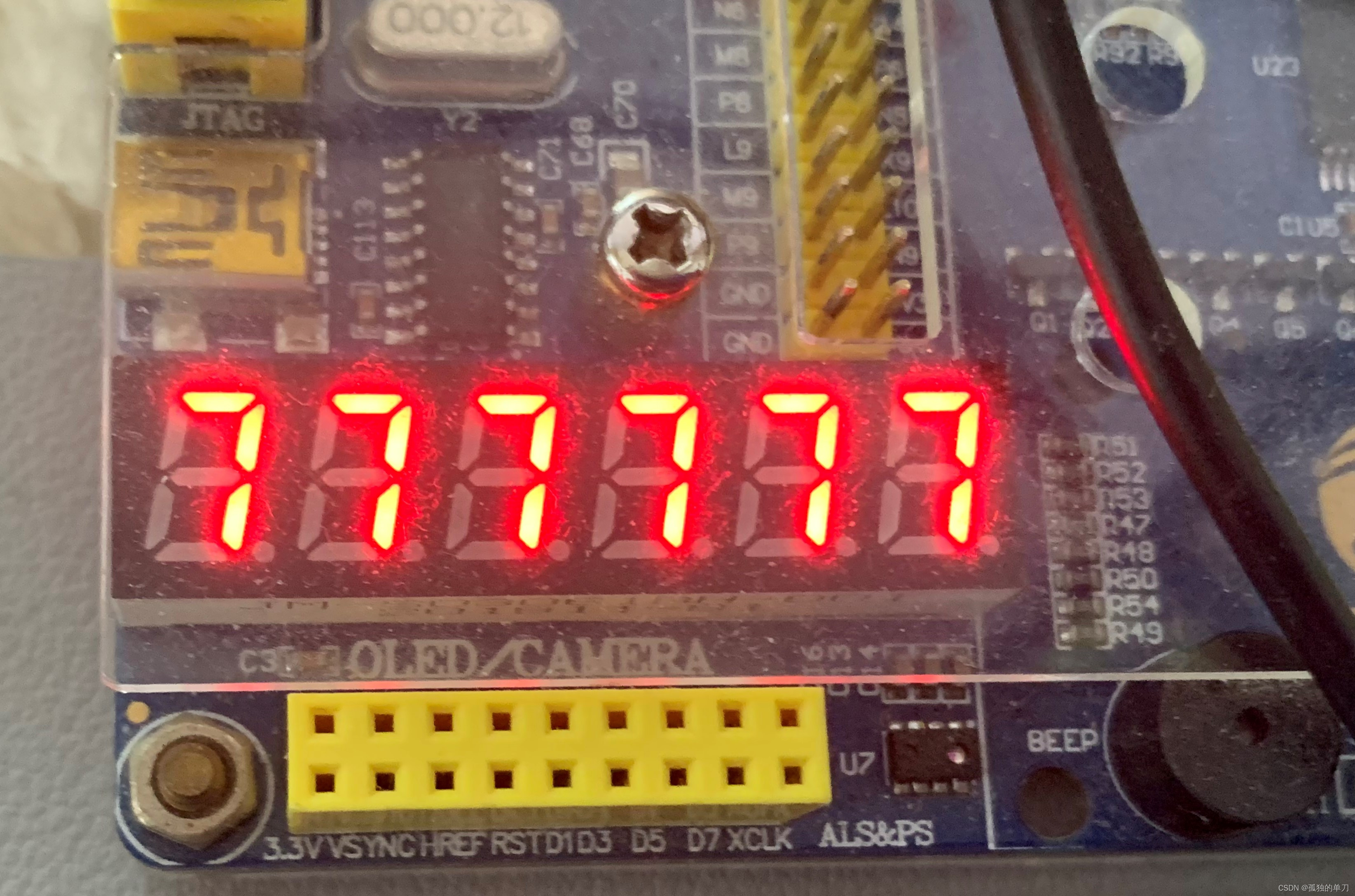

6、我们在source窗口输入7,然后读取探测数据,此时读到的数码管段选值为00011111,与预计一致

同时发现我们的开发板上的数码管显示777777,与预计一致

4、其他

- 创作不易,如果本文对您有帮助,还请多多点赞、评论和收藏。您的支持是我持续更新的最大动力!

- 关于本文,您有什么想法均可在评论区留言。如果需要整个工程,请在评论留下邮箱或者私信我邮箱(注意保护隐私)。

- 自身能力不足,如有错误还请多多指出!

版本信息

文件:V1.0

编号:0003

Quartus II:Quartus II 13.1 (64-bit)