一、硬件描述语言

硬件描述语言(HDL)是电子系统硬件行为描述、结构描述、数据流描述的语言。利用这种语言,数字电路系统的设计可以从顶层到底层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后,利用电子设计自动化( EDA )工具,逐层进行仿真验证,再把其中需要变为实际电路的模块组合,经过自动综合工具转换到门级电路网表。接下去,再用专用集成电路 ASIC 或现场可编程门阵列 FPGA 自动布局布线工具,把网表转换为要实现的具体电路布线结构,VHDL 和 Verilog HDL 语言适应了这种趋势的要求,先后成为 IEEE 标准。

2.选择哪种硬件描述语言?

建议选择:Verilog HDL

原因:

- Verilog HDL 推出已经有 20 年了,拥有广泛的设计群体,成熟的资源也比 VHDL 丰富,Verilog HDL未来发展趋势。

- 它非常容易掌握,只要有 C 语言的编程基础,通过比较短的时间,经过一些实际的操作,可以在 2 ~ 3 个月内掌握这种设计技术。

- 在中国很多集成电路设计公司都采用Verilog,一般大型项目采用VHDL。

二、基础知识

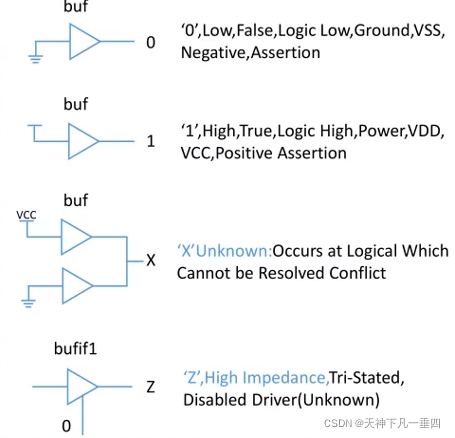

1.逻辑值:

- 逻辑0:表示低电平,也就对应我们的电路GND

- 逻辑1:表示高电平,也就对应我们电路的VCC

- 逻辑X:表示未知,有可能是高电平,也有可能是低电平

- 逻辑Z:·表示高阻态,外部没有激励信号(输入信号),是一个悬空状态(未接高低电平)

2.数字进制格式:

Verilog数字进制格式包括二进制(b)、八进制(o)、十进制(d)和十六进制(h)。

一般常用的为二进制、十进制和十六进制。

二进制表示如下:4’b0101表示4位二进制数字0101

十进制表示如下:4’d2表示4位十进制数字2(二进制0010)

十六进制表示如下:4’ha表示4位十六进制数字a(二进制1010)

注意:如果未表明位宽和进制则:默认为32位宽的十进制数字(32’d)

常见写法:16’b1001_1010_1010_1001=16’h9AA9

3.标识符(变量名):

标识符:用于定义模块名、端口名、信号名等(就是起个名字而已)。

标识符可以是任意一组字母、数字、$和_(下划线)符号的组合

但标识符不允许以数字开头

标识符严格区分大小写

不建议大小写混合使用

普通内部信号建议全部小写

命名最好体现信号的含义,简介、清晰、易懂(见名知意)

如: 1.有意义的标识符:sum

2.用下划线区分词:cpu_addr

3.采用一些前缀或后缀:时钟clk_50或sys_clk