一. FSMC简介

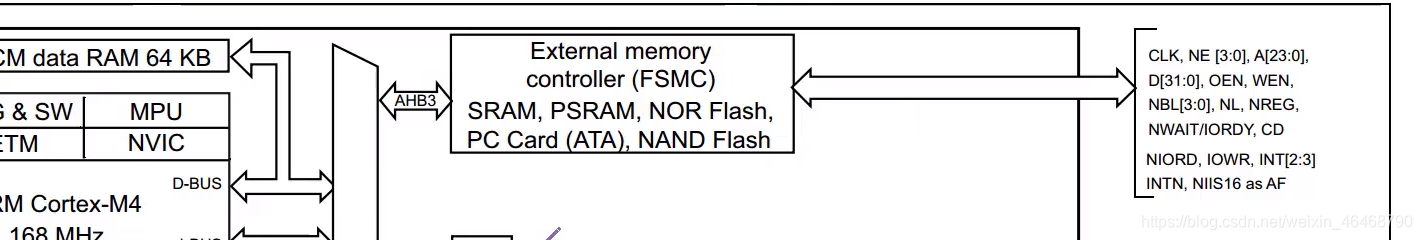

名称:FSMC ,即为 Flexible Static Memory Controller 的缩写,译为灵活的静态存储控制器。它可以用于驱动包括 SRAM、NOR FLASH 以及NAND FLSAH 类型的存储器。

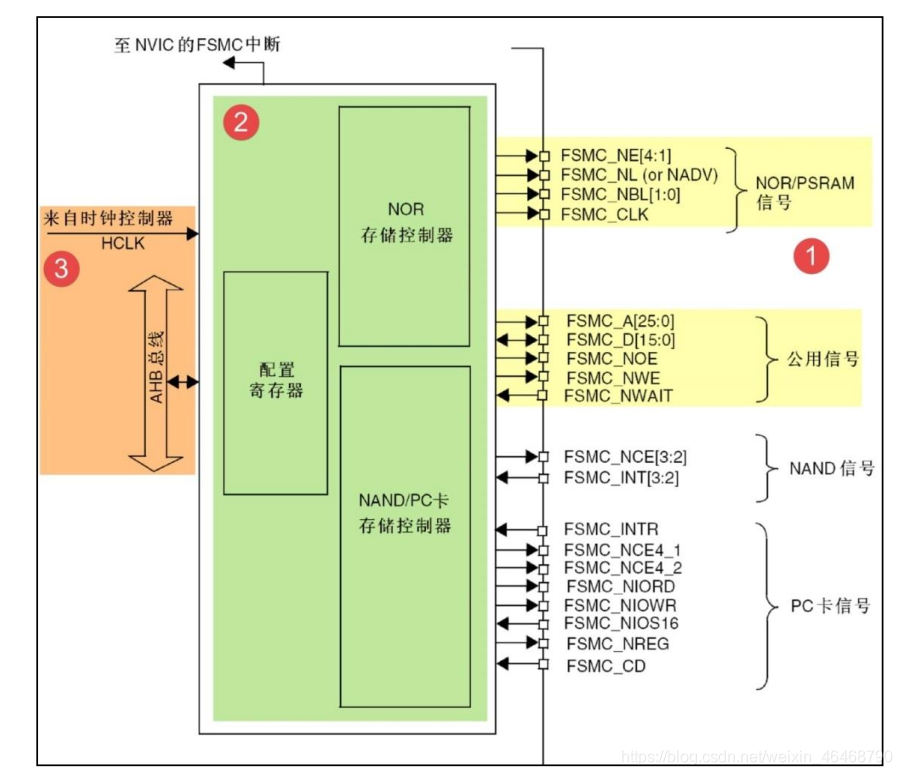

二 . 结构框图

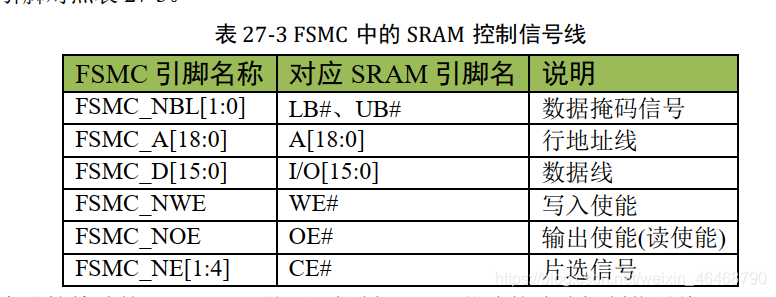

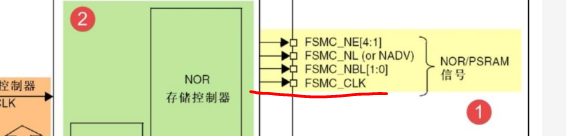

2.1 FSCM相关通讯引脚

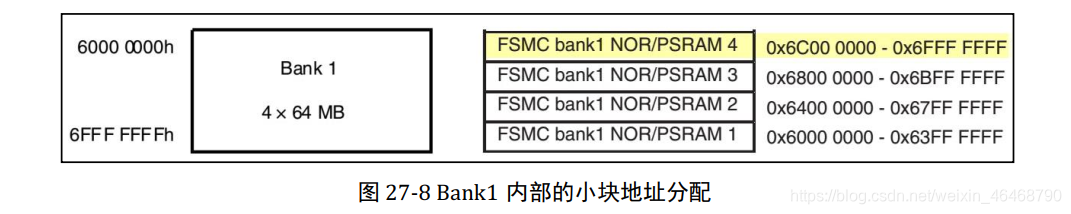

其中FSMC_NE[1:4]引脚有四根,对应STM32内部不同的存储区域。例如,当 STM32访问 0x6C000000-0x6FFFFFFF 地址空间时,FSMC_NE3 引脚会自动设置为低电平,由于它连接到 SRAM 的 CE#引脚,所以 SRAM 的片选被使能,而访问 0x60000000-0x63FFFFFF

地址时, FSMC_NE1 会输出低电平。

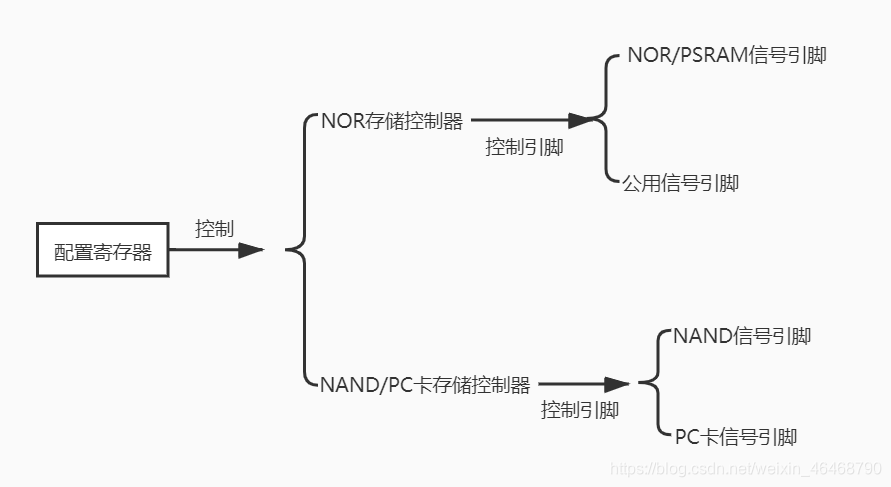

2.2 存储控制器

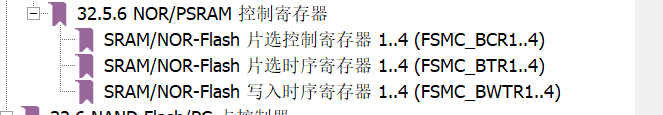

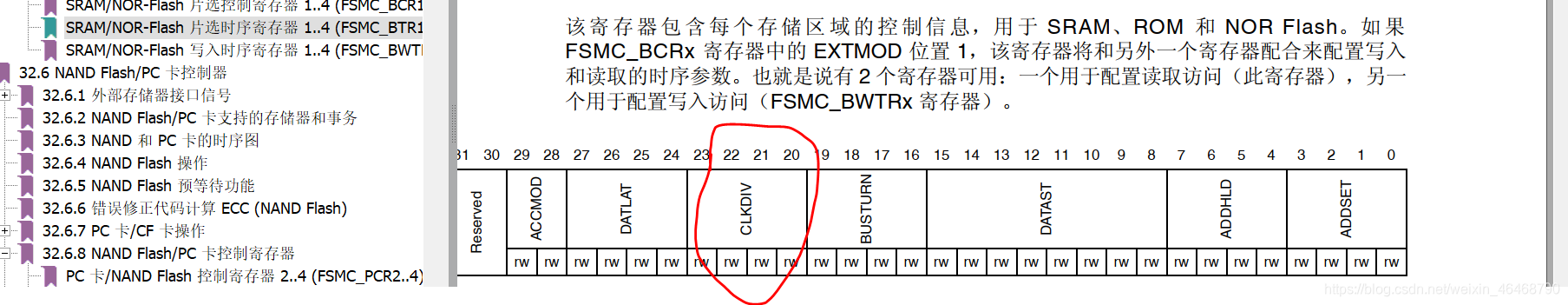

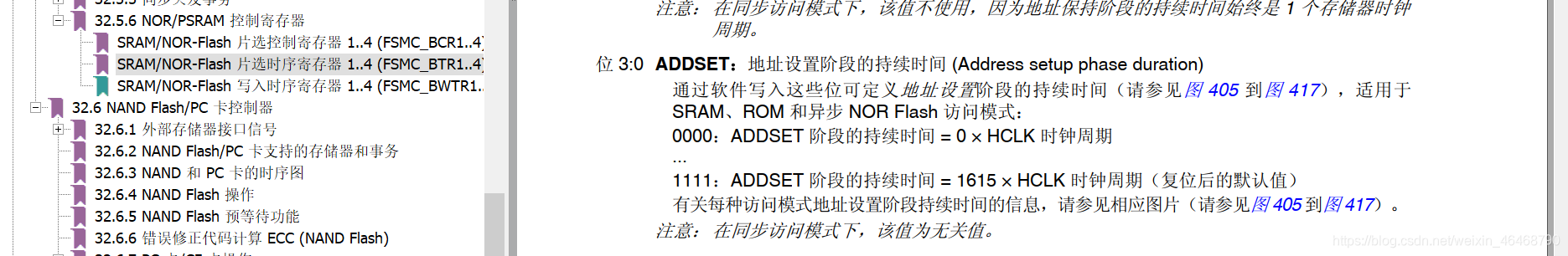

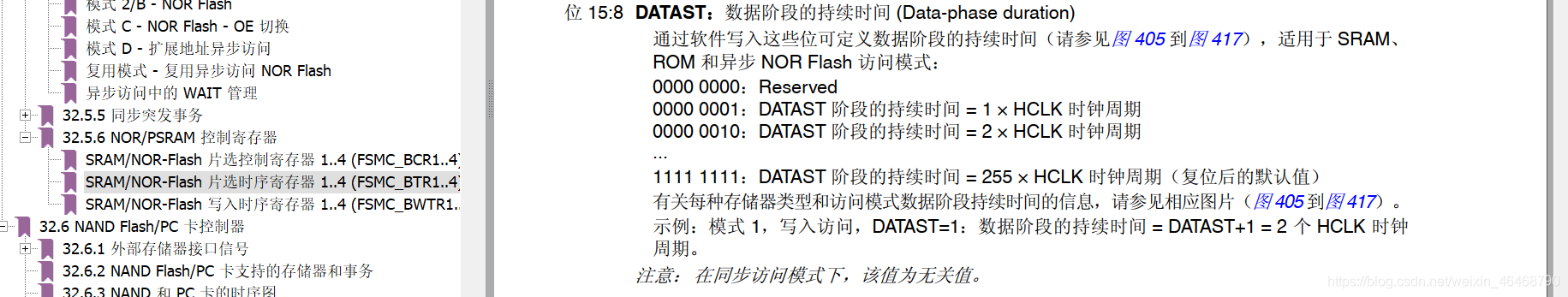

2.2.1 NOR/PSRAM控制寄存器

控制 SRAM 的有 FSMC_BCR1/2/3/4 控制寄存器、FSMC_BTR1/2/3/4 片选时序寄存器以及 FSMC_BWTR1/2/3/4 写时序寄存器。每种寄存器都有 4 个,分别对应于 4 个不同的存储区域,各种寄存器介绍如下:

FSMC_BCR 控制寄存器可配置要控制的存储器类型、数据线宽度以及信号有效极性能参数。

FMC_BTR 时序寄存器用于配置 SRAM 访问时的各种时间延迟,如数据保持时间、地址保持时间等。

FMC_BWTR 写时序寄存器与 FMC_BTR 寄存器控制的参数类似,它专门用于控制写时序的时间参数。写时序寄存器的目的在于在需要读时序与写时序不一致时,可以通过FMC_BTR控制读的相关时间延迟,而用FMC_BWTR专门控制写的各种时间延迟。

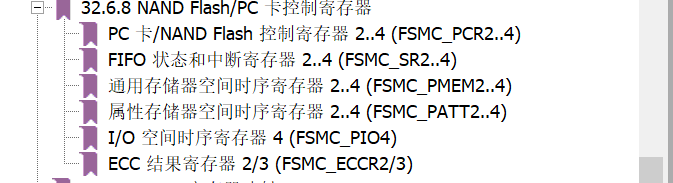

2.2.2 NAND Flash/PC卡控制寄存器

2.3 时钟控制器

FSCM直接挂在最高的时钟总线AHB3下,因为FSCM对速度要求很高。时钟信号来自于 HCLK(默认 168MHz),控制器的同

步时钟输出就是由它分频得到。

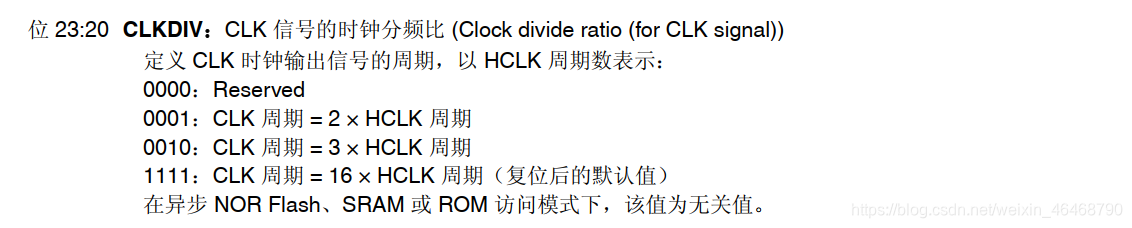

上图中的FSMC_CLK可以控制同步时钟频率,可通过 FSMC_BTR 寄存器的CLKDIV 位配置,可以配置为 HCLK 的 1/2 或 1/3,也就是说,若它与同步类型的 SRAM通讯时,同步时钟最高频率为 84MHz。

三. FSCM寄存器映射

3.1 寄存器映射概念:使用 FSMC 外接存储器时,其存储单元是映射到 STM32 的内部寻址空间的;在程序里,定义一个指向这些地址的指针,然后就可以通过指针直接修改该存储单元的内容, FSMC 外设会自动完成数据访问过程,读写命令之类的操作不需要程序控制。(相当于就是把取指针的过程给你做了)。

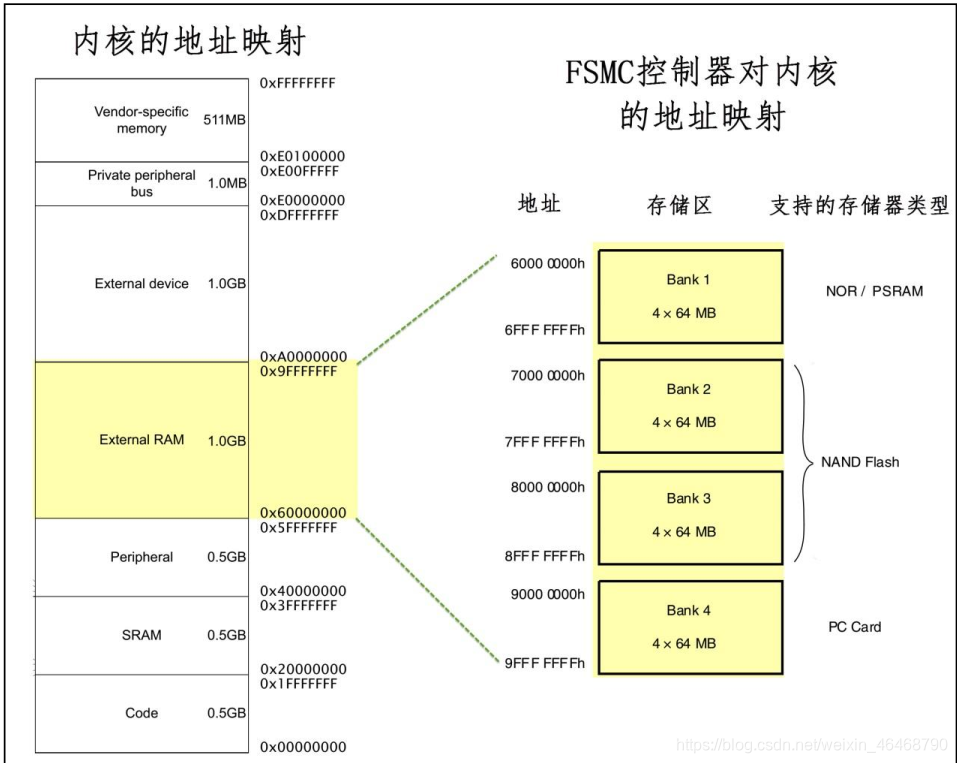

3.2 FSMC把外部RAM分成四个BANK,每个BANK又分成四个部分。

每个部分有相应的控制引脚用于连接片选信号,如 FSMC_NE[4:1]信

号线可用于选择 BANK1 内部的 4 小块地址区域。

例如:当当 STM32 访问 0x6C000000-0x6FFFFFFF 地址空间时,会访问到 Bank1 的第 3 小块区域,相应的 FSMC_NE3 信号线会输出控制信号。

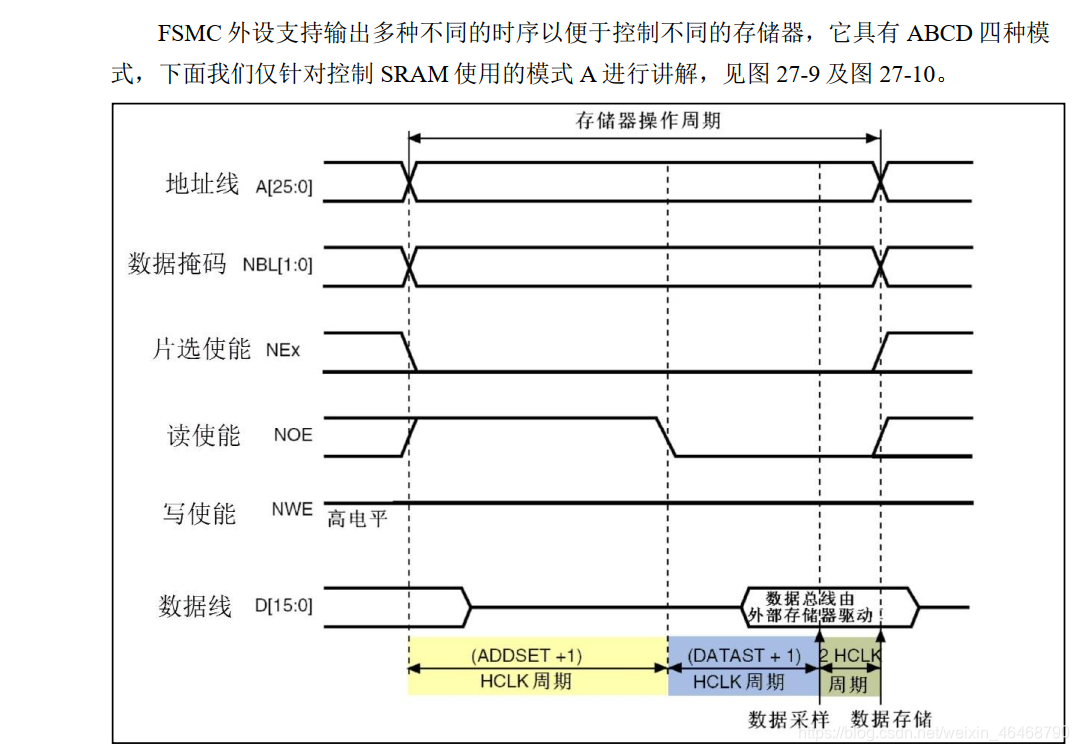

四. FSCM控制SRAM时序

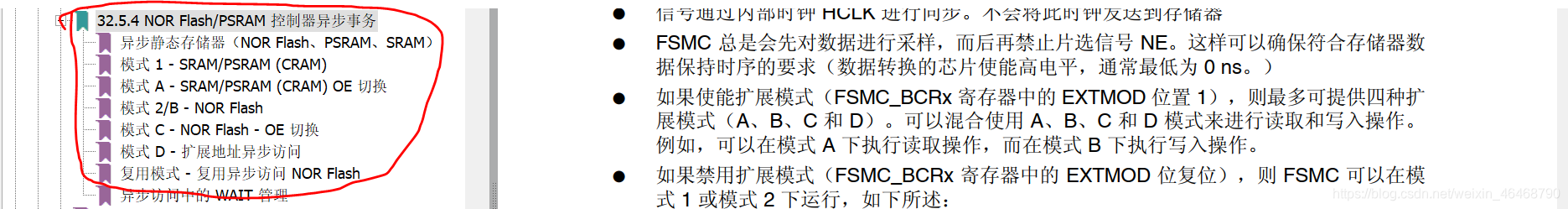

4.1 SARM四种控制模式

举例:对于SARM模式A

ADDSET配置:

DATAST 配置:

五. SRAM时序结构体与初始化结构体

5.1 SRAM时序结构体

typedef struct

{

uint32_t FSMC_AddressSetupTime; /*地址建立时间, 0-0xF 个 HCLK 周期*/

uint32_t FSMC_AddressHoldTime; /*地址保持时间, 0-0xF 个 HCLK 周期*/

uint32_t FSMC_DataSetupTime; /*地址建立时间, 0-0xF 个 HCLK 周期*/

uint32_t FSMC_BusTurnAroundDuration; /*总线转换周期,0-0xF 个 HCLK 周期,在 NOR FLASH */

uint32_t FSMC_CLKDivision; /*时钟分频因子,1-0xF,若控制异步存储器,本参数无效 */

uint32_t FSMC_DataLatency; /*数据延迟时间,若控制异步存储器,本参数无效 */

uint32_t FSMC_AccessMode; /*设置访问模式 */

}FSMC_NORSRAMTimingInitTypeDef;

5.2 SRAM 初始化结构体

typedef struct

{

uint32_t FSMC_Bank; /*设置要控制的 Bank 区域 */ uint32_t FSMC_DataAddressMux; /*设置地址总线与数据总线是否复用 */

uint32_t FSMC_MemoryType; /*设置存储器的类型 */

uint32_t FSMC_MemoryDataWidth; /*设置存储器的数据宽度*/

uint32_t FSMC_BurstAccessMode; /*设置是否支持突发访问模式,只支持同步类型的存储器 */

uint32_t FSMC_AsynchronousWait; /*设置是否使能在同步传输时的等待信号, */

uint32_t FSMC_WaitSignalPolarity; /*设置等待信号的极性*/

uint32_t FSMC_WrapMode; /*设置是否支持对齐的突发模式 */

uint32_t FSMC_WaitSignalActive; /*配置等待信号在等待前有效还是等待期间有效 */

uint32_t FSMC_WriteOperation; /*设置是否写使能 */

uint32_t FSMC_WaitSignal; /*设置是否使能等待状态插入 */

uint32_t FSMC_ExtendedMode; /*设置是否使能扩展模式 */

uint32_t FSMC_WriteBurst; /*设置是否使能写突发操作*/

/*当不使用扩展模式时,本参数用于配置读写时序,否则用于配置读时序*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_ReadWriteTimingStruct;

/*当使用扩展模式时,本参数用于配置写时序*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_WriteTimingStruct;

}FSMC_NORSRAMInitTypeDef;

六. FSMC初始化结构体

typedef struct

{

uint32_t FSMC_Bank; /*设置要控制的 Bank 区域 */

uint32_t FSMC_DataAddressMux; /*设置地址总线与数据总线是否复用 */

uint32_t FSMC_MemoryType; /*设置存储器的类型 */

uint32_t FSMC_MemoryDataWidth; /*设置存储器的数据宽度*/

uint32_t FSMC_BurstAccessMode; /*设置是否支持突发访问模式,只支持同步类型的存储器 */

uint32_t FSMC_AsynchronousWait; /*设置是否使能在同步传输时的等待信号, */

uint32_t FSMC_WaitSignalPolarity; /*设置等待信号的极性*/

uint32_t FSMC_WrapMode; /*设置是否支持对齐的突发模式 */

uint32_t FSMC_WaitSignalActive; /*配置等待信号在等待前有效还是等待期间有效 */

uint32_t FSMC_WriteOperation; /*设置是否写使能 */

uint32_t FSMC_WaitSignal; /*设置是否使能等待状态插入 */

uint32_t FSMC_ExtendedMode; /*设置是否使能扩展模式 */

uint32_t FSMC_WriteBurst; /*设置是否使能写突发操作*/

/*当不使用扩展模式时,本参数用于配置读写时序,否则用于配置读时序*/ FSMC_NORSRAMTimingInitTypeDef*FSMC_ReadWriteTimingStruct;

/*当使用扩展模式时, 本参数用于配置写时序*/

FSMC_NORSRAMTimingInitTypeDef* FSMC_WriteTimingStruct;

}FSMC_NORSRAMInitTypeDef;

本文是参考野火视频讲解学习总结性文章