1. ESP32 芯片分类:

ESP32 目前有 6 种:

| 订购型号 | 内核 | 嵌入式 flash | 通信模式 | 封装 | 工作温度 |

|---|---|---|---|---|---|

| ESP32-D0WD-V3 | 双核 | 无嵌入式 flash | Wi-Fib/g/n + BT/BLE 双模 | QFN 5*5 | –40 °C ~ 125 °C |

| ESP32-D0WDQ6-V3 | 双核 | 无嵌入式 flash | Wi-Fib/g/n + BT/BLE 双模 | QFN 6*6 | –40 °C ~ 125 °C |

| ESP32-D0WD | 双核 | 无嵌入式 flash | Wi-Fib/g/n + BT/BLE 双模 | QFN 5*5 | –40 °C ~ 125 °C |

| ESP32-D0WDQ6 | 双核 | 无嵌入式 flash | Wi-Fib/g/n + BT/BLE 双模 | QFN 6*6 | –40 °C ~ 125 °C |

| ESP32-D2WD | 双核 | 16Mbit 嵌入式 flash(40MHz) | Wi-Fib/g/n + BT/BLE 双模 | QFN 5*5 | –40 °C ~ 105 °C |

| ESP32-S0WD | 单核 | 无嵌入式 flash | Wi-Fib/g/n + BT/BLE 双模 | QFN 5*5 | –40 °C ~ 125 °C |

V3 为最近乐鑫对旗下 ESP32 系列产品的晶圆级改进(ECO V3),主要变化如下:

- 修复 PSRAM Cache 问题: 修复了“CPU 以特定顺序访问外部 SRAM 时读写异常” 的问题

- 修复 “双核 CPU 在读不同地址空间时可能发生读错误” 的问题

- 针对客户 “ECO V1 硬件配置下, 32.768KHz 晶振小概率无法正常启动”的问题,优化外部 32.768KHz 晶振的稳定性

- 修复有关 “安全启动” 和 “闪存加密” 的故障注入问题

- 优化:CAN 模块支持的最低带宽从 25KHz 放宽至 12.5KHz

2. 管脚功能

ESP32管脚配置非常灵活,截图自 Datasheet 如下:

但仍然有几个比较特殊的功能需要特定的管脚,如下:

- ESP32-D2WD 中的内置 flash 端口与芯片管脚对应关系是:CS# = GPIO16,IO1/DO = GPIO17,IO3/HOLD# = SD_CMD,CLK = SD_CLK,IO2/WP# = SD_DATA_0,IO0/DI = SD_DATA_1。芯片的这几个管脚不建议用于其他功能

- 除 ESP32-D2WD 的其他 ESP32 芯片和外接 flash 的数据端口连接关系是:SD_DATA0/SPIQ = IO1/DO,SD_DATA1/SPID = IO0/DI,SD_DATA2/SPIHD = IO3/HOLD#,SD_DATA3/SPIWP = IO2/WP#

-

GPI34 ~ GPI39 只能作为输入功能;

-

推荐使用 ADC1,建议靠近 ADC 功能管脚添加 0.1uF 电容;

-

2*8 bit DAC,只能分配到: GPIO25 和 GPIO26

-

数字输出管脚驱动强度有四挡可配置:

- 0: 5mA

- 1: 10mA

- 2: 20mA(默认)

- 3: 40mA

2.1 VDD_SDIO:

- VDD_SDIO 最大输出电流为 40mA。

- VDD_SDIO 为 1.8V 输出时,电压范围在 1.65V ~ 2.0V,需靠近其管脚添加 2K//4.7uF 电路。

- VDD_SDIO 为 3.3V 输出时,其由 VDD3P3_RTC 经过 6R 电阻供电,故电压略低于 VDD3P3_RTC。需靠近其管脚添加 1uF 电容。

2.2 VDD3P3(Pin3&Pin4):

- 添加 LC 滤波电路,L 额定电流需在 500mA 及以上

2.3 射频 RF:

- ESP32(6x6) 和 (5x5) RF 管脚输出阻抗分别为 30+j10 和 35+j10,设计时需添加 π 型匹配网络,推荐 CLC 结构;

- RF trace 需做 50R 阻抗管控;

2.4 UART:

- 靠近 U0TXD 串联 499R 电阻用于抑制 80MHz 谐波;

3. 硬件设计

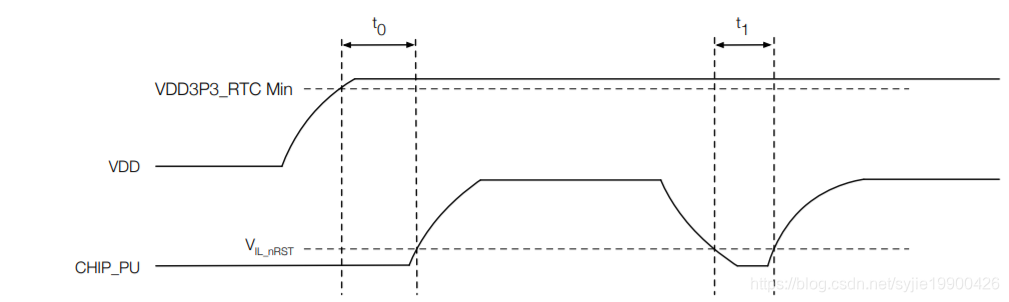

3.1 上电、复位时序:

- VDD3P3_RTC Min: 2.3V

- VIL_nRST: 0.6V(max)

- t0: CHIP_PU 管脚上电晚于系统电源 3.3V 上电的延时时间,最小值为 50us

- t1: CHIP_PU 电平低于 VIL_nRST 的时间, 最小值为 50us

3.2 Strapping 管脚:

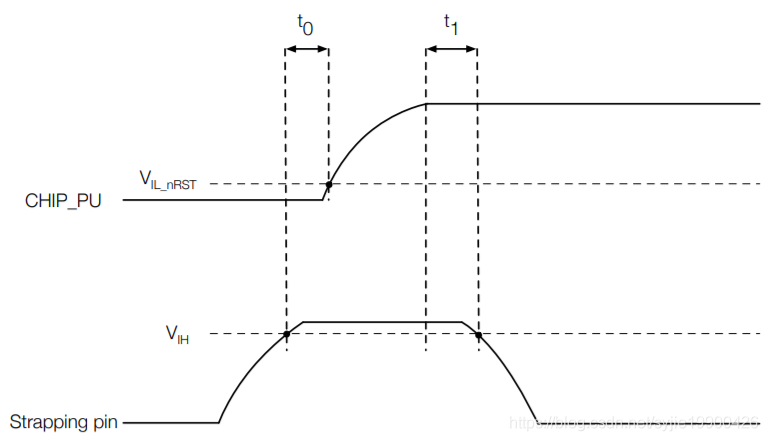

CHIP_PU 与 strapping 管脚的建立和保持时间关系:

- VIH: 高电平输入电压, 0.75xVDDIO(I/O 供电电源) < VIH < VDDIO+0.3

- t0: CHIP_PU 上电前的建立时间,最小值 0ms

- t1: CHIP_PU 上电后的保持时间, 最小值 1ms

ESP32 共有 5 个 Strapping Pins: GPIO0、GPIO2、GPIO5、GPIO12、GPIO15。

内置 LDO(VDD_SDIO)电压:

| 管脚 | 默认 | 3.3V | 1.8V |

|---|---|---|---|

| GPIO12 | 下拉 | 0 | 1 |

系统启动模式:

| 管脚 | 默认 | SPI启动模式 | 下载启动模式 |

|---|---|---|---|

| GPIO0 | 上拉 | 1 | 0 |

| GPIO2 | 下拉 | 无关项 | 0 |

系统启动过程中,控制 U0TXD 打印:

| 管脚 | 默认 | U0TXD 正常打印 | U0TXD 上电不打印 |

|---|---|---|---|

| GPIO15 | 上拉 | 1 | 0 |

SDIO 从机信号输入输出时序:

| 管脚 | 默认 | 下降沿采样,下降沿输出 | 下降沿采样,上升沿输出 | 上升沿采样,下降沿输出 | 上升沿采样,上升沿输出 |

|---|---|---|---|---|---|

| GPIO15 | 上拉 | 0 | 0 | 1 | 1 |

| GPIO5 | 上拉 | 0 | 1 | 0 | 1 |

- “VDD_SDIO” 和 “SDIO 从机信号输入输出时序” 可在上电后,通过寄存器修改其配置

- ESP32-D2WD 内置 flash 工作电压为 1.8V,上电时需将 GPIO12 拉高

4. 设计注意事项:

4.1 避免将 ESP 的 strapping pins 与外设的输出管脚(即,对 ESP 为输入)连接:外设的输出管脚可能在上电时拉住 ESP strapping pins 的状态,影响上电逻辑。