关于STM32F407芯片结构的个人认知

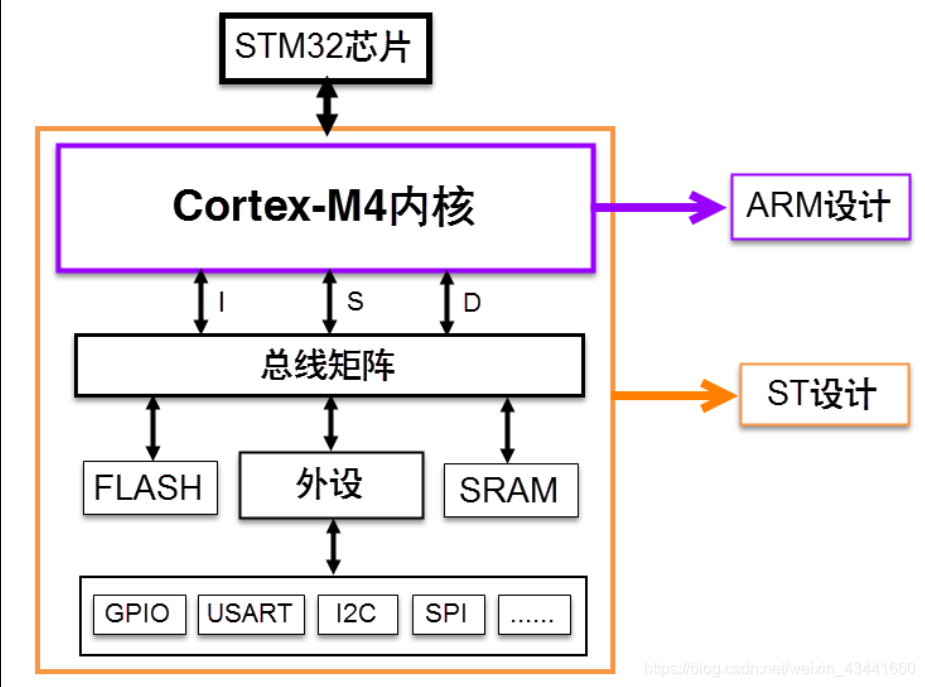

1.芯片内部结构(不深究)*

内核就相当于我们电脑中的CPU,它通过总线矩阵与Flash,SRAM,等相连。而FLASH, RAM 和片上外设,这些功能部件共同排列在一个 4GB 的地址空间内(也就是存储器),我们在编程的时候,操作的也正是这些功能部件。

那么我们就会不禁想到,存储器是怎么给Flash,SRAM分配空间的呢?

存储器映射

存储器本身不具有地址信息,它的地址是由芯片厂商或用户分配,给存储器分配地址的过程就称为存储器映射

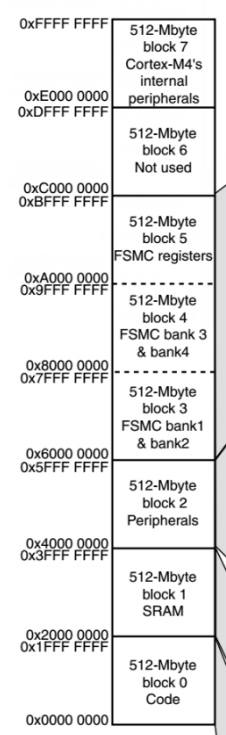

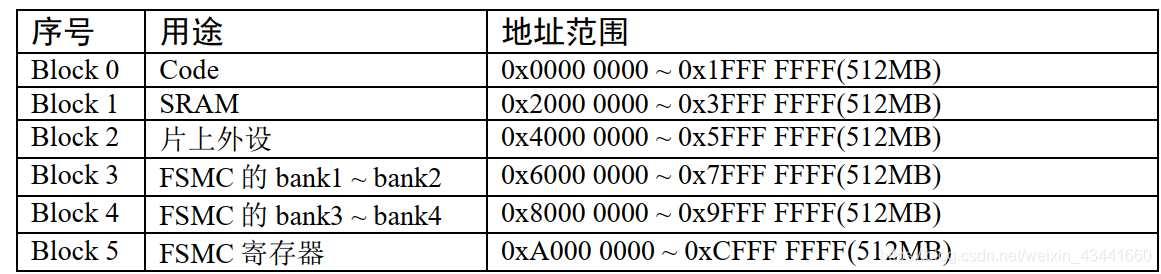

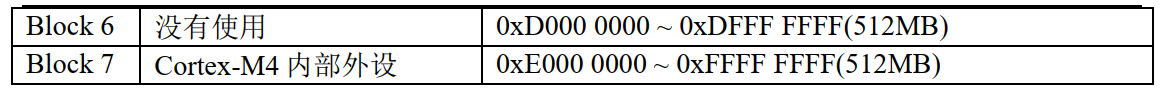

在这 4GB 的地址空间中, ARM 已经粗线条的平均分成了 8 个块,每块 512MB

其中有三个块是我们要重视的,就是Block0,Block1,Block2,也就是我们上面所谈到的Flash,SRAM和外设的所在块,可见它们分在不同的块中。

Flash(也就是我们代码存储的地方)在Block0中,地址为0x0800 0000 ~ 0x080F FFFF (1MB),至于Block0中其它存储区域是什么,我们不必深究。

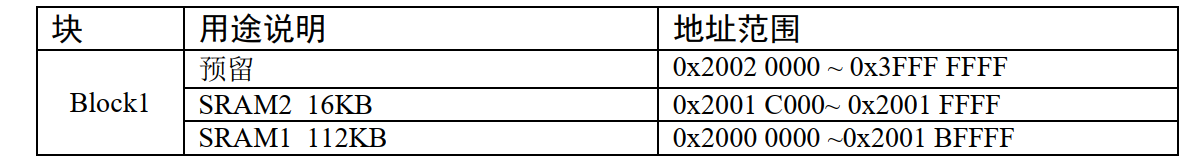

而Block1的地址分配情况为

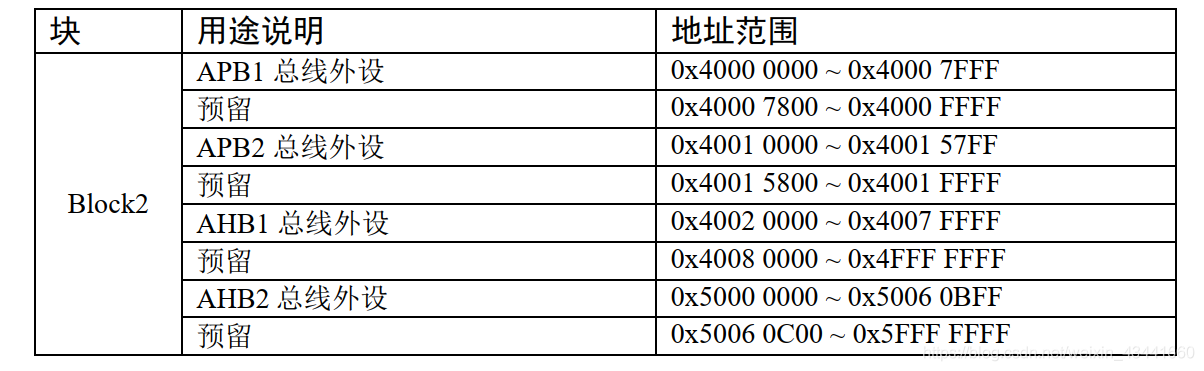

Block2 用于设计片内的外设,根据外设的总线速度不同, Block2 被分成了 APB 和 AHB

两部分,其中 APB 又被分为 APB1 和 APB2, AHB 分为 AHB1 和 AHB2

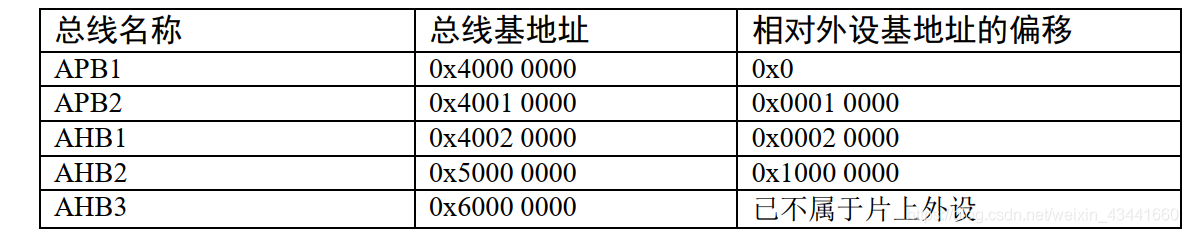

在存储器 Block2 这块区域,设计的是片上外设,需要它们以四个字节为一个单元,共32bit,每一个单元对应不同的功能,当我们控制这些单元时就可以驱动外设工作,片上外设区分为四条总线,根据外设速度的不同,不同总线挂载着不同的外设, APB挂载低速外设, AHB 挂载高速外设。相应总线的最低地址我们称为该总线的基地址,总线基地址也是挂载在该总线上的首个外设的地址。其中 APB1 总线的地址最低,片上外设从这里开始,也叫外设基地址。

其中因为APB1外设是Block2首条总线,所以它的地址也是总线基地址,相对基地址的偏移也是0

然后别的外设又怎么分配到这四条总线上呢?

在每条总线地址范围内,分配着不同的外设,根据不同外设所需要的速度挂载在不同的总线上,例如GPIO外设挂载在AHB1总线。

那么外设挂载在总线后,它的地址范围内,又分布着什么呢?

答案就是寄存器 (我们可以根据每个单元功能的不同,以功能为名给这个内存单元取一个别名,这个别名就是我们经常说的寄存器,这个给已经分配好地址的有特定功能的内存单元取别名的过程就叫寄存器映射)

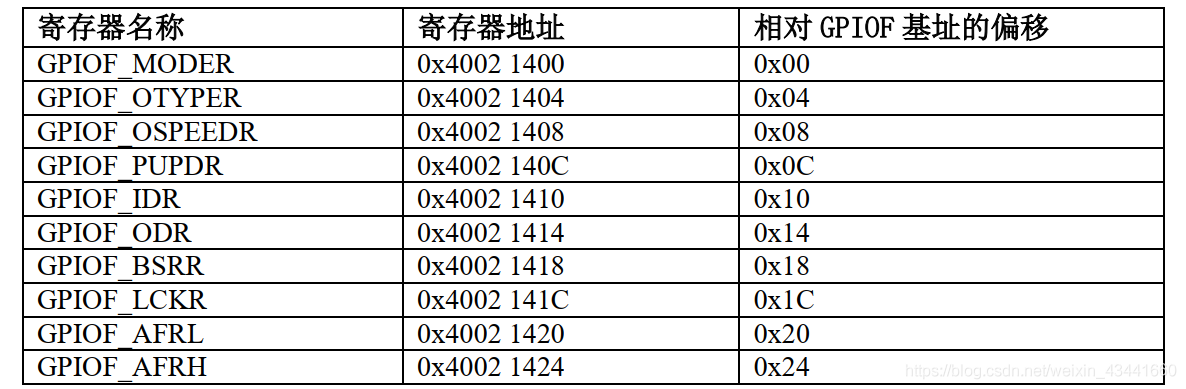

以GPIOF为例,GPIOF的地址为0x4002 1400 ~ 0x4002 17FF

在这个地址范围内有分布着控制这个外设的寄存器

(GPIO 有很多个寄存器,每一个都有特定的功能。每个寄存器为 32bit,占四个字节,在该外设的基地址上按照顺序排列,寄存器的位置都以相对该外设基地址的偏移地址来描述。)

寄存器功能就是控制这个外设的状态,例如高电平还是低电平,开漏输出还是推挽输出等等,每个寄存器有着它们独特的功能。

那么我们又会想到,那我们控制外设还要先找到它的地址,然后再找到要使用的那个寄存器的地址,那不是很麻烦吗?

这就需要我们用c语言对寄存器进行封装了

这个下次我们再详谈,本次只是说说我对芯片结构的个人认知,有些地方可能不够严谨写得不好,望多多包涵,本人大二学生,第一次写技术博客。

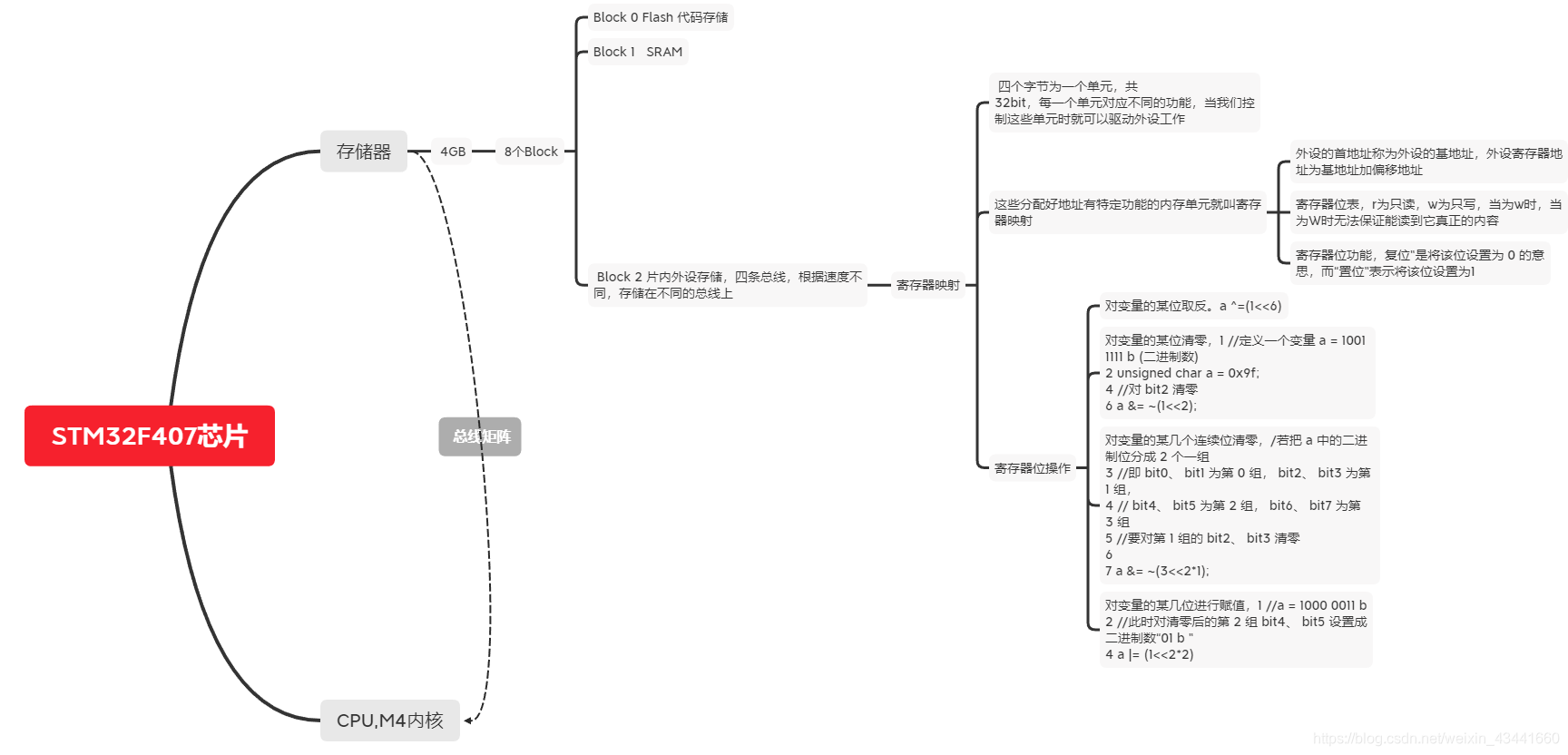

下面是我的思维导图