本文主要讲解演示下如何设计 底层VHDL语言设计,顶层原理图设计的混合输入方式

基于设计平台:Quartus II 13.1

基于设计课题:0-9999加法计数器的设计,采用混合输入方式

底层VHDL语言完成十进制计数器

1.创建工程文件,在工程文件下新建文件等编译环境的搭建在这里就不过多累赘讲述

2.底层VHDL语言设计十进制计数器代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

--声明程序包

entity cnt10 is

port (clk,clr,ena: in std_logic;

cq: out std_logic_vector(3 downto 0);

co: out std_logic);

end cnt10;

--声明实体

architecture bhv of cnt10 is

signal cq1: std_logic_vector(3 downto 0);

--定义保存计数值的信号cq1

begin

process(clk,clr,ena) is

--计数控制进程

begin

if clr = '1' then cq1<="0000";

--计数器异步复位

elsif clk'event and clk = '1' then

--检测时钟上升沿

if ena = '1' then

--检测是否允许计数(同步使能)

if cq1 = "1001" then

cq1<="0000";

--等于9,计数值清零

else

cq1<=cq1+'1';

--允许计数

end if;

end if;

end if;

end process;

process(clk,cq1) is

--进位控制进程

begin

if clk'event and clk = '1' then

if cq1 < "1001" then

co<='0';

else

co<='1';

--计数大于9,输出进位信号

end if;

end if;

end process;

cq<=cq1;

--将计数的中间结果cq1,传送到计数器cnt10的输出端口cq

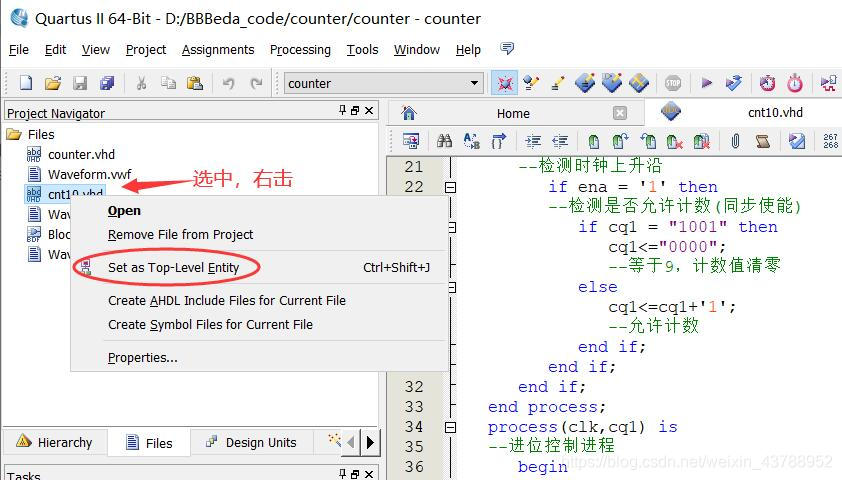

end bhv;3.编译程序,检查是否报错;无误后,如果工程下面存在多个文件,将其针对使用的文件进行置顶操作,如下图所示:

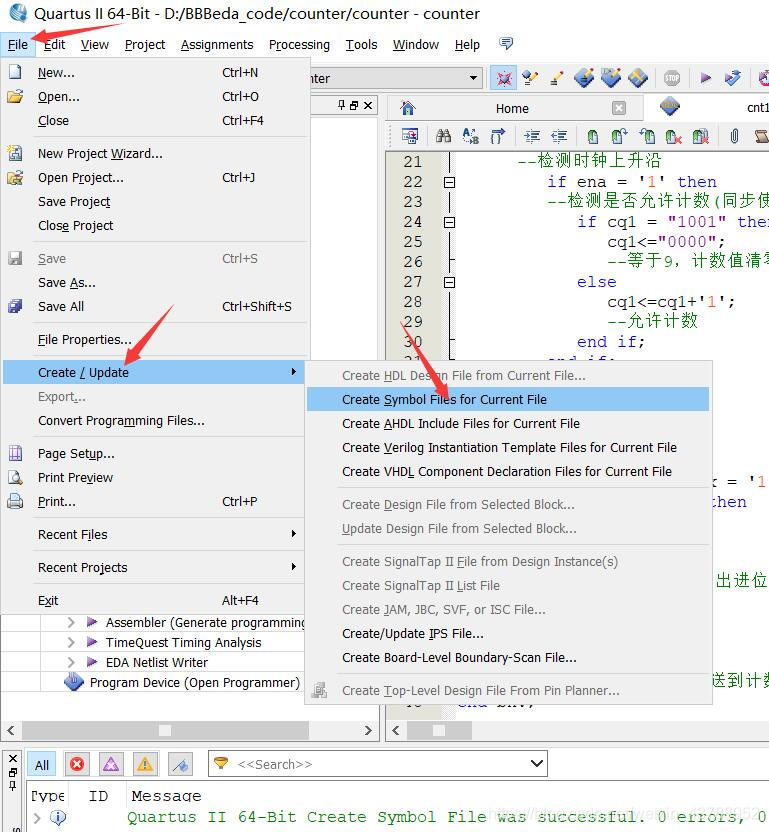

4.接下来进行将底层VHDL语言设计的器件导出符号文件,如下图:

运行无误即成功

顶层原理图设计

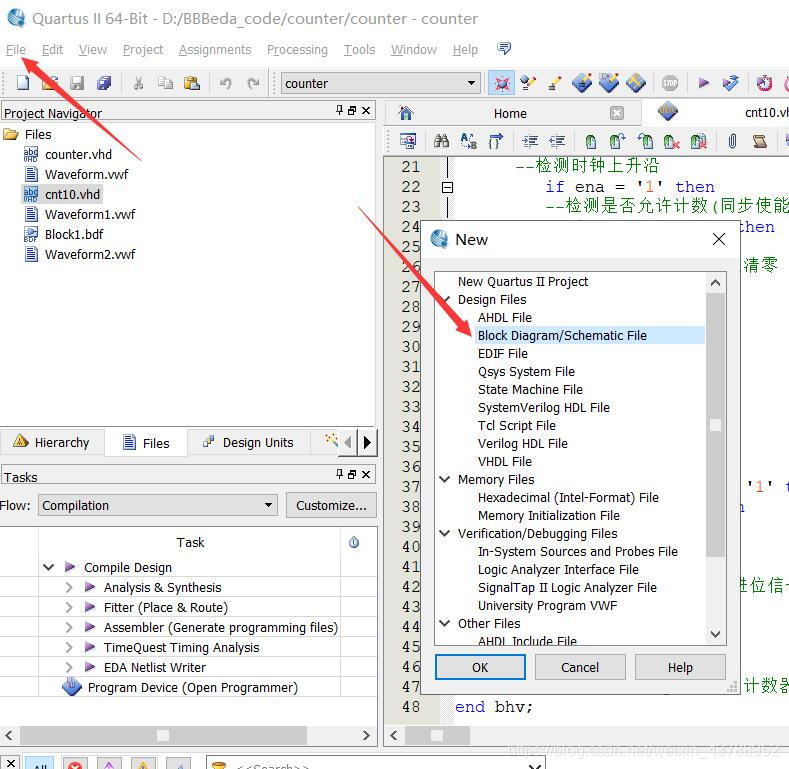

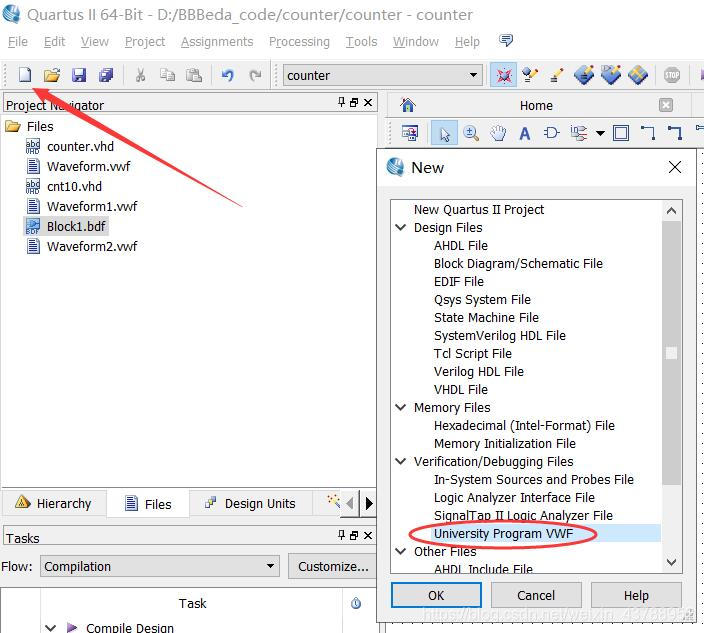

5.在工程下面新建原理图文件,如下图所示:

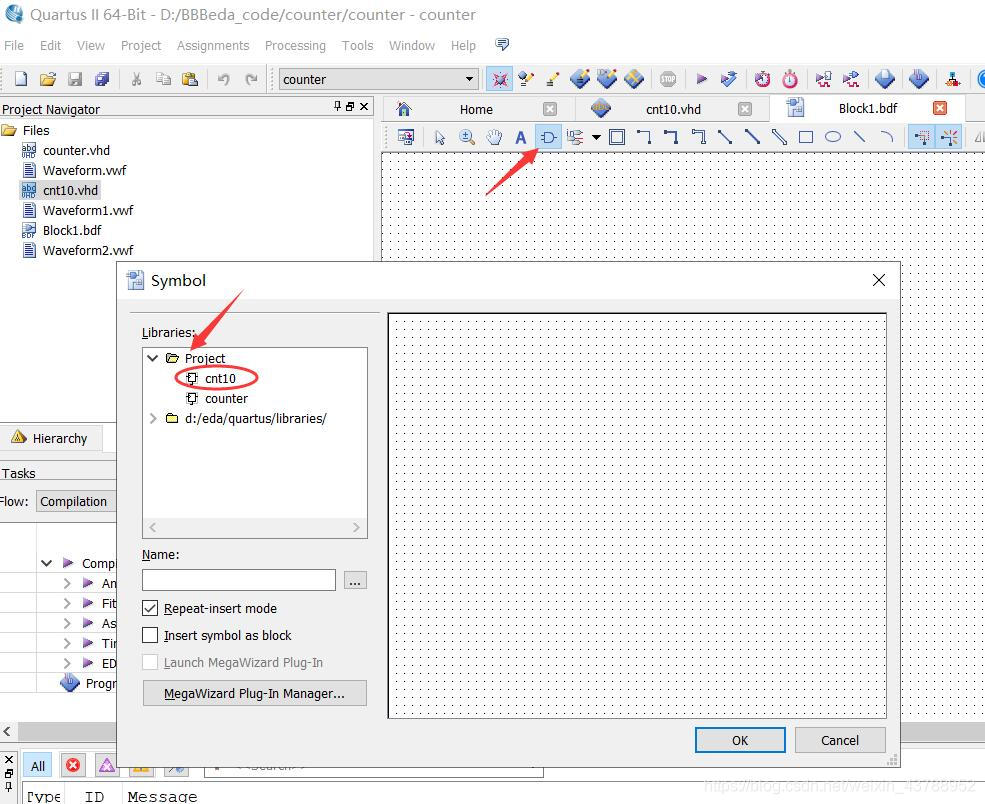

6.放置底层语言设计导出的符号文件,如下图所示:

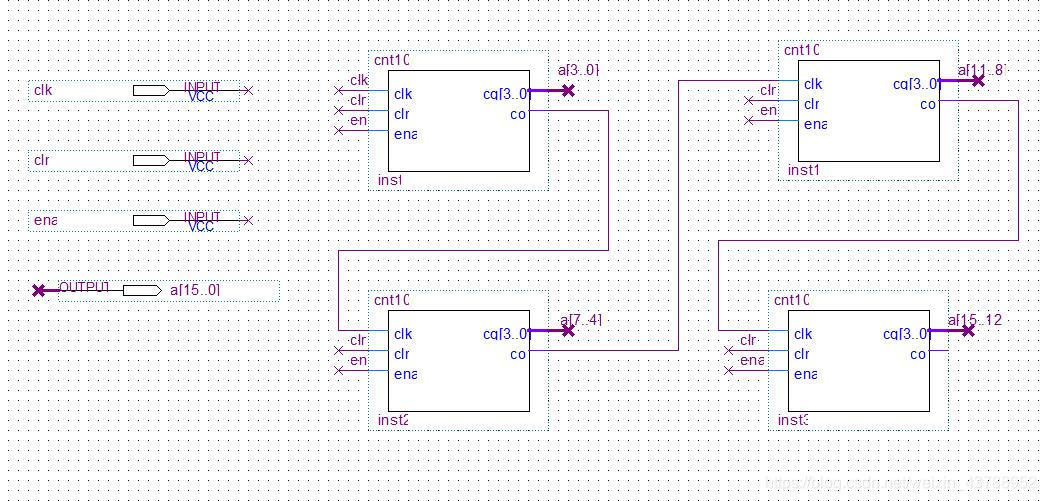

7.然后,利用四个十进制计数器搭建成范围是0~9999的加法计数器,如下图所示:

可以用导线将端口对应连接,如果图方便,简洁,也可以隔空连接,如图所示,在端口处连出一端导线,不连接另外一端,即形成叉号,然后将对应端口也连出一端导线,不连接另外一端,形成叉号,将对应两端的导线命成相同的名字,即为默认连接。

需要注意的是,输出端口要有总线接出,在命名总线时,格式为a[0…3],写成[0…3]是错误的

8.设计好原理图后,运行检查是否报错,如下图:

注意这里运行,需要将原理图文件同样进行置顶操作,操作如之前步骤一样。

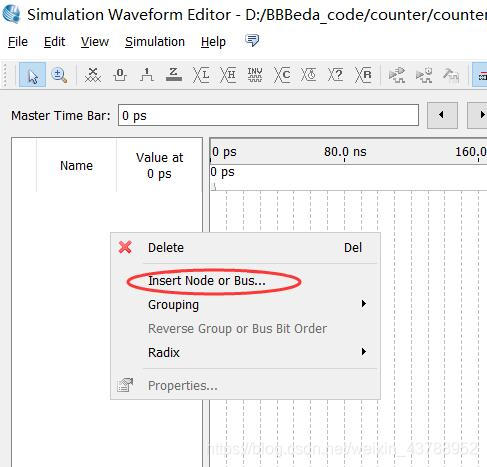

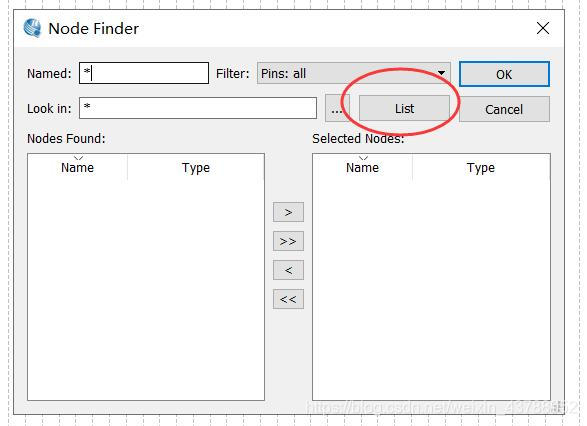

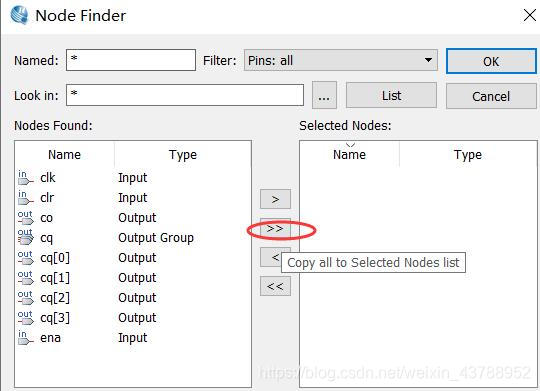

9.经过以上操作,顶层原理图,底层语言文本设计就完成了,现在进行仿真操作,检查是否实现功能,如图下:

新建仿真文件

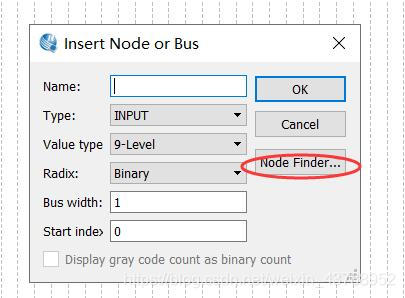

依次搭建仿真环境,鼠标右击空白处

随后依次点击ok,ok即可

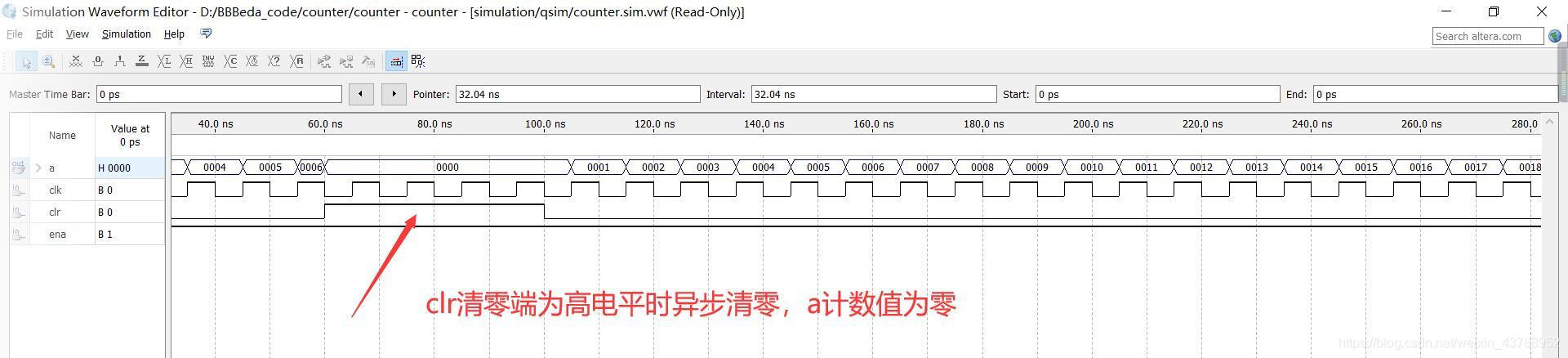

10.配置仿真条件,验证仿真结果

可以进行0~9999十进制计数,功能实现