1. 硬件平台介绍

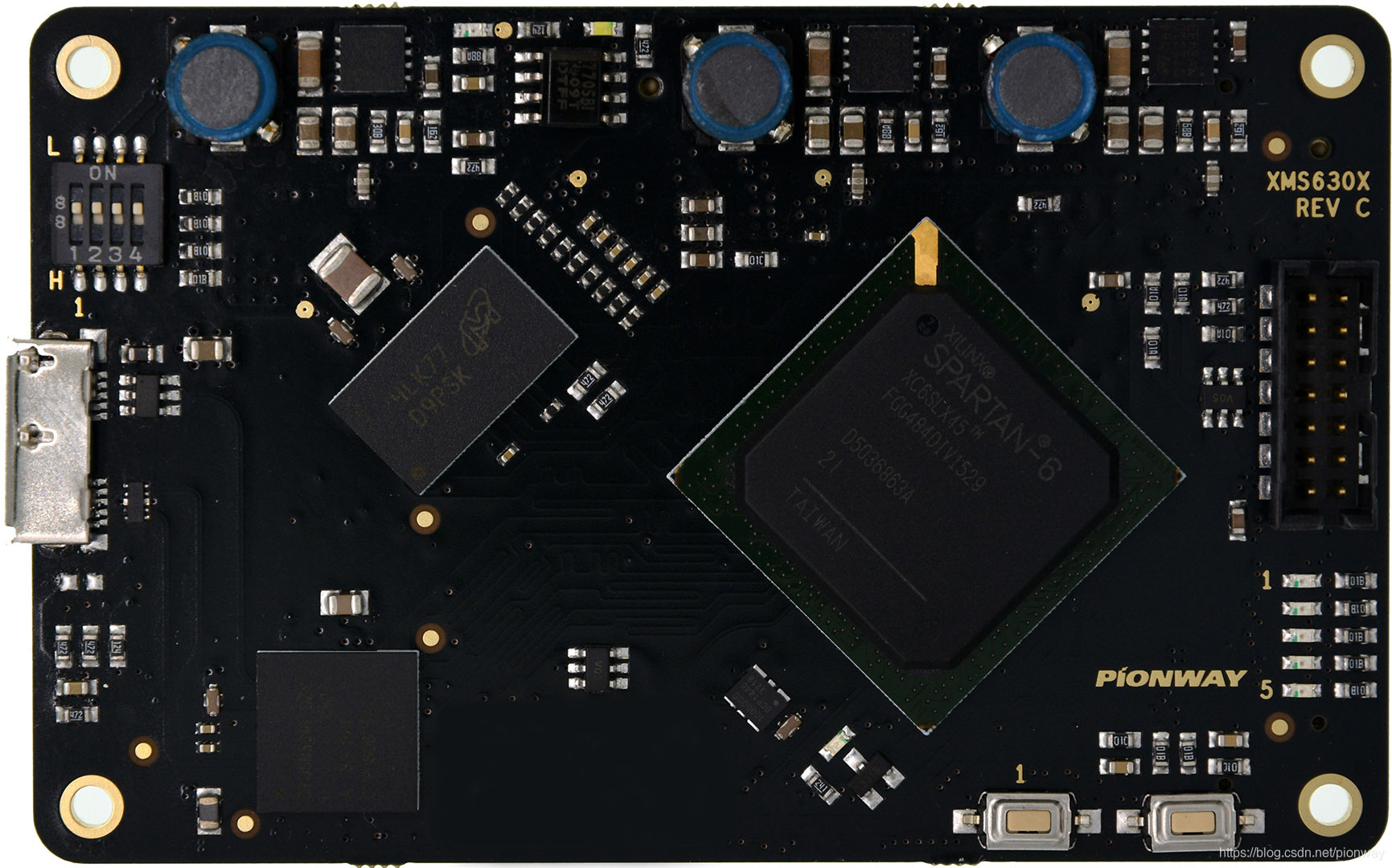

TT推荐的USB硬件快速开发方法是直接使用成熟的产品级的FPGA USB模块作为基础来开发。模块已经完成了最复杂及风险最高的硬件开发部分,用户只需要基于具体应用设计一个扩展板即可完成整体的产品级设计。这里以Pionway的XMS6301 FPGA USB模块来做示例说明。

XMS6301是一款深受市场欢迎的FPGA USB3.0产品级模块,用料扎实,做工优良,在高速信号采集、图像/视频采集及处理、数字通信等领域应用广泛。

XMS6301按照工业级温度标准设计,采用芯片级的电源输入保护方案,10层板叠层设计,板上所有的传输线全部实现阻抗控制及等长匹配,电磁兼容能力良好。大小仅为标准银行卡尺寸(85.5mm×54mm),可以方便的集成在各种小型的电子设备内部。

XMS6301中心的Spartan-6 FPGA为模块的主处理器部分,内置丰富的逻辑资源,可用于实现各种复杂的数字信号处理功能。板载2Gibit的DDR3 SDRAM连接到了FPGA内置的硬核存储器控制器上,最大读写带宽10.672Gbps,为处理器的处理流程提供了大容量的数据缓存支持。板载高精度LVDS差分低抖动硅晶振时钟源,降低FPGA的时序约束,增强处理器的运行可靠性。

| XMS6301型号 | XMS6301-LX45I | XMS6301-LX150I |

| Slice数量 | 6,822 | 23,038 |

| D触发器数量 | 54,576 | 184,304 |

| 分布式RAM大小 | 401Kib | 1,355Kib |

| Block RAM大小 | 2,088Kib | 4,824 Kib |

| DSP Slice数量 | 58 | 180 |

| 时钟管理模块(CMT)数量 | 4 | 6 |

| 项目 | 数值 |

| Integrated Phase Jitter(JPH) | 2ps |

| Period Jitter RMS(JPER) | 2.5ps |

| Overall Freq.Stability | ±25ppm |

2. 扩展板设计

扩展板用来与模块通过板对板连接器相互连接,为模块提供电源供给,并将模块的I/O导出到外部来使用。

在设计过程中,推荐的电子元器件购买渠道是立创商城、Digi-Key、Mouser等自营元器件交易网站。

2.1 模块引脚网络标识说明

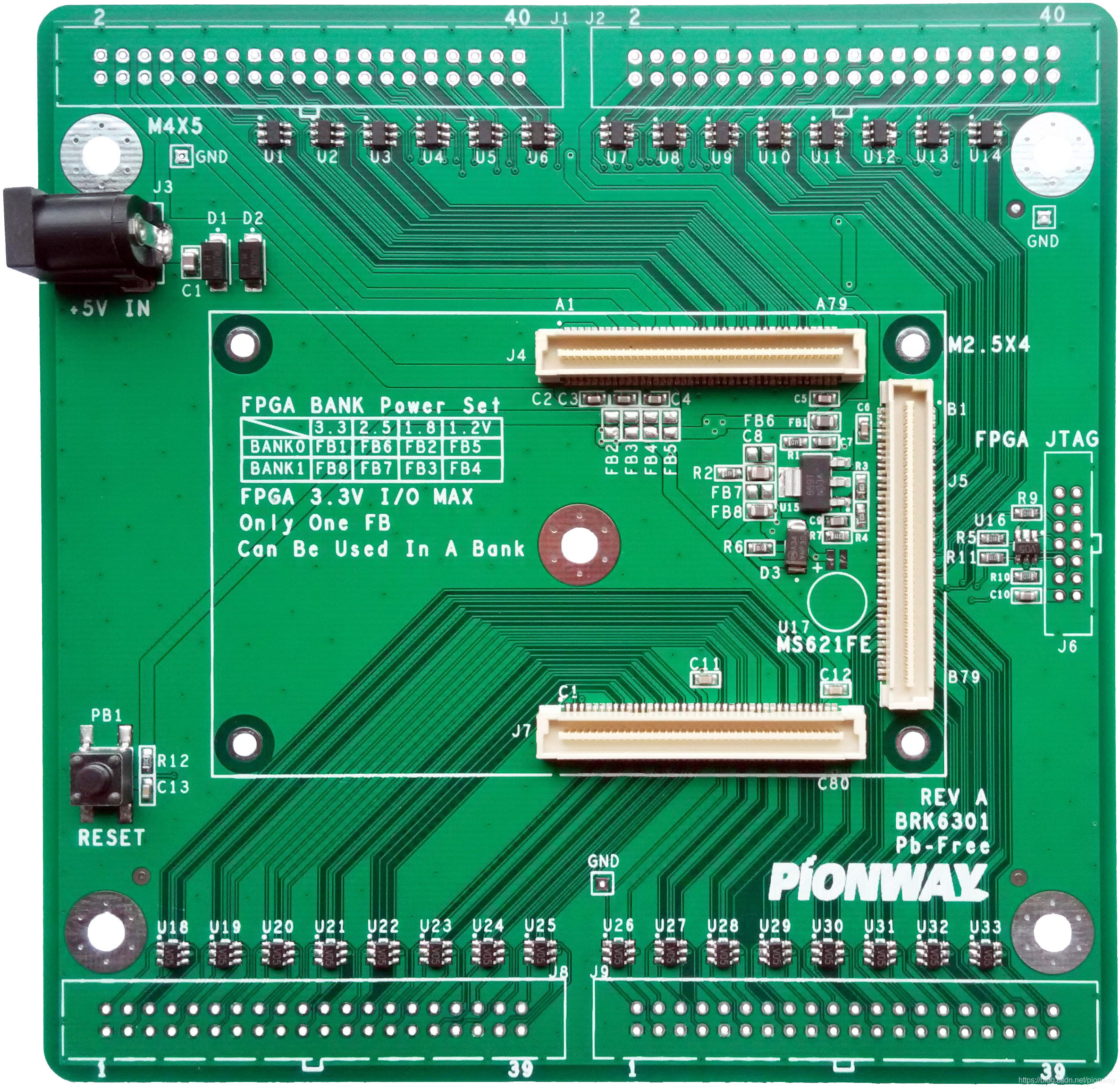

XMS6301模块对外有3个80pin的0.8mm间距板对板连接器,标号分别为A、B、C。总共240pin引脚包含了模块的供电输入输出、I/O数据传输及特殊功能的连接。

| 序号 | 功能描述 | 网络标识 | I/O引脚数量 |

| 1 | 主电源输入 | VCC5VD | 10 |

| 2 | FPGA BANK 0 I/O电压输入 | FPGA_VCCO0_IN |

4 |

| 3 | FPGA BANK 0 I/O参考电压输入 在不需要的情况下可以用作I/O |

L1N_VREF_0、L8N_VREF_0、 L38N_VREF_0、L62N_VREF_0 |

4 (4双功能) |

| 4 | FPGA BANK 1 I/O电压输入 | FPGA_VCCO1_IN |

4 |

| 5 | FPGA BANK 1 I/O参考电压输入 在不需要的情况下可以用作I/O |

L1N_VREF_1、L28N_VREF_1、L53N_VREF_1 |

3 (3双功能) |

| 6 | 数字电源输出 | VCC1V2D、VCC1V8D、VCC3V3D | 18 |

| 7 | 数字地 | DGND | 81 |

| 8 | FPGA BANK 0 I/O | L2P_0、L3N_0... | 44 |

| 9 | FPGA BANK 1 I/O | L1P_1、L1N_VREF_1 | 72 (3双功能) |

| 10 | 复位输入/输出 | SYS_RST_IN_N(复位输入)、FX3_RESET_N(漏极开路复位输出) | 2 |

| 11 | JTAG接口 | CABLE_TDI、FPGA_TDO、 CABLE_TCK、CABLE_TMS |

4 |

| 12 | 电池电源输入 | VBAT | 1 |

2.2 扩展板的电源设计

模块的电源电路包含电源输入和电源输出部分,电源输入有两路,一路是USB Cable(0.5-0.9A),另一路是通过通过板对板连接器(3-4A),其中板对板连接器的供电内部优先级更高。

由于USB Cable的输入电流能力有限,一般仅作为简单的功能演示使用,在产品级的使用场景中建议仅使用板对板连接器来为模块供电,并将XMS6301模块背面的USBP开关拨到DIS(出厂默认)来关断USB的供电使能。

2.2.1 模块的主电源供电设计

XMS6301的输入额定电压为+5V,短时间最高可耐受到+12V,最低输入电压不应低于+4.6V,最大输入电流为4.17A。使用过程中,可以根据如FPGA处理算法的规模、外部驱动负载的情况等实际应用需求来搭建足够功率的DC/DC电路来驱动。

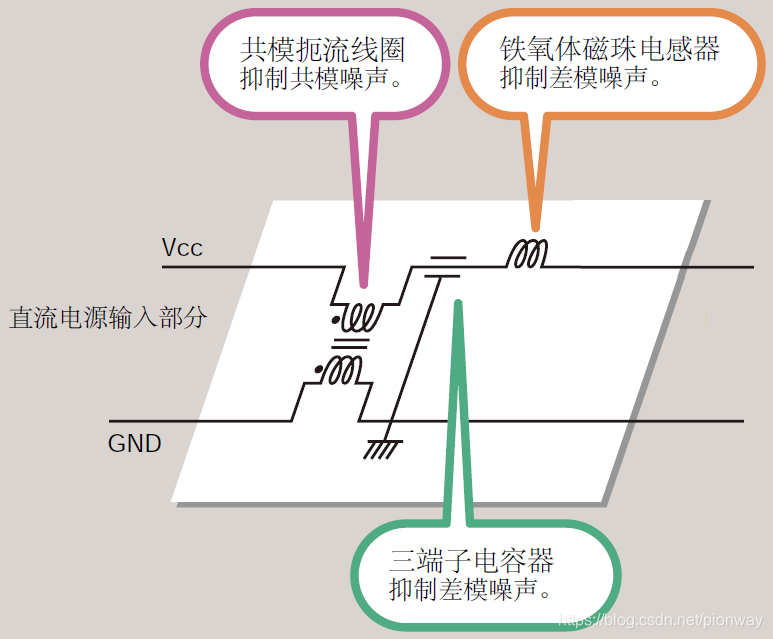

DC/DC电路的最大输出电流、电感的电感量、饱和电流指标要足够,并且建议在DC/DC的电源输出端串联大载流能力的磁珠或者EMIFIL对电源滤波后再送入模块。如果板上有敏感的模拟信号部分,需要远离DC/DC电路或对其加做电磁屏蔽处理。

| 序号 |

调节器类型 |

电路特点 | 价格 | 面积 | 参考芯片/模块型号 |

| 1 |

Module |

内置开关管(MOSFET)和电感,体积最小,价格较高,使用最方便,原包装拆封过久焊接前必须烘烤! |

差别较大 | 最小 | 3.0A:TPS82130SILR 4.0A:EN2340QI 6.0A:LTM8033双模块并联 |

| 2 |

Converter |

内置开关管,需要外接电感, 性价比最高,使用的最多 |

较低 | 适中 | 3.0A:TPS54329DDAR 4.0A:TPS56428DDAR 5.0A:TPS56528DDAR |

| 3 | Controller | 需要外接开关管和电感, 面积最大,使用相对少 |

较高 | 较大 |

| 类型 | 序号 | 型号 | 电容量/ 100MHz 阻抗值 |

耐压 | 最大通过电流 | 封装 | 生产 厂商 |

特点及作用 |

适用电路 |

| 共模扼流线圈 | 1 | ACM70V-701-2PL-TL00 | 701Ω |

80V | 4A | 7.0X 6.0mm |

TDK | 对长导线 产生的 共模噪声 抑制能力强 |

电源输入的 开始位置 |

| EMIFIL滤波器 | 2 | NFM18PS105D0J3D | 1μF | 6.3V | 2A | 0603 | Murata | 超低的ESL 滤除高频噪声 效果极佳 |

高噪声辐射 高阻抗线路 |

| 3 | NFM18PC225B1A3D | 2.2μF | 10V | 4A | 0603 | Murata | |||

| 4 | NFM41PC155B1H3L | 1.5μF | 50V | 6A | 1806 | Murata | |||

| 铁氧体磁珠 | 5 | BLM21PG221SN1D | 220Ω | N/A | 2A | 0805 | Murata | 抑制高频噪声 无需对地连接 |

低噪声辐射 低阻抗线路 |

| 6 | MPZ1608S331ATA00 | 330Ω | N/A | 1.7A | 0603 | TDK | |||

| 7 | MPZ2012S601AT000 | 600Ω | N/A | 2A | 0805 | TDK |

2.2.2 模块I/O所使用的VCCO和VREF供电设计

XMS6301模块上的I/O连接到了FPGA的Bank0和Bank1,每个Bank的VCCO和VREF输入电压决定了其分别所能支持的电平标准。

VCCO在所有情况下都必须要全部连接外部电源输入,其输入电流取决于输出I/O的数量和输出负载,一般不小于500mA。并且需要在其他板对板连接器的引脚附近放置10-100nF的去耦电容(阵列)来防止噪声耦合。

VREF则根据实际要是用的电平标准来决定是否输入电压,如没有用到不用可作为FPGA的I/O来使用。如果需要使用,则相应BANK的VREF必须全部供电,VREF所需要的输入电流不大,但对电源噪声敏感,建议外接LDO或者经过EMIFIL滤波后对其供电,并且需要在其他板对板连接器的引脚附近放置10-100nF的去耦电容(阵列)来防止噪声耦合。

| 序号 | VCCO电压 | VREF | 单端电平标准 |

| 1 | 3.3V | 不用供电,可做I/O使用 |

LVTTL、LVCMOS33、PCI33_3、PCI66_3、SDIO |

| 1.5V低噪声+MLCC | SSTL3_I、SSTL3_II | ||

| 2 | 3.0V | 不用供电,可做I/O使用 | I2C、SMBUS |

| 3 | 2.5V | 不用供电,可做I/O使用 | LVCMOS25 |

| 1.25V低噪声+MLCC | SSTL2_I、SSTL2_II | ||

| 4 | 1.8V | 不用供电,可做I/O使用 | LVCMOS18、MOBILE_DDR、LVCMOS18_JEDEC |

| 0.9V低噪声+MLCC | SSTL18_I、SSTL18_II | ||

| 5 | 1.5V | 不用供电,可做I/O使用 | LVCMOS15、LVCMOS15_JEDEC |

| 0.75V低噪声+MLCC | SSTL15_II | ||

| 6 | 1.2V | 不用供电,可做I/O使用 | LVCMOS12、LVCMOS12_JEDEC |

| 序号 | VCCO电压 | VREF电压 | 差分电平标准 |

| 1 | 3.3V | 不用供电, 可做I/O使用 |

LVDS_33、MINI_LVDS_33、RSDS_33、 PPDS_33、DIFF_SSTL3_I、DIFF_SSTL3_II |

| 2 | 2.5V | LVDS_25、BLVDS_25、MINI_LVDS_25、RSDS_25、 PPDS_25、DISPLAY_PORT、DIFF_SSTL2_I、DIFF_SSTL2_II |

|

| 3 | 1.8V | DIFF_MOBILE_DDR、DIFF_HSTL_I_18、DIFF_HSTL_II_18、 DIFF_HSTL_III_18、DIFF_SSTL18_I、DIFF_SSTL18_II |

|

| 4 | 1.5V | DIFF_HSTL_I、DIFF_HSTL_II、DIFF_HSTL_III、IFF_SSTL15_II |

2.2.3 模块的电源输出

XMS6301模块还将自身的1.2V、1.8V、3.3V三个数字电源输出(可以不使用),其中1.8V和3.3V的最大输出能力为1A,1.2V的最大输出能力为500mA,可以为小功率的数字电路外设提供电源,如要给模拟电路供电需要先经过LDO转换再经过EMIFIL或磁珠滤波后使用。XMS6301的所有电源输出即使没有使用,也需要在旁边并联若干10-100nF MLCC去耦电容以防止连接器的天线效应耦合噪声。

2.3 扩展板的I/O设计

XMS6301的3个板对板连接器上的I/O大部分连接到了FPGA的数据I/O引脚上,负责FPGA的数据通信功能。还有一小部分I/O连接到了模块的复位电路、FPGA的配置电路部分,负责模块的功能管理部分。

2.3.1 扩展板的FPGA I/O设计

XMS6301的I/O总共有116根,分布在FPGA的BANK0和BANK1,包括差分和单端传输线。

差分传输线对总共有21对(48根),差分特性阻抗100Ω,所有的21对差分对之间的传输线长度误差<3mil,连接在BANK0有16对(双向LVDS),连接在BANK1有5对(LVDS只能输出),这21对差分对也可以作为单端信号传输线,但如果用来传输高速信号,需要考虑传输线间的串扰(可以间隔使用)。

非差分I/O数量总共有74根,只能用于单端信号传输,特性阻抗50Ω,116根所有的I/O的传输线长度误差<150mil。

| 标号 | 总I/O数量 |

差分对数量 |

差分对名称 | 非差分I/O数量 |

GCLK数量 |

其他引脚类型 |

| A | 24 | 9 | L2_0、L3_0、L4_0、L5_0、L6_0、 L7_0、L33_0、L36_0、L37_0、 |

6 | 6 | 5V、1.8V、1.2V、 VCCO0、VREF0、GND |

| B | 48 | 11 | L35_0、L50_0、L51_0、L62_0、 L63_0、L65_0、L66_0、L19_1、 L20_1、L31_1、L71_1 |

26 | 6 | 3.3V、VREF0、 VREF1、GND |

| C | 44 | 1 | L44_1 | 42 | 4 | VCCO1、VREF1、 复位、JTAG、GND |

对于XMS6301,在任何情况下外部设备的I/O最高电压不应超过模块当前的I/O所对应的VCCO,比如假设VCCO0的输入电压设置为1.8V,则L2P_0输入信号的输入电压不应超过1.8V,VCCO1的输入电压设置为2.5V,L1P_1的输入信号的最高电压不应超过2.5V,否则有可能会导致I/O损坏。

对于最高输入电压高于3.3V的电平标准,如TTL、CMOS。需要外接缓冲芯片,如SN74LVC245A、SN74LVC244A,可以将5V的输入转换成2.5V或3.3V的电平标准保护了模块的FPGA I/O引脚。如果所要转换的数字信号频率较高,对转换电路的延迟较为敏感,可以考虑使用CPLD来做接口电平转换功能。

如果扩展板需要将XMS6301的I/O导出到PCB的外部,也建议使用SN74LVC245A、SN74LVC244A来做接口的隔离,并在靠近外部接口处放置ESD保护器件增强静电保护。

2.3.2 扩展板的复位电路设计

XMS6301上电后复位电路会不断监控模块上的VCC1V8D电压轨,当模块内部的VCC1V8D电压轨正常的时候,无复位信号输出。而当各种意外导致模块VCC1V8D电压轨降低到了1.67V以下时,模块内部复位电路会持续输出复位信号,直到VCC1V8D电压持续200ms回到1.67V以上后解除复位信号输出。

用户也可以通过拉低模块的复位信号输入引脚FX3_RESET_N的电平来通知模块强制执行复位操作。

模块的复位输入信号FX3_RESET_N和复位输出信号FX3_RESET_N都为低电平有效,复位输出信号为漏极开路,在内部上拉到了1.8V。

复位输入信号SYS_RST_IN_N在模块内部也做了1.8V的弱上拉,其最高外部输入电压不要超过2.0V。

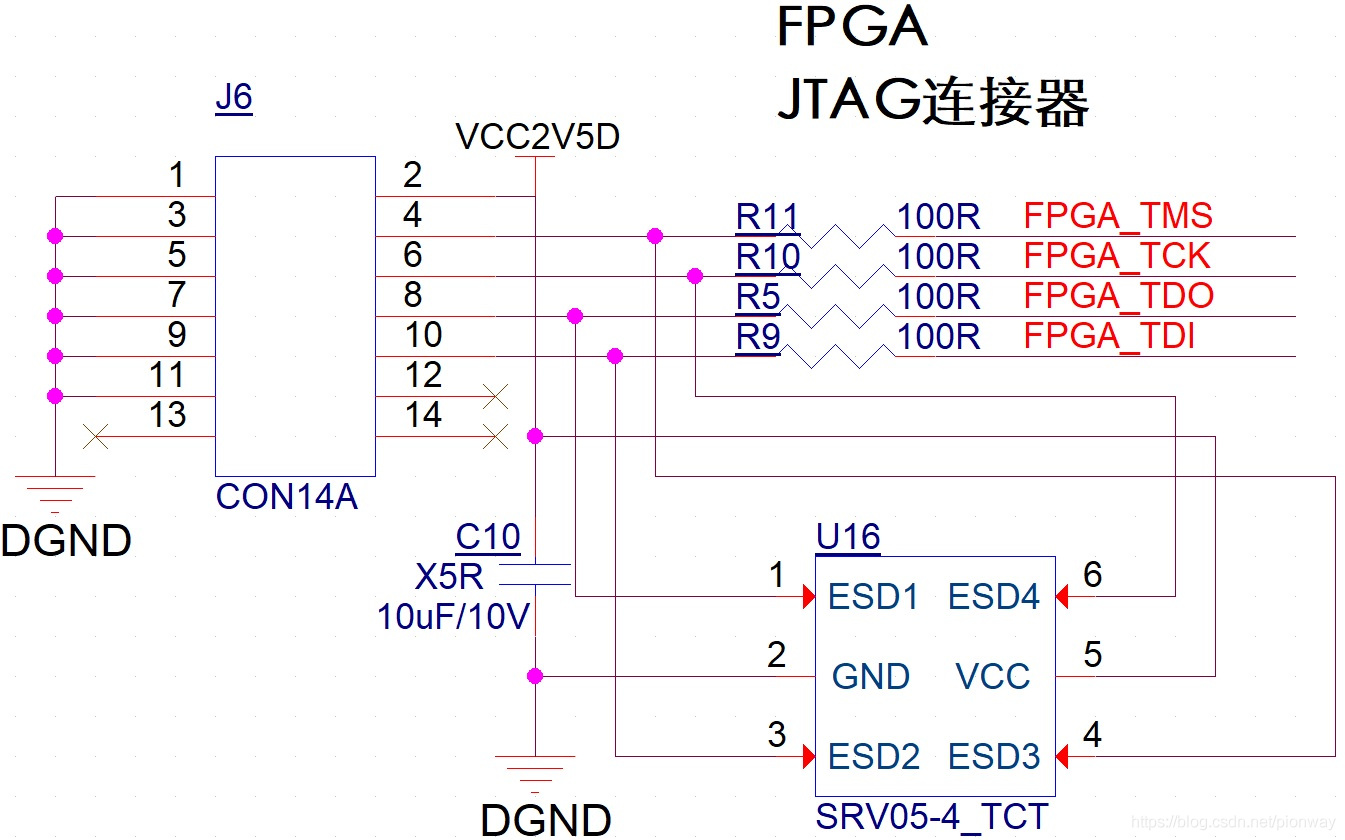

2.3.3 扩展板的配置电路设计

XMS6301将FPGA的JTAG信号引出到了板对板连接器上,用户可以在扩展板上将其引出来实现FPGA的下载及调试工作。

如果需要做外接连接器与Xilinx Platform USB (II)相连接,第二脚的VREF电压需要设置成2.5V来兼容模块上的JTAG电平标准。所有对外的JTAG信号线都需要加ESD保护芯片增加静电保护能力。

| 生产厂商 | 表贴垂直型号 | 通孔垂直型号 | 通孔直角型号 |

| Molex | 87832-1420 | 87831-1450 | 87833-1420 |

| FCI | 98424-G52-14 | 98414-G06-14 | 98464-G61-14 |

| Comm Con Connectors | 2475-14G2 | 2422-14G2 | 2401R-G2-14 |

2.3.4 扩展板的防篡改电路设计

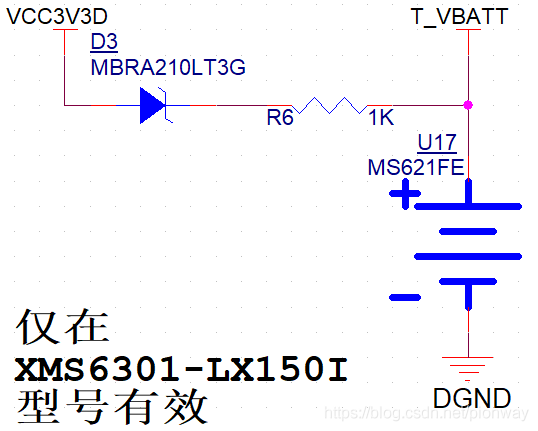

XMS6301的LX150型号支持Xilinx的bit流文件加密功能,如需使用此功能能,需要使用电池来不间断的为板对板连接器上的VBATT引脚提供工作电压,VBATT的工作电压范围是1.0V-3.3V之间,可以在扩展板上放置一个可充电的贴片锂电池。当设备连接电源的时候为其充电,当设备掉电后为VBATT引脚继续提供工作电流。

XMS6301 用户还可以使用FPGA 内部的Device DNA 来实现自定义的加密功能。LX45 与LX150 都支持此

功能。

Device DNA 是FPGA 在生产过程中烧录的57bits 数字序列,每一个芯片的序列都不相同。基本的加密思

路如下:

- 用户在上位机使用JTAG 接口读取FPGA 的Device DNA 序列,然后合并自定义的秘钥key1 一同带入到一个自定义的单向函数中进行不可逆计算,得出结果序列。

- 将结果序列存储到与FPGA 相连接的非易失存储器上。

- 配置FPGA 程序。

- FPGA 内部的解密程序通过DNA_PORT 接口读取自身的Device DNA 序列后合并预定义的秘钥key1 一起送入单向函数进行同样的不可逆算法后得到结果序列。

- FPGA 解密程序读取和他相连的非易失存储器内容后进行比较,如果两者内容相同则验证成功,否则FPGA 程序不执行。

使用此加密方法在硬件上需要在FPGA 上外接一个非易失存储器, 如小容量的EEPROM, 如

AT24C02C‐SSHM‐T,也可以使用更复杂的安全验证存储器,如AT88SC0104CA‐SH、DS28E38Q+U 等芯片。